1.功能测试概述

功能测试是验证器件是否能完成设计所预期的功能。对于复杂的数字集成电路,由于电路功能复杂,其性能不可能直接反映在引脚上,器件质量也不能由输入、输出参数完全反映出来,需要对这些嵌入片内的逻辑电路进行功能测试。

功能测试的基本过程是应用一有序的或随机的数据组合测试图形,以器件规定的速率作用于DUT(被测器件),并将器件的输出与预期数据图形比较,以此判别器件功能是否正常。

为了验证被测器件是否能正确实现所设计的逻辑功能,检测出被测器件中的故障,需生成测试向量或真值表。测试向量和测试时序组成功能测试的核心。执行功能测试时,测试系统给DUT提供输入数据并逐个周期、逐个引脚监测DUT的输出,如果任何引脚输出逻辑状态、电平、时序与期望的不符,则功能测试不通过。

功能测试有静态功能测试和动态功能测试之分。所谓静态功能测试,其测试速率比器件正常工作速度慢得多,主要用于验证真值表功能,发现固定型故障。动态功能测试则以接近或高于器件的工作频率进行测试,其目的是在接近或高于器件实际工作频率的情况下,验证器件的功能和性能,以充分保证器件的质量。两者所采用的测试图形相同,但因工作频率要求不同,所采用的测试仪就不尽相同。显然动态功能测试是一种更全面、更严格的测试。

2.功能测试的原理

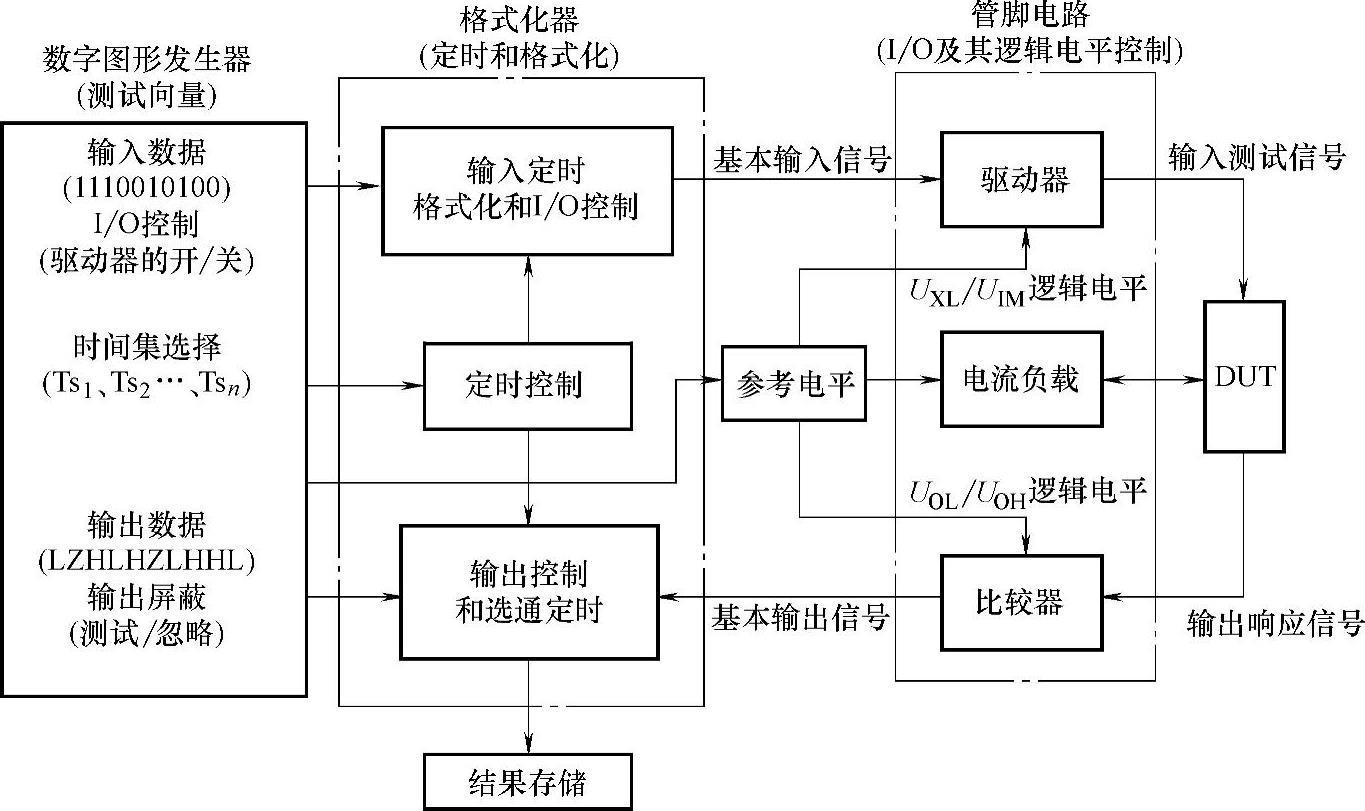

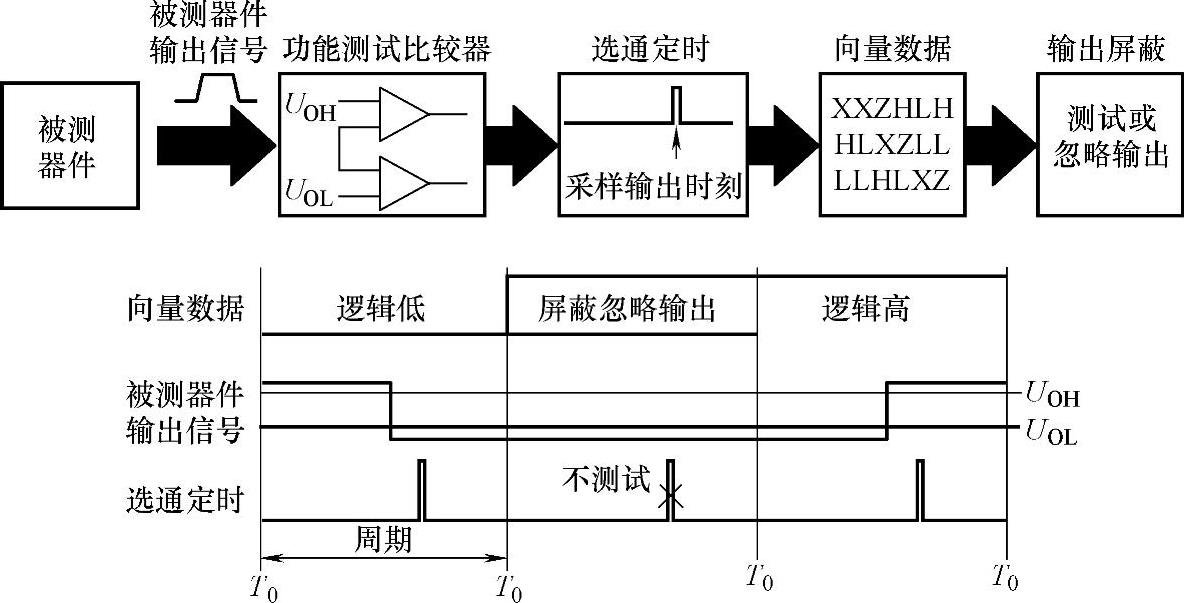

典型的功能测试原理框图如图11-22所示,它包括了三大功能模块:测试向量生成、定时和格式化、输入/输出及其逻辑电平控制等。三大功能模块构成了两个信号通道:DUT的输入(激励)信号产生通道和DUT的输出(响应)信号检测通道。

下面分别介绍三大功能模块和两种信号通道的组成原理。

3.测试向量

测试向量包含的信息如下:

1)测试向量文件包含DUT运行一系列功能的真值表,即包括必须施加到DUT输入端的逻辑状态和期望在输出端出现的逻辑状态。向量数据通常包含如下逻辑状态的字符:

0——驱动输入低电平(逻辑0); 1——驱动输入高电平(逻辑1);

L——输出比较低电平; H——输出比较高电平;

图11-22 功能测试原理框图

Z——输出高阻状态比较电平; X——不关心状态(忽略电平)。

2)向量文件还可能包含一些供测试系统识别的标志。如果DUT拥有双向I/O引脚,向量文件就需要提供I/O切换,一方面需要控制测试系统的输入驱动电路何时打开和关闭;另一方面I/O切换将DUT的某个I/O引脚从输入状态变为输出状态或反之,I/O切换可以发生在任何需要的周期。

3)测试向量可能还含有部分输出引脚的屏蔽信息。屏蔽用于控制一个输出引脚的测试与否:当输出引脚处于已知的逻辑状态时,输出可以被测试;而当输出处于未知的逻辑状态或者在某个条件下不理会它的状态时,它就可以不被测试,这时就可以用“X”来忽略输出引脚上的状态,屏蔽可以对独立的引脚和在独立的周期进行。

4)如果测试系统支持复合时序设置,则向量还可能含有时序设置方面的信息,用于在向量运行时间改变测试时序,举例来说,测试一款典型的RAM时,数据写入和读出的时间不同时,这种情况下,就可能有一套包含写入数据时序的时序设置和另一套包含读出数据时序的时序设置。时序设置可以控制周期的长短、输入信号的时序和格式以及输出采样的时序。

测试向量(测试控制代码和测试图形)存储在向量存储器中,在测试系统的初始化阶段(程序装载),测试控制的计算机将编写好的测试向量写入向量存储器。开始测试时,将向量存储器对应的存储单元中的向量数据输出到格式化器。

4.测试信号波形的格式化

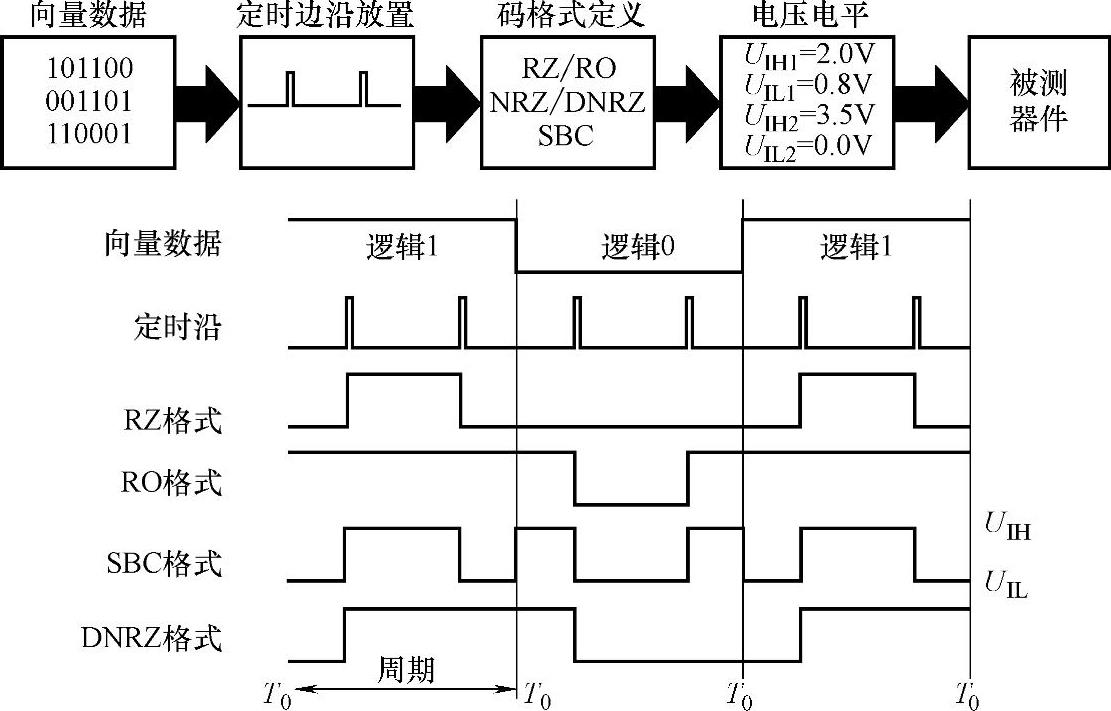

从基于周期的测试原理来看,构成一个测试波形需要4方面的信息:测试周期,根据测试速率要求而定;格式化方式,有NRZ、RO、RZ、SBC等;定时信息,包括输入驱动沿和输出选通沿;状态信号,各类引脚的测试数据。

格式化是将向量存储器送来的数据,按照设定的调制方式,在可编程时钟信号的触发下,转换成对应的已调制波形的基本数字信号。这里将之称为基本数字信号是因为这里仅对数字信号波形的相位(定时时序)进行了调制,而它的幅度未经调节,也未经驱动器驱动,所以还不能直接输出到被测器件的引脚。

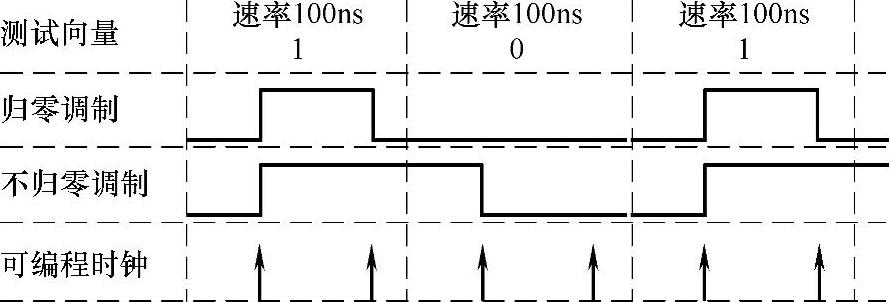

图11-23表示了格式化的工作波形,假定测试周期为100ns,设向量存储器输出数据为101,其中“1”、“0”分别代表逻辑高和低。可编程时钟发生器在每个标准周期中产生两个时钟信号,测试向量存储器送来的逻辑数据流“101”,经格式化器按某种调制方式调制出了相应的波形。图中表示分别按归零调制方式与不归零调制方式调制出的两种不同的基本数字信号波形。

图11-23 格式化器的功能

测试向量的定时和格式化的三个要素是:测试周期、调制方式(信号格式)和可编程时钟。

(1)测试周期

测试周期(testcycle或test period)T=1/f,是根据器件测试的工作频率f而定义的测试向量每一位所持续的时间。测试周期由可编程的时钟信号决定。每个周期的起始点为时间零点(time zero)或T0,为功能测试建立时序的第一步是定义测试周期的时序关系。

(2)输入信号格式

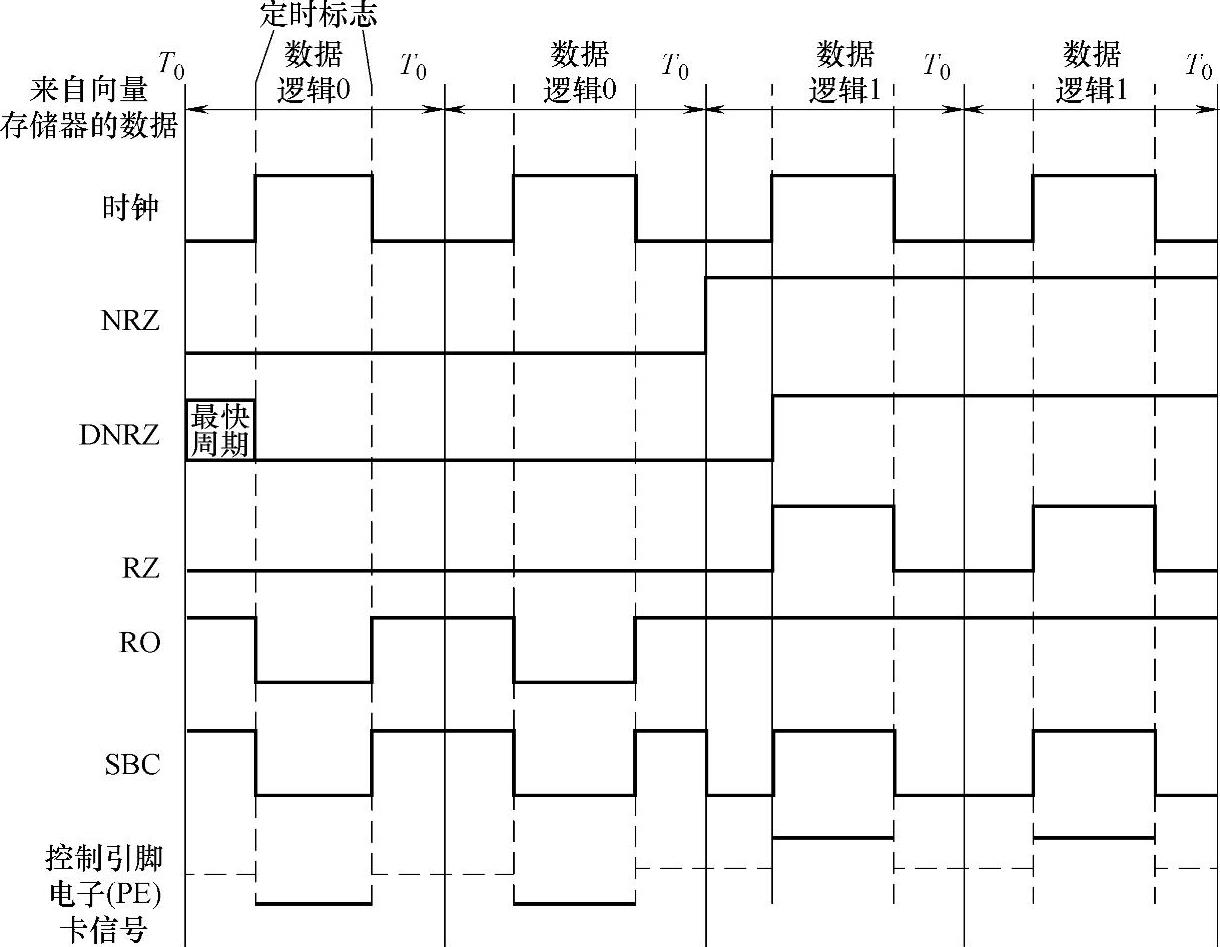

信号的格式对动态功能和AC参数测试是很重要的。信号格式与向量数据、时沿设定及输入电平组合,构成DUT测试的输入信号波形。信号格式的几种形式如图11-24所示。

图11-24 信号格式

1)NRZ(Non Return to Zero非归零码):不返回零电平,代表存储于向量存储器的实际数据,它不含有时钟沿信息,当前周期与前一周期的数据不同时,只在每个周期的起始(T0)发生变化。

2)DNRZ(Delayed Non Return to Zero延迟非归零码):延迟不返回零电平,顾名思义,它和NRZ一样代表存储于向量存储器的数据,只是周期中数据的转变点不在T0。如果当前周期和前一周期的数据不同,DNRZ会在预先定义的延时点上发生跳变。

3)RZ(Return to Zero归零码):返回零电平,当数据为1时提供一个正向脉冲,数据为0时则保持低电平不变。RZ信号含有前(上升)沿和后(下降)沿这两个时间沿。当相应引脚的所有向量都为逻辑1时,用RZ格式则等于提供正向脉冲的时钟。

4)RO(Return to One归一码):返回高电平,与RZ相反,当数据为0时提供一个负向脉冲,数据为1时则保持高电平。RO信号也有前(下降)沿和后(上升)沿。当相应引脚的所有向量都为逻辑0时,RO格式提供了负向脉冲的时钟。

5)SBC(Surround By Complement补码环绕):当前后周期的数据不同时,它可以在一个周期内提供3个跳变沿,信号更为复杂:首先在T0翻转电平,等待预定的延迟后,在定义的脉冲宽度内表现真实的向量数据,最后再次翻转电平并在周期内剩下的时间保持。SBC是运行测试向量时唯一能同时保证信号建立(setup)和保持(hold)时间的信号格式,也被称为XOR格式,它可由数据与时钟异或得到。

6)ZD(High Impedance Drive高阻驱动):该信号格式允许输入驱动在同一周期内打开和关闭。当驱动关闭时,测试通道处于高阻态;当驱动打开时,则根据向量给DUT送出逻辑0或1。

(3)可编程时钟

输入信号格式化中,作为时间基准的可编程时钟极为重要,数字信号的逻辑电平的每一个变化时刻(跳变沿)都是由可编程时钟发生器的信号来定时的。

在不同的测试系统中,设计的可编程时钟发生器的时钟信号的个数和格式可能不同,时钟信号的格式主要取决于格式化器的要求,有边沿触发信号、电平触发信号等。而可编程信号发生器产生的时钟信号的个数越多,说明数字信号的调制方式越丰富,可以方便地产生复杂的数字信号。

(4)输出(响应)信号的采样定时

测试系统检测输出(响应)的变化,是采取定时采样的方式进行的。为了正确地确定输出信号采样点在测试周期内的位置,需要了解被测器件的时序图。被测器件受到输入信号激励后,输出响应信号的传输通常要受到时钟和控制信号的时间沿的控制。确定引起输出信号发生变化的时钟有效沿和控制信号,以及输出达到有效逻辑电平所需要的延迟时间等,才能确定输出信号的采样定时。

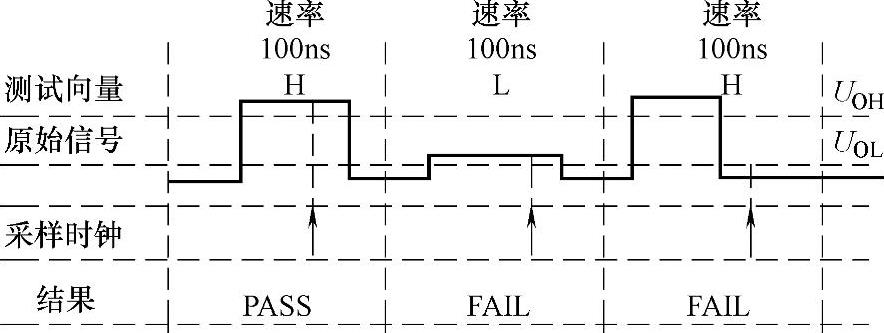

图11-25 比较器工作原理

1)采样时钟。在数字信号比较器中,可编程时钟根据程序的设定来产生采样时钟信号。如图11-25所示,可编程时钟在每个标准周期(假定为100ns)的特定时刻产生一个采样时钟信号,比较器在采样时钟触发时检测被测器件DUT的输出信号。在许多高档的测试系统中,可编程时钟可以产生不止一个的采样时钟信号。在实际的逻辑测试单元中,控制DUT的输入数字信号发生与控制DUT的输出数字信号检测的时钟信号都是由一个可编程时钟发生器提供的。

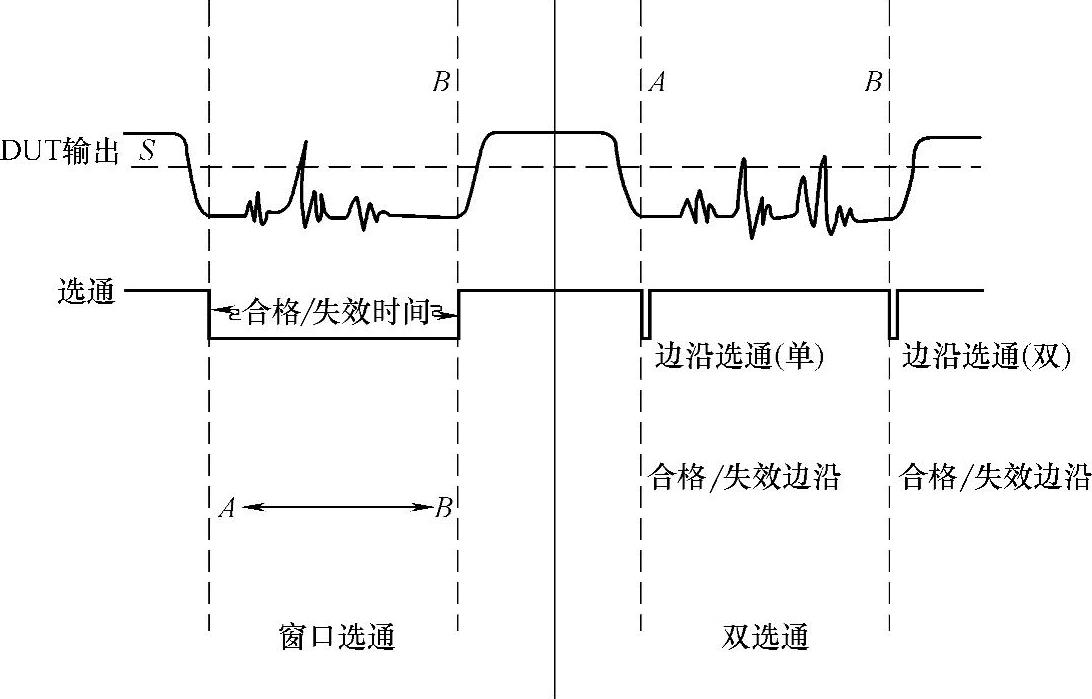

2)输出信号选通方式。功能测试取决于输出选通的方式和它相对于时间T0的位置。目前测试系统中输出响应有两种比较选通方式:有窗口比较选通(WindowComparisonStrobe)和边沿比较选通(edge comparison strobe),窗口模式是在测试周期内特定的一段时间都对输出进行采样和比较,而边沿模式只在测试周期内特定的时间点上采集并比较一次数据,如图11-26所示。图中,假定在时间A至B的区间,DUT输出为低电平信号,逻辑比较阈值电平为S。

图11-26 测试输出选通

如果选通是边沿比较型,并采用单选通模式,由于DUT输出脉冲信号在时刻A低于比较阈值S,所以测试结果将是合格,但是在窗口比较选通时,由于DUT的输出脉冲信号在时间A到时间B的时间间隔内出现了高于比较阈值S的情况,测试结果将是失效。如果考虑到失效是噪声引起的而实际DUT输出脉冲信号在开始点A和结束点B都低于比较阈值S,则可采取双选通模式,即在同一个周期内对DUT引脚使用双重选通采样,测试结果将是合格。在交流参数测试中,双选通也是经常采用的。

5.引脚电路

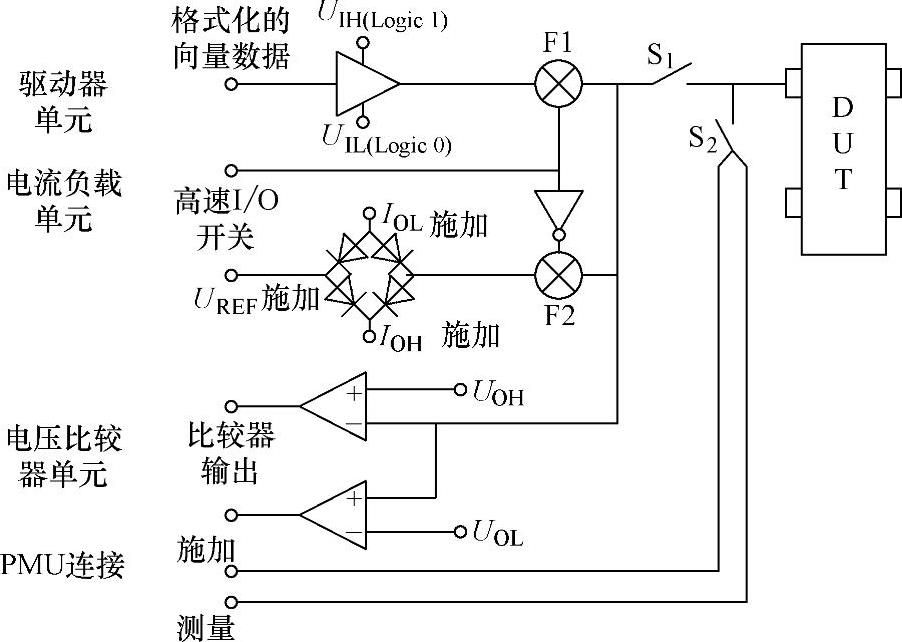

引脚电路(Pin Electronics,PE),是测试系统内部资源和待测器件之间的接口电路,它给待测器件提供输入信号并接收待测器件的输出信号。图11-27表示了数字测试通道的典型PE的I/O电路结构。通常PE电路包括:提供输入信号的驱动电路;可编程的电流负载;驱动转换及电流负载的I/O切换开关电路;检验输出电平的电压比较电路;与PMU的连接电路(端点)。

图11-27 典型的引脚电路单元

(1)驱动单元(TheDriver)

驱动器的功能是对基本数字信号进行幅度调整,并向DUT提供足够的驱动能力,驱动器还能根据测试向量数据在必要时变成高阻状态,以便对DUT的双向端口引脚进行测试。图11-27中F1开关具有输出驱动与DUT之间的隔离作用(高阻状态)。

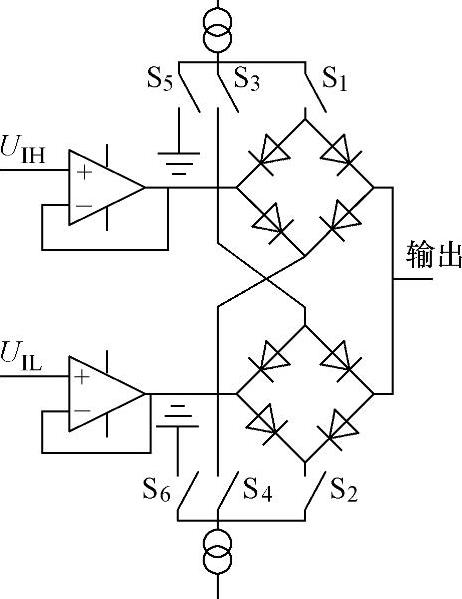

图11-28是一个典型的驱动器结构,由缓冲器、模拟开关及二极管桥构成。当向量为‘1’时,S1与S4接通,输出UIH。当向量为‘0’时,S3与S2接通,输出UIL。当S5、S6接通,其他4个模拟开关断开时,输出端呈现高阻态。图中UIH、UIL是由可编程电平发生器产生的参考电平信号。

(2)电压比较单元(Voltage Receiver)

电压比较器按照设定的采样时钟,对DUT的输出电压和定义的参考电压UOH和UOL同时进行比较。‘逻辑高’定义为电平值高于UOH,‘逻辑低’定义为电平值低于UOL。

图11-28 典型的驱动器结构(https://www.xing528.com)

这里参照图11-25和图11-27,来对比较器的工作作一个简单的介绍。图中的向量为‘HLH’,在程序中的意义是:在程序规定的采样时刻,被测器件的输出信号的原始信号应该是‘逻辑高—逻辑低—逻辑高’。当第一个采样时钟信号到来时,比较器判断原始信号是否满足程序设定的逻辑高电平的范围,从图上可以看出原始信号是满足这一条件的,结果得到一个‘PASS’信号。第二个采样时钟信号到来时,比较器按照逻辑低的要求比较原始信号,结果是‘FAIL’。现在来看第三个采样周期,在第三个时钟周期内原始信号确实有一个逻辑高信号,幅度也满足输出高电平的要求。但经过比较器出来的仍然是一个‘FAIL’,这其中的原因就在于比较器只在采样时钟信号到来时才对原始信号进行比较,这个周期内原始信号虽然包含一个高电平信号,但在比较器对它进行检测时却已回到了低电平,结果自然是‘FAIL’了。

(3)可编程电平

经格式化后的基本数字信号不能直接输出到被测器件,其原因之一是信号的幅度未经调整,还不满足测试要求。为了使基本数字信号的幅度满足测试要求,必须先按照程序设定参考电平信号,驱动器用参考电平信号对基本数字信号进行幅度调节,得到时序、幅度均满足要求的数字信号。

对于比较器,不仅要知道在什么时间去检测,还必须知道比较器在什么电平范围内为通过、在什么范围内为失效,所以数字信号比较器也必须有参考电平。图11-27中的UOH、UOL是两个可编程电平发生器产生的两个参考电平信号。

(4)电流负载单元(Current Load)

电流负载(也叫动态负载)是在功能测试时连接到待测器件的输出端作为负载,由程序控制,可以提供从测试系统到待测器件的正向电流或从待测器件到测试系统的负向电流。电流负载的电路如图11-27所示。

电流负载提供IOH(输出高电平电流)和IOL(输出低电平电流)。IOH指当待测器件输出逻辑“1”时其输出引脚必须提供的电流;IOL则相反,指当待测器件输出逻辑“0”时其输出引脚必须接纳的电流。

电流IOH和IOL由测试程序设定,UREF电压的设置决定了IOH和IOL的转换点。转换点决定了IOH起作用还是IOL起作用;当待测器件的输出电压高于转换点电压时,IOH提供电流;当待测器件的输出电压低于转换点时,IOL提供电流。

F2和F1一样,具有电流负载电路和待测器件的隔离功能,并且作为进行输入-输出切换时的开关。当程序定义测试信道为输出时,则F2接通,允许输出正向电流或抽取反向电流;当定义测试通道为输入时,则F2断开,将负载电路和待测器件隔离。

(5)PMU连接点(PMU Connection)

当要把PMU连接到器件引脚时,S1先断开,将PMU和Pin Electrics卡的I/O电路隔离开来。然后再把S2闭合。

6.输入通道和输出通道的工作原理

(1)输入通道

1)输入数据。输入数据由以下因素的组合构成:①测试向量数据(给DUT的指令或激励);②输入信号时序(信号传输点);③输入信号格式(信号波形);④输入信号电平(UIH/UIL);⑤时序设置选择(如果程序中有不止一套时序)。

首先,最简单的输入信号是以测试向量数据形式存储的一个0和1的二进制码,而代表逻辑0或逻辑1的电平则由测试头中的UIH/UIL参考电平产生。大部分输入信号是包含唯一格式(波形)和时序(时沿设定)的更为复杂的数据形式。

2)输入通道时序。决定测试周期,以及周期内各控制信号的布局及时钟沿位置。通常来说,输入信号有两类:控制信号和数据信号。数据信号在控制信号决定的时间点提供数据到被测器件。

①首先要决定的是控制信号的有效时沿和数据信号的建立和保持时间,这些信息将决定周期内各输入信号时间沿的位置。②决定各输入信号的格式。时钟信号通常使用RZ(正脉冲)或RO(负脉冲)格式;上升沿有效的信号如片选(CS)或读(READ)常使用RZ格式;下降沿有效的信号如输出使能(OE)常使用RO格式;如有建立和保持时间要求的数据信号常使用SBC格式;其他的输入信号则可以使用NRZ或DNRZ格式。③从测试头输出的信号波形是测试向量、时沿设置、信号格式及UIH/UIL设置共同作用的结果,如图11-29所示。

图11-29 输入信号的产生及时序波形

(2)输出通道

1)输出数据。输出部分的测试由以下组合构成:①测试向量数据(期望的逻辑状态);②采样时序(周期内何时对输出进行采样);③UOL/UOH(期望的逻辑电平);④IOL/IOH(输出电流负载)。

2)输出通道时序。测试数据的输出如图11-30所示,它包括以下各个环节:向量数据决定期望的逻辑状态;UOL/UOH参考电平决定期望的输出电压;输出采样时序决定着周期内输出信号的测试点;输出比较屏蔽(mask)控制输出结果是否进行pass/fail判断。

图11-30 输出信号的测试及时序波形

7.功能测试的实例

(1)功能测试参数定义

功能测试可按以下步骤进行:①定义电源UDD电压;②定义输入、输出电平(UIL/UIH/UOL/UOH);③定义输出电流负载(IOL/IOH/UREF);④定义测试周期;⑤为所有输入信号定义输入时序和信号格式;⑥为所有输出信号定义输出采样时序;⑦为向量存储器定义向量的起始和终止点;⑧运行测试。

验证器件的功能是否符合规范,通常有两种方法。第一种方法是将所有的输入、输出和时序参数都设置成最差(规格书中定义最严格)的情况,然后运行功能向量序列。这种方式能最快地判断器件是否符合其设计规范,缺点在于如果有fail发生,无法直观地知道是由什么参数引起的该故障。另一种方法是单独地设置各个参数,例如,开始只按照规格书定义的最差情形设置UIL/UIH,其他的参数则放宽。如果有fail发生在这个地方,则马上可以判断是UIL或UIH电平引起的。然后再设置下一组参数,直到所有参数都被单独验证。此方式可以直观地获取更多具体的信息,代价是增加了测试时间。

(2)功能测试内容

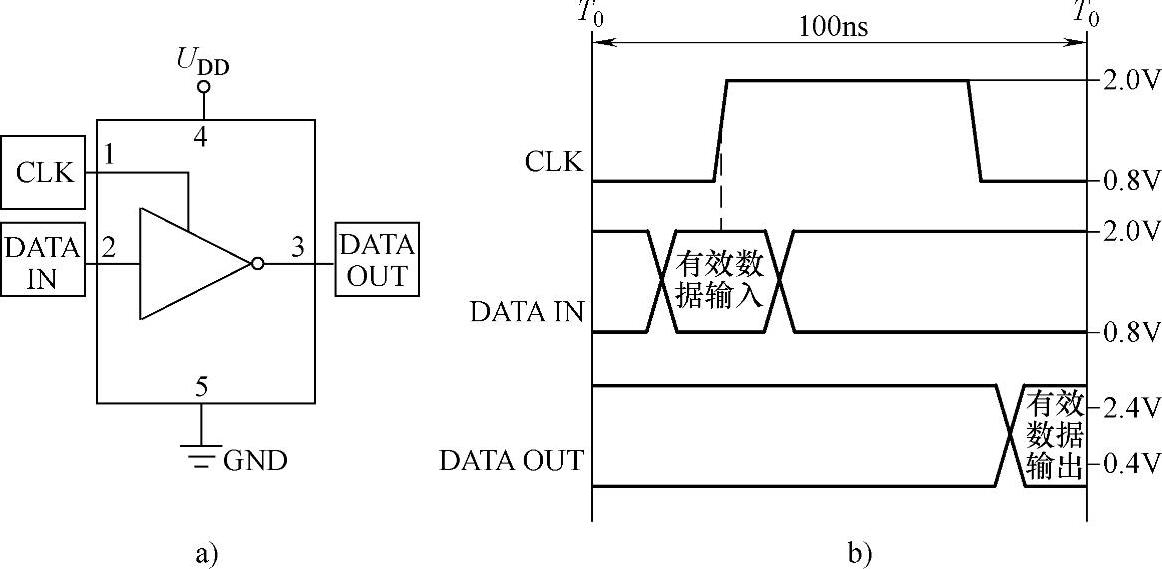

为了对功能测试所涉及的器件规格、测试系统硬件和测试程序之间的关系做一个整体的了解,这里以一个简单的器件——受时钟控制的反相器(见图11-31a)为例,来说明相关功能测试内容。钟控反相器有两个输入端:时钟输入(CLK)和数据输入(DATAIN);一个输出端:反向信号输出(DATAOUT)。它有如下功能特征:①时钟是数据由输入到输出经过器件进行传输的同步控制信号;②输入数据在时钟的上升沿由器件读入;③输入数据在时钟的下降沿从器件输出;④数据传输仅在时钟有效时进行;⑤输出数据与输入数据逻辑相反。

1)器件规范。规范中给出了器件需要满足的最差情况,测试时可根据它去制订测试计划(Test Plan)、选择合适的测试系统来实施其测试。下面以测试某型号的钟控反相器为例进行阐述。

该钟控反相器规范中需要控制的电平及时序参数(见图11-31b)如下:

UDD=5.0V;UIH=2.0V,UIL=0.8V;UOH=2.4V,UOL=0.4V;工作频率=10MHz,时钟占空比50%;输入数据建立时间为15ns;输入数据保持时间为5ns;输出传输最大延时为8ns。

图11-31 钟控反相器

a)反相器电路 b)工作时序图

2)测试所需资源及参数设定

①测试硬件及设备——负载板(Loadboard)、测试座(Socket)、相关阻容元件。

②器件电源,UDD和GND。

③输入电平,UIL(逻辑0)和UIH(逻辑1)。

④输出参考电平,UOL(逻辑0)和UOH(逻辑1)。

⑤信号时序和格式配置,包括输入信号的生成和输出信号的比较。

⑥测试向量。

测试系统内的资源较多,要针对测试需求选取并配置相关的资源。首先,需要DPS单元对器件供电,提供UDD为5V的直流电压。其次,由RVS(参考电压单元)提供输入电平和输出比较的参考电平。这里UIL设定为0.8V,UIH设定为2.0V;UOL设定为0.4V,UOH设定为2.4V。

测试系统的时序单元设定输入信号的周期、信号格式及输出信号的比较沿位置,如图11-32所示。对于时钟信号,器件规范书给出的频率是10MHz,则时钟周期为100ns;占空比要求是50%,即一个周期内时钟信号一半为高电平一半为低电平,时钟信号格式选用RZ格式。这里将时钟的上升沿设定在25ns时刻,下降沿设定在75ns时刻。

为了能正确地验证建立时间和保持时间,选用SBC格式作为DATAIN的信号格式。DA- TAIN的时序设置则需要参考时钟信号。它的建立时间是15ns,即在时钟的上升沿之前15ns,它的状态必须是有效的;保持时间是5ns,即上升沿之后的5ns它必须保持相同的状态。这样就知道周期内数据信号的脉宽最小是20ns,即图11-31b中的“1”或“0”的有效数据宽度均为20ns。

最后一步是确定输出信号的相关时序。规范书给出的信号传输延迟为8ns,以及时钟的下降沿在75ns时刻,则可以确定输出信号比较沿的位置;75ns+8ns=83ns,测试系统在此位置上对输出采样并将电平值与UOL/UOH相比较,判断状态为L、M还是H,再与测试图形中的期望值比较以判断此周期的输出正确与否。

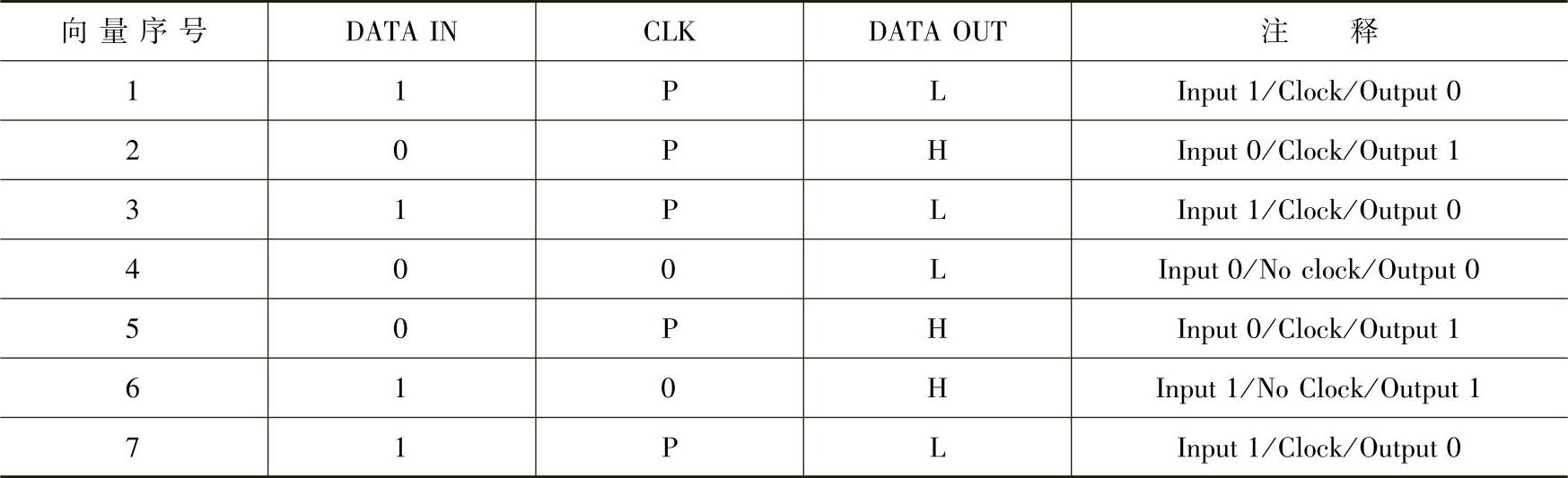

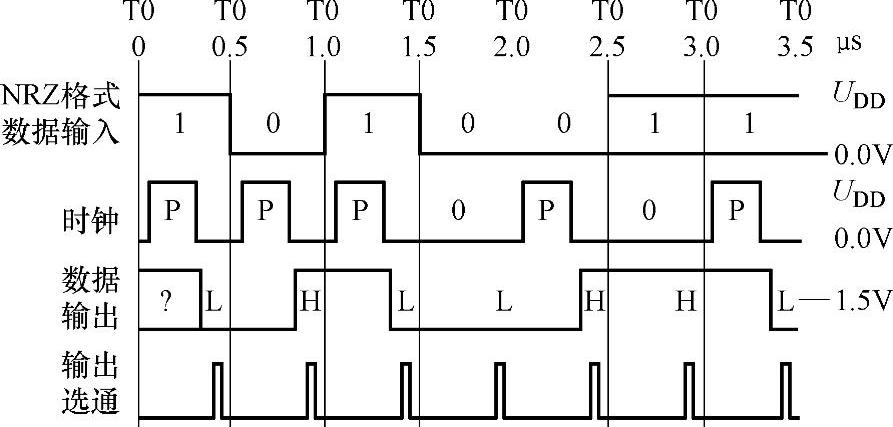

3)测试向量。功能测试必须有测试向量,也就是反映器件真值表的图形化文件,见表11-3,钟控反相器的向量文件中有7条测试矢量,能够验证该钟控反相器的逻辑功能。表中还包含几种向量字符,每个字符都代表一个周期数据状态,它们与时序、电平和格式等信息共同构成相关信号的波形,如图11-32所示。

表11-3 钟控反相器的测试向量

注:P——Drive input with a positive clock pulse(上升沿脉冲输入);

1——Drive input high(to logic 1)(输入高电平);H——Compare output to a high(输出高电平);

0——Drive input low(to logic 0)(输入低电平);L——Compare output to a low(输出低电平)。

4)功能测试时序。图11-32显示的是运行功能测试期间钟控反相器各信号的时序图,可以看到由信号时序、信号格式及信号电平组合而成的七个周期的向量数据,这和之前规格书中定义的情形一致。测试周期设定为100ns;时钟信号则是RZ信号格式,占空比为50%;DATAIN采用SBC格式,设置了正确的建立时间和保持时间;输入和输出的电平值也按照器件规范进行了设定。

图11-32 钟控反相器指标功能测试定时图

5)总功能测试。总功能测试是在使用最宽松的条件下,即不用精确参数设置的情况下,基本判断器件是“好”还是“故障”的一种基本的功能测试。总功能测试能最快地检测出半导体内部的物理损伤或制造过程中的错误。总功能测试可以作为检验器件是否要进行功能测试的前提测试。

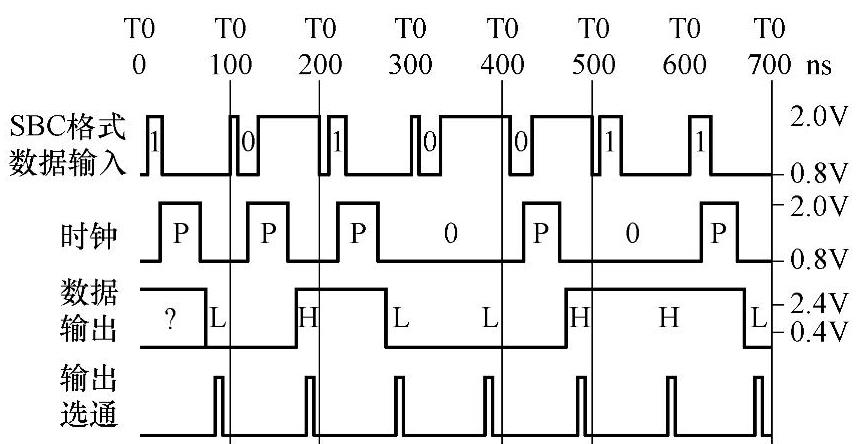

图11-33的波形显示的是总功能测试用到的时序及电平条件。输入和输出电平较功能测试条件有所放宽,测试速度由原来的100ns放宽至500ns;DATAIN信号则改为在每个周期的开始启动的NRZ格式,放弃了对建立和保持时间的测试;输出传输延迟也适当增加,让输出有更多时间去改变状态并稳定。这使得器件更容易正确运行其功能。

如果器件在图11-32的测试条件下测试判为失效(fail),而在图11-33的测试条件下重新测试判为通过(pass),则之前的失效不是由硅缺陷引起的。这时则需要对每个具体的参数单独测试,以找出失效的真正原因。总功能测试条件常被用于测试向量的调试阶段,它可以在排除其他因素干扰的情况下轻易判断测试向量是否正确。

图11-33 钟控反相器总功能测试定时图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。