1.直流(DC)参数的测试

集成电路直流参数测试是通过在DUT引脚上进行电压或电流的测量来验证电气参数。常用的测试方法有施加电流测量结果电压(简称加流测压FIMV)和施加电压测量结果电流(简称加压测流FVMI)。所测的直流参数通常有连接性、泄漏、功耗、高/低电平电压、驱动能力、噪声干扰等。直流参数测量不一定要求有很快的速度,直流参数测试主要考虑测试准确度和测试效率(每个器件引脚的每个参数的测试时间)。

对于SSI和简单的MSI,通过直流参数测试通常即可判明其质量,即在输入、输出和电源引脚进行直流参数测试,得到影响器件可靠性和性能的各项因素。它是针对每个引脚的逻辑“0”或“1”状态,或者是输出引脚的第三态(禁止态)进行测试。所测参数有:输入钳位电压(UIK)、输出高/低电平(UOH/UOL)、输入高/低电流(IIH/IIL)、输入泄漏电流(IL)、输出短路电流(IOS)以及电源电流(ICCH/ICCL)等。

各直流参数的测试详述如下。

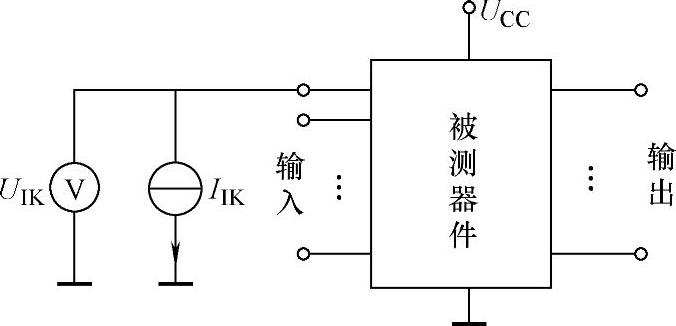

(1)输入钳位电压(UIK)测试

UIK是在器件输入端抽出规定的电流IIK时的电压,此参数检查输入钳位二极管是否正常。测试原理图如图11-9所示。通常UCC加规范的最小值,使用FIMV方式,在被测输入端抽取规范规定的电流IIK,其他输入端和输出端开路,在被测输入端检测UIK。如果UIK值在规范值之内,说明钳位二极管正常。

图11-9 UIK测试原理图

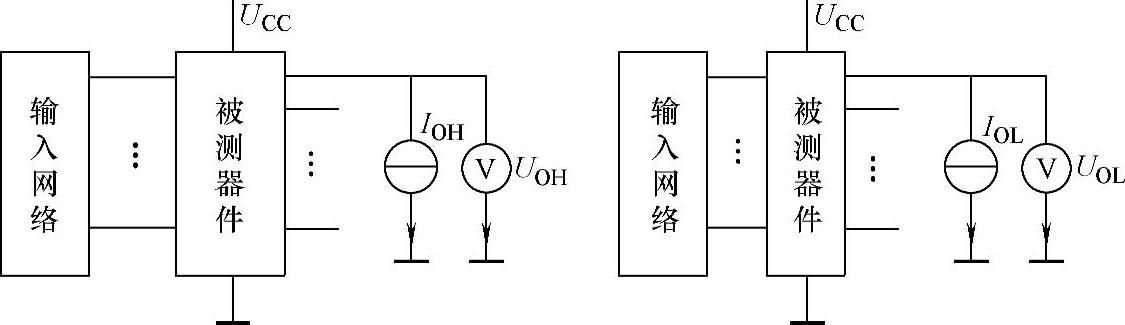

(2)输入高/低电平(UOH/UOL)测试

UOH(UOL)是输入端在施加规定的电平下,使输出端为逻辑高电平H(低电平L)时的电压。测试原理图如图11-10所示。UCC通常为规范的最小值,在进行UOH、UOL测试时,首先要对被测器件加预置条件。测试使用FIMV方式:对于UOH测试,在被测输出端抽取规范规定的负载电流IOH,其余输出端开路,同时测量该端输出电压UOH;对于UOL测试,在被测输出端注入规范规定的负载电流IOL,其余输出端开路,同时测量该端输出电压UOL。UOH、UOL测试主要检查抗干扰能力。

图11-10 UOH和UOL测试原理图

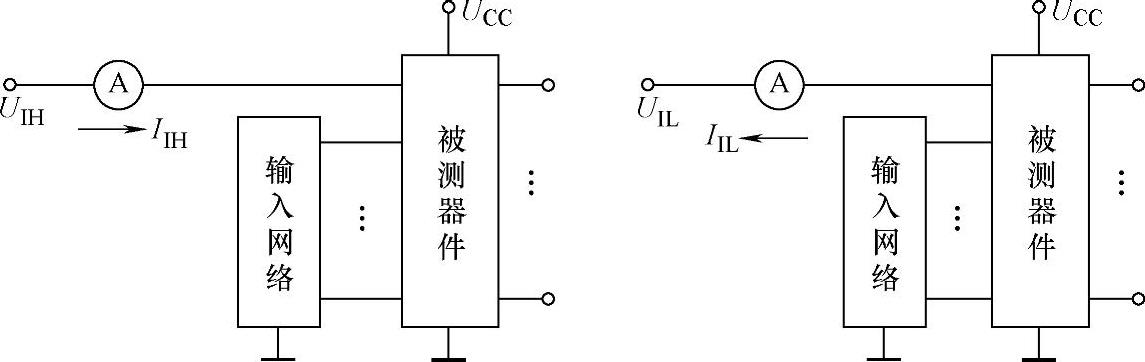

(3)输入高/低电流(IIH/IIL)测试

IIH(IIL)是输入端在施加规范规定的高电平电压UIH(低电平电压UIL)时流入(流出)被测器件的电流。测试原理图如图11-11所示。在IIH、IIL的测试中,UCC往往被置于规范的最大值。测试使用FVMI方式,在被测输入端施加规范规定的输入高电平电压UIH(低电平电压UIL),其余输入端施加规定电平,输出端开路,测量输入高电平电流IIH(低电平电流IIL)。IIH和IIL验证DUT接受逻辑“1”和“0”电平的能力,目的是检查DUT的负载特性。

图11-11 IIH、IIL测试原理图

(4)输入泄漏电流(IL)测试

IL是输入端在施加规范规定的最大输入电压UL时流入被测器件的电流。测试原理与图11-11相同,UCC一般也是加规范规定的最大值,只是加压和测流值不同。在IL测试中,被测输入端施加最大输入电压,其余输入端加规定电平,输出端开路。IL测试用以检查DUT的扇入负载特性。

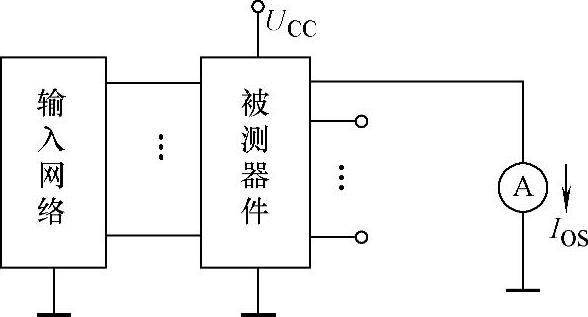

(5)输出短路电流(IOS)测试

IOS是输入端在施加规范规定的电平下、输出为逻辑高电平、输出端对地短路时的输出电流。测试原理图如图11-12所示,通常UCC加规范的最大值。DUT输入端施加规定的电平并以一定的激励使被测输出端呈现逻辑高电平,然后将该输出端对地短路,其余输出开路,并测量该端的输出短路电流IOS。测试中也是加压测流方式,但所加电压是特殊的零电压值。IOS测试用以检查DUT的扇出负载能力。

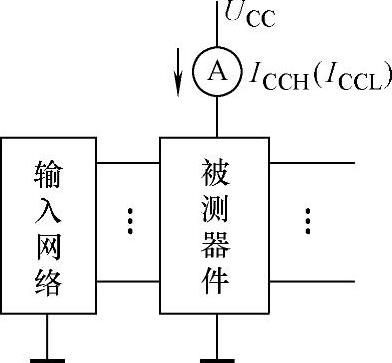

(6)电源电流ICCH/ICCL测试

ICCH(ICCL)是输入端施加规定的电平,使输出端为逻辑高电平(低电平)时,经电源端流入被测器件的电流。测试原理图如图11-13所示。测试时,在输入端加入特定的激励使输出端为高(低)电平,输出端开路,电源电压通常使用规范的最大值,在电源端测量ICCH或ICCL。这是加压测流方式,检测被测器件功耗。

图11-12 IOS测试原理图

图11-13 ICCH和ICCL测试原理图

数字集成电路的直流参数测试主要使用集成电路测试系统中必备的精密测量单元PMU实现,关于PMU将在本章的11.4节专门讲述。

2.交流(AC)参数的测试

集成电路交流参数测试是验证与时间相关的参数,对电路工作时的时间关系进行测量,测量输入信号后电路随时间的响应、电路内部逻辑状态的变化时间、输入和输出信号之间的时间关系、电路的极限工作频率等。测量的方法是确定输入信号和输出信号的两个不同(或相同)电压电平之间的时间间隔,所取电压电平值通常是信号脉冲幅度的50%、10%或90%。

最常测量的交流参数有上升和下降时间、传输延迟、建立和保持时间以及存取时间等。交流参数测试最关注的是最大测试速率和重复性能,其次才为准确度。集成电路的时间参数值一般是ns级,甚至ps级,极限工作频率在MHz~GHz,所以时间测试分辨率要求很高。

大多数数字集成电路自动测试系统都有专门的时间测量单元TMU,提供可选择的高时间测量分辨力(从ns到10ps),准确测量出传输延时及上升沿、下降沿时间等,而不再需要其他昂贵的精密测量仪器。TMU的组成和基本原理在本书的第3章3.5节中有关高分辨力的时间间隔测量技术中有详细讨论,此处不再赘述。

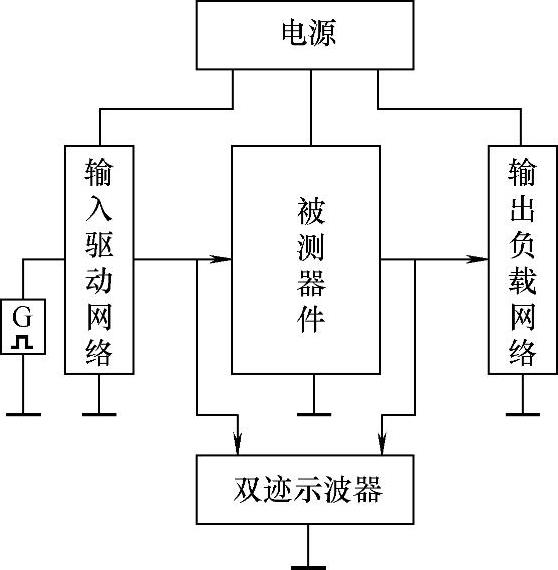

数字集成电路交流参数(动态参数)项目较多,各参数测试方法不同,但其基本测试原理均可归结为在时域内进行测量,即在规定的条件下,对DUT被测输入端施加脉冲信号,用TMU或高档示波器,测量由参数定义规定的信号边沿参考电平处的时间间隔。规定条件有环境温度、电源电压UCC(UDD)、输入端施加电平、输出负载、参考电平UREF和输入端施加的脉冲电压幅度Um、频率f、上升时间tr、下降时间tf等,它们应符合产品规范的规定。常见的交流参数测量方法如下。

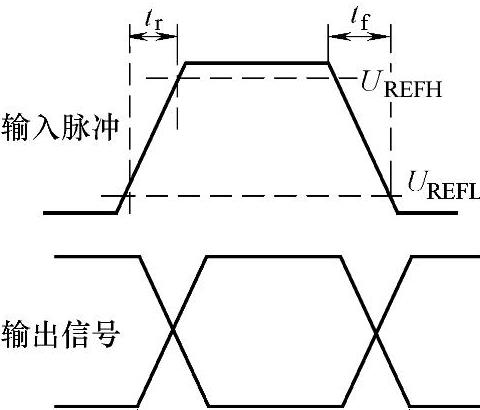

(1)输入脉冲上升/下降时间tr/tf的测量

时序逻辑器件中输出逻辑电平按规定临界转换前,在触发输入端施加的输入脉冲上升/沿上两个规定参考电平间的最大时间间隔,定义为输入脉冲上升/下降时间tr/tf。输入脉冲上升/下降时间tr/tf测量原理图如图11-14所示。输入脉冲上升/下降时间tr/tf波形图如图11-15所示。(https://www.xing528.com)

图11-14 tr/tf、tPLH与tPHL测量原理图

图11-15 输入脉冲上升/下降时间tr/tf波形图

测试方法:在被测器件触发输入端施加输入脉冲,其余输入端施加电平,输出端接负载。调节输入脉冲上升/下降沿时间,使输出逻辑电平按规定临界转换,测量输入脉冲电压上升/下降沿上两个规定的参考电平(UREFL、UREFH)间的最大时间,该时间间隔即为输入脉冲上升/下降时间tr/tf。

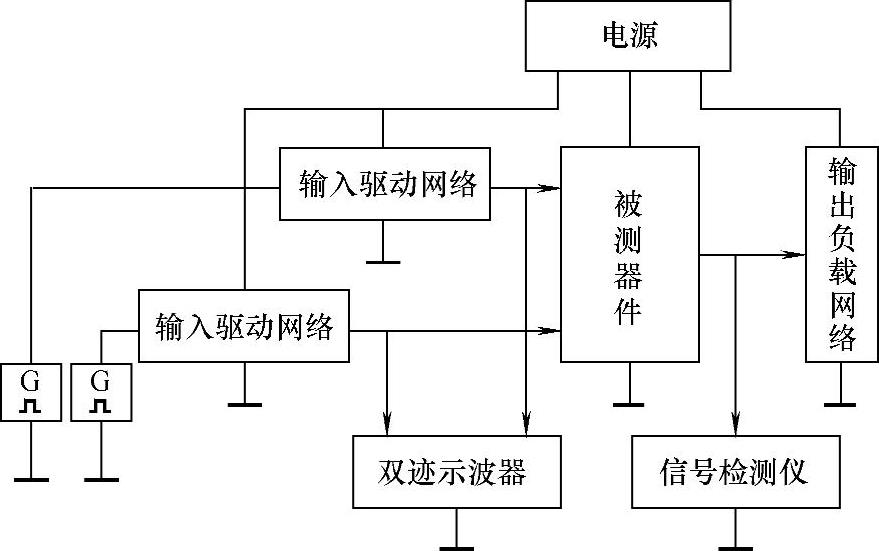

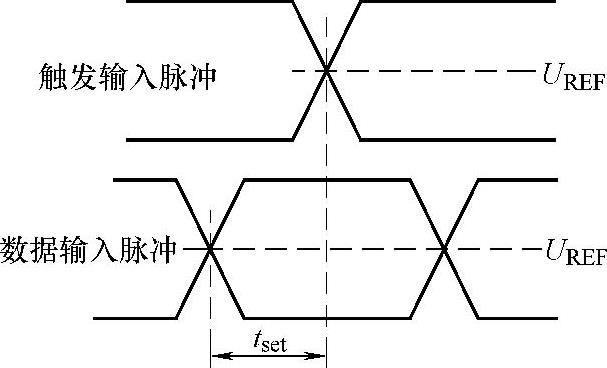

(2)建立时间tset的测量

时序逻辑器件输出逻辑电平按规定临界转换时,数据输入脉冲电压应比触发输入脉冲电压提前施加于被测器件的最小时间间隔,定义为建立时间tset。建立时间tset的测量原理图如图11-16所示。建立时间tset波形图如图11-17所示。

图11-16 tset、tH测量原理图

图11-17 建立时间tset波形图

测试方法:在被测器件数据输入端和触发输入端加脉冲电压,其余输入端施加电平,被测输出端接负载,其余输出端开路。调节被测数据输入端的脉冲电压比触发输入端施加的脉冲电压超前的时间,使输出逻辑电平按规定临界转换,该时间间隔即为建立时间tset。

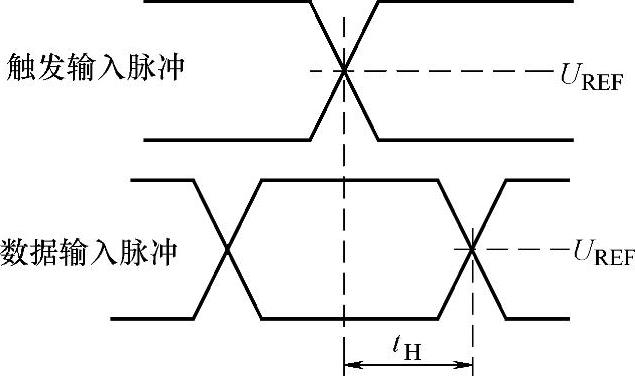

(3)保持时间tH的测量

时序逻辑器件输出逻辑电平按规定临界转换时,数据输入脉冲电压在触发输入脉冲电压过后应保持的最小时间间隔,定义为保持时间tH。

保持时间tH的测试原理图如图11-16所示。保持时间tH波形图如图11-18所示。

测试方法:在被测器件数据输入端和触发输入端施加脉冲电压,其余输入端施加电平,被测输出端接负载,其余输出端开路。调节数据输入端施加的脉冲电压比触发输入端施加的脉冲电压滞后的时间,使输出逻辑电平按规定临界转换,该时间间隔即为保持时间tH。

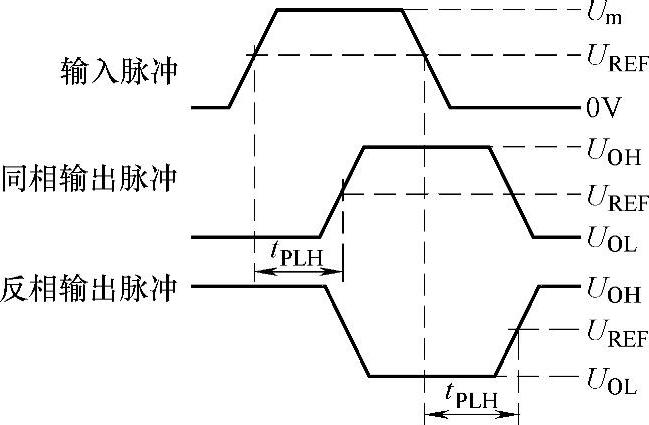

(4)输出由低电平到高电平传输延时tPLH的测量

输入端在施加规定电平的脉冲时,输出脉冲由低电平到高电平的边沿和对应的输入脉冲边沿上两个规定的参考电平间的时间间隔,定义为输出由低电平到高电平的传输延时tPLH。tPLH的测试原理图如图11-14所示。tPLH波形图如图11-19所示。

图11-18 保持时间tH波形图

图11-19 传输延时tPLH波形图

测试方法:在被测器件输入端施加规定电平的脉冲,其余输入端施加电平,被测输出端接负载,其余输出端开路。在被测输出端输出脉冲由低电平到高电平转换边沿的参考电平UREF处和对应的输出脉冲转换边沿的参考电平UREF处,两者之间测得的时间间隔即为输出由低电平到高电平的传输延时tPLH。

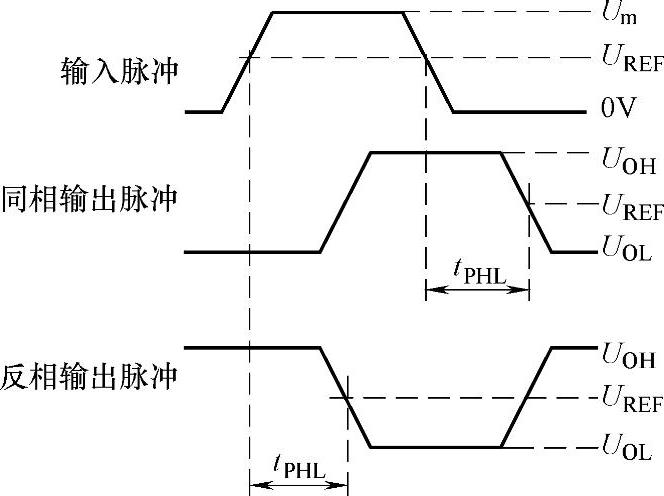

(5)输出由高电平到低电平传输延时tPHL的测量

输入端在施加规定电平的脉冲时,输出脉冲由高电平到低电平的边沿和对应的输入脉冲边沿上两个规定的参考电平间的时间间隔,定义为输出由高电平到低电平的传输延时tPHL。tPHL的测试原理图如图11-14所示。tPHL波形图如图11-20所示。

测试方法:在被测器件输入端施加规定电平的脉冲,其余输入端施加电平,被测输出端接负载,其余输出端开路。在被测输出端输出脉冲由高电平到低电平转换边沿的参考电平UREF处和对应的输入脉冲转换边沿的参考电平UREF处,两者之间测得的时间间隔即为输出由高电平到低电平传输延时tPHL。

(6)最高时钟频率fmax的测量

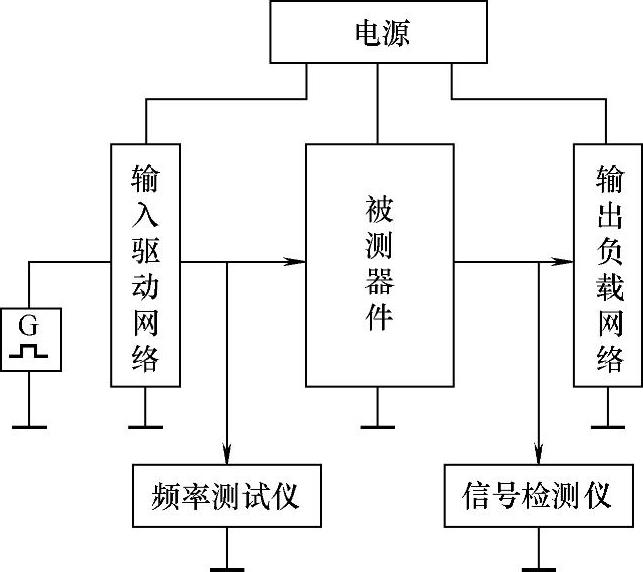

时序逻辑器件,输出逻辑电平按规定临界转换前,在时钟输入端施加的输入脉冲的最高频率定义为最高时钟频率fmax。它的测试原理图如图11-21所示。

测试方法:在时钟输入端施加脉冲电压,其余输入端施加规定电平,被测输出端接规定负载,其余输出端开路。调节输入脉冲电压频率,使输出逻辑电平按规定临界转换,该频率即为最高时钟频率fmax。

图11-20 传输延时tPHL波形图

图11-21 最高时钟频率fmax测试原理图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。