直接数字合成(DDS)和锁相环频率合成(PLL)相结合,可进行优势互补,构成性能优异的合成信号源。DDS本身频率转换很快,但是DDS的输出频率低,杂散多。所以要依靠PLL实现倍频和跟踪滤波。而PLL在频率转换时需要一定的捕获时间,这个捕获时间与环路的类型、参数和跳频步长等有关。一般来说,当步长为10MHz左右时,捕获大概需要10~20μs。当步长很大时,会达到毫秒级。所以DDS+PLL频率合成器的频率转换时间取决于PLL,而不是DDS,PLL的频率转换时间长,这等于牺牲了DDS频率转换快速的优点来换取高输出频率。

DDS+PLL频率合成器的电路一般有两种形式:用DDS作为PLL环路的参考源和用DDS作为PLL环路的分频器。

1.DDS作PLL的参考源

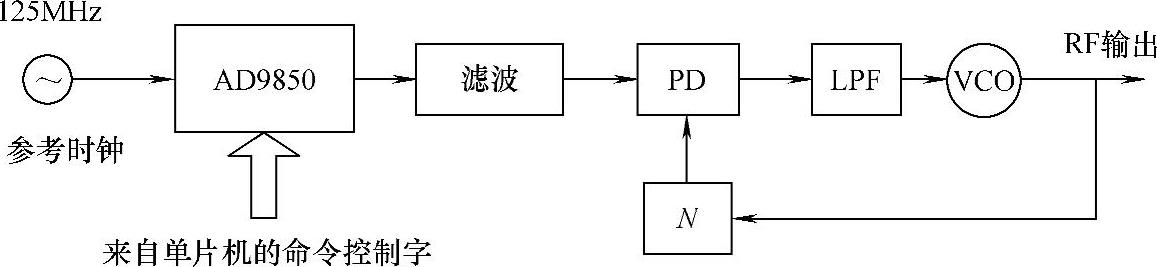

直接数字频率合成芯片DDS作为PLL锁相频率合成环的可变参考频率的信号源,构成了一个DDS+PLL频率合成器。这种结构适用于各种型号的DDS和PLL芯片。图9-38所示电路用AD9850DDS系统输出作为PLL的参考信号,虽然DDS的输出频率低,杂散输出丰富,但是它具有频率转换速度快、频率分辨力高等优良性能,而PLL设计成N倍频PLL,提高了输出频率,利用DDS的高分辨力来保证PLL输出有较高的频率分辨力,而通过PLL的杂散输出可以减少。

图9-38 用AD9850系统输出作为PLL的信号

PLL采用单环频率合成技术,以使DDS+PLL频率合成器的结构简单,性能稳定。在这种方案中,由DDS为锁相环提供一个高精度参考源,频率的调节由DDS和PLL两个芯片共同决定。

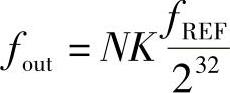

输出频率为

(https://www.xing528.com)

(https://www.xing528.com)

频率分辨力为

式中,K为AD9850频率控制字;N为PLL环路分频器的分频值。整个系统换频精度受到DDS特性、滤波器的带宽和锁相环参数的影响,频率切换时间主要由锁相环决定。

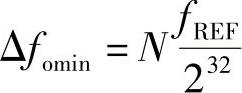

2.DDS作PLL的可编程分频器

这种方案又称为PLL内插DDS频率合成器,组成原理如图9-39所示。VCO输出频率作为AD9850DDS的参考频率源,DDS的输出频率为fDDS=Kfout/232=fout/N,K为AD9850频率控制字,PLL环路分频器的分频值为N=232/K,由于K=1~231,所以N=2~232。在VCO输出允许情况下,该PLL输出频率为fout=NfREF=(2~232)fREF。这样可以得到具有很高频率分辨力的倍频锁相环。

图9-39 PLL内插DDS频率合成器原理

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。