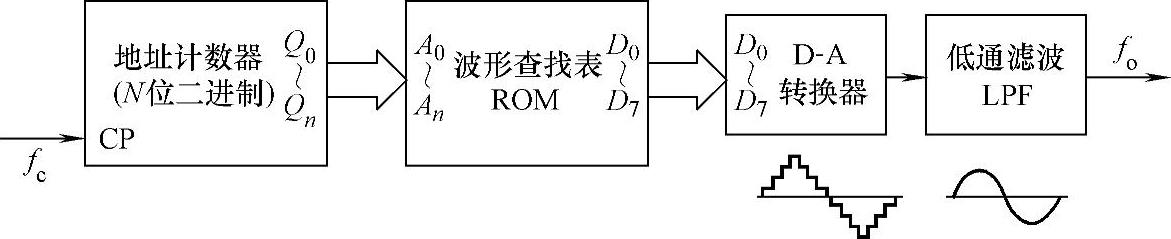

1.简单DDS信号源的组成

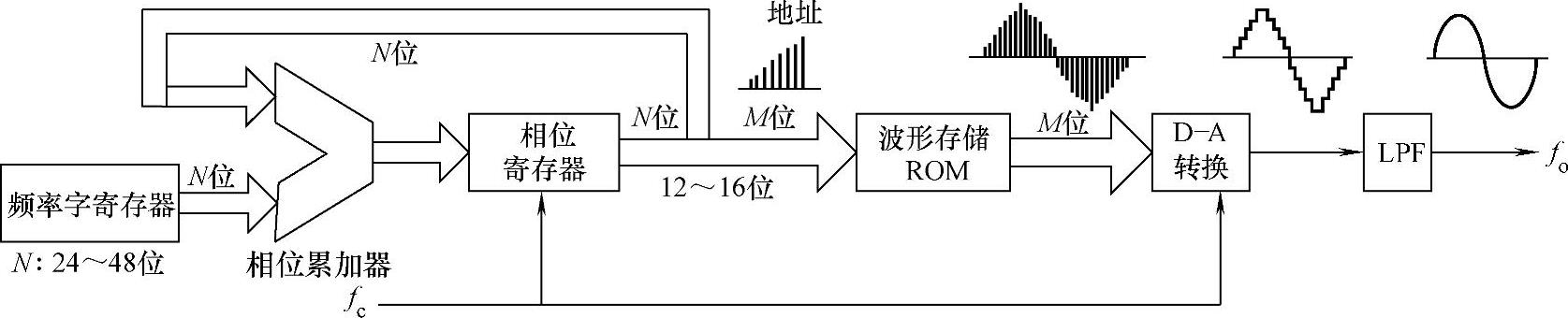

一个简单的DDS信号源组成框图如图9-33所示。设图中的地址计数器为一个N位二进制加法计数器,用以生成控制波形查找表ROM的地址信号;ROM有2N个存储单元(相应N位地址),存储了一个周期正弦波形的采样数据以便于查找。

图9-33 简单DDS信号源的组成原理

当地址计数器在时钟fc的作用下进行加1计数时,就能从波形查找表ROM中按由小到大的地址顺序逐单元读出预存在ROM中的波形数据,这些数据再经过D-A转换及滤波,就可以得到连续的正弦波形信号。

2.信号波形的相位-幅度数据表(波形数据表)

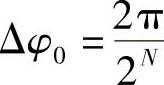

根据采样定理,任何频率的连续信号可以看作由一系列离散的采样点所组成。对于一个周期性的连续信号波形,若在它的一个周期内采样了2N点,从信号的相位出发,则每一个采样点之间的相位差Δφ0为

或

或

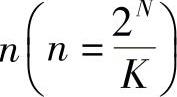

再将每一个采样点的幅值量化,则可形成一个相位与幅度一一对应的波形数据表(波形查找表),将此表预先存放在波形存储器(ROM)中,存储地址码表示相位值,该地址单元内存放的数据为波形的幅度值。从波形数据表输出信号的方法是,在时钟fc的驱动下,地址计数器做累加计数,其线性增加的计数值作为波形数据表存储器地址,周而复始地对ROM寻址,按地址增加的顺序逐个地读出波形数据,再经过D-A转换和滤波后,输出信号波形。输出信号频率为

由此说明,改变时钟频率fc或者改变ROM中每周期波形的采样点数(2N),均能改变输出信号波形的频率fo。改变fc的方法不够灵活,在DDS合成信号源中很少采用。大多情况下采用改变采样点数2N的办法。

3.间隔采样读取技术

为了改变DDS的输出频率f,DDS通常采用间隔取值的方法来改变ROM中每周期波形的采样点数。间隔采样读取的方法是每间隔K个地址读出一个数据,此时输出信号频率为

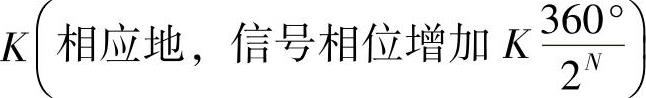

通常,将式(9-28)称为DDS方程,改变K值,相当于改变了每周期To内从ROM中抽取的样点数 ,也就可以改变DDS的输出频率fo,故将K称为频率控制字。增加K值,提高了输出频率fo。从相位概念出发,K值实际上反映从ROM中读出两个采样数据之间相位差的大小,采用间隔抽样后的相位分辨力为

,也就可以改变DDS的输出频率fo,故将K称为频率控制字。增加K值,提高了输出频率fo。从相位概念出发,K值实际上反映从ROM中读出两个采样数据之间相位差的大小,采用间隔抽样后的相位分辨力为

由此可见,间隔抽样的相位分辨力随K值变化。增加K值,降低了相位分辨力。

4.基于相位累加器的DDS的基本结构

为了实现间隔式地采样读取,完成K为任意数的地址累加计数,需采用相位累加器,基于相位累加器的DDS原理框图如图9-34所示。

(1)相位累加器

相位累加器是DDS系统的核心,它由频率字寄存器、相位累加器(二进制全加器)和相位寄存器组成,三者的位宽均为N。频率字寄存器中存放的频率控制字K,作为全加器的一个输入;相位寄存器用于寄存全加器的计算结果,它又作为全加器的另一个输入,同时也作为波形存储器的取数地址;全加器做累加计算,即将频率控制字K与相位寄存器的输出数据(累加器已累加的值)相加。这样,在时钟fc作用下,相位累加器能不断对频率控制字K进行线性相位累加,即每来一个时钟,相位累加器输出的数值n就增加K,即nt+1=nt+K,也即波形存储ROM的地址增加 ,按K的地址间隔取出ROM中的波形采样值,当相位累加到360°满量程,即nt+1≥2N时,就会产生一次溢出,完成波形一个周期的相位-幅度转换,输出一个周期的波形,同时开始进入下一周期的过程,从而可以连续输出周期性的信号波形。

,按K的地址间隔取出ROM中的波形采样值,当相位累加到360°满量程,即nt+1≥2N时,就会产生一次溢出,完成波形一个周期的相位-幅度转换,输出一个周期的波形,同时开始进入下一周期的过程,从而可以连续输出周期性的信号波形。

图9-34 基于相位累加器的DDS原理框图

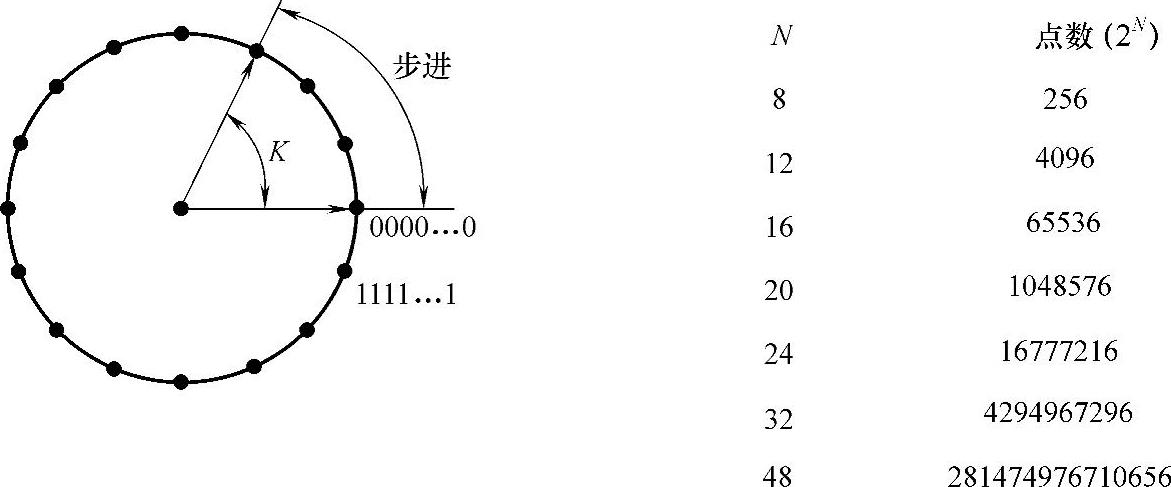

为便于理解,可以将正弦波波形看作一个矢量沿相位圆转动,相位圆对应正弦波一个周期的波形。波形中的每个采样点对应相位圆上的一个相位点,如图9-35所示。(https://www.xing528.com)

图9-35 数字相位圆

如果正弦波形定位到相位圆上的精度为N位,则其分辨力为1/2N,即以fc对基本波形一周期的采样数为2N。如果相位累加时的步进为K(频率控制字),则每个时钟fc使得相位累加器的值增加K/2N×360°,即φt+1=φt+(K/2N)×360°,因此每周期的采样点数为2N/K,则输出频率为fo=(K/2N)fc

(2)波形存储器

波形存储器又称波形查找表ROM,其作用是以累加器输出的相位值作为地址,转换成(查找出)对应的波形幅度的数字值输出。

在实际的DDS设计中,为了提高波形的相位精度,获得足够高的频率分辨力,采样点数2N通常取得很大,例如,N值取32~48位,可以得到毫赫兹(mHz)甚至微赫兹(μHz)的分辨力,如果每个采样点都存储,则相应的波形数据存储容量也要做成2N。在实际中,由于受成本、功耗等诸多因素限制,不可能采用这么大的容量。为了节省波形存储空间,采用相位截断的办法,即只用相位累加器N位中的高M位来寻址波形查找表。如N=32,取M=12,将剩余的B位(B=N-M)截断不用,这样存储容量只需要2M,与2N相比,大大减少了存储容量。

采用相位截断,DDS输出频率仍然不变,其表达式仍为

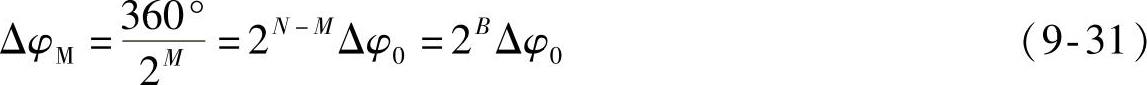

相位截断相当于对参考时钟fc先进行了2B分频,然后再对2M容量的波形存储器进行寻址。但是,通过相位截断后,DDS的最高相位分辨力ΔφM为

由此可见,相位截断牺牲了相位分辨力,但不影响频率分辨力。

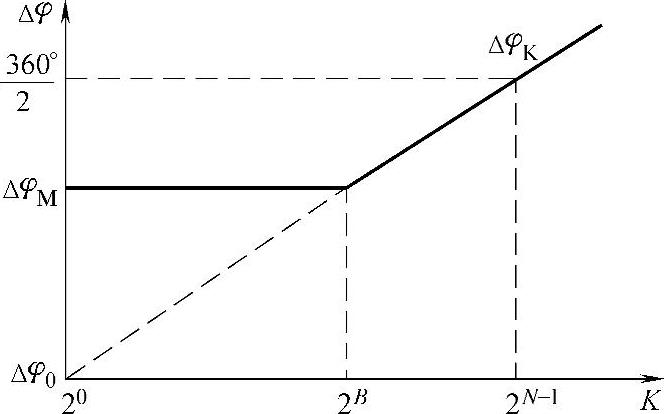

在没有相位截断的情况下,采用间隔采样的相位分辨力如式(9-29)所示,根据此式可给出一条ΔφK~K的变化曲线(倾斜的直线),如图9-36所示。同时,在图9-36中,也画出了ΔφM的曲线(与水平轴平行的直线)。式(9-29)和式(9-31)以及图9-36表明,当K=2B时,ΔφK=ΔφM。在采用了相位截断的情况下,采用间隔采样的相位分辨力将受到式(9-31)的限制,ΔφM是最高的相位分辨力。换句话说,当K≤2B时,Δφ=ΔφM=2BΔφ0,DDS的相位分辨力不随K值改变,即减小K值不会增加相位分辨力;当K>2B时,Δφ=ΔφK=KΔφ0,相位分辨力随K值增加而降低。

图9-36 在相位截断的情况下,DDS的相位分辨力与K的关系曲线

(3)D-A转换器

D-A转换器的作用是把合成的正弦波幅值的序列数字值转换成包络为正弦波的阶梯波。输出波形的质量取决于D-A的分辨率和转换速率。D-A转换器的位数越多,分辨率越高,DDS的幅度分辨率也越高,合成正弦波形的台阶就越多,信号波形越平滑,谐波分量越小,量化噪声越小,输出波形的精度就越高。D-A转换器的转换速率,决定了输出信号的最高工作频率。

若D-A转换`器的位数为n,参考电压为Ur,则DDS的幅度分辨率为

但幅度分辨力也不是越高越好,因为它必须使用高位数D-A转换器,这不但价格昂贵,而且工作速率明显下降,不利于输出频率的提高。此外,D-A转换器的位数大于波形存储器的容量也无意义。

欲获得连续平滑的输出信号,一个周期的波形应当采用更多的数据点来描述,即应相应地提高波形存储器的容量。一般说来,D-A转换器的位数最好能与波形存储容量相同。

(4)低通滤波器

在D-A转换器输出的包络为正弦形的阶梯波中,除主频fo外,还存在许多高次谐波和非谐波的高频分量,因此,为了取出主频fo,必须在D-A转换器的输出端接入低通滤波器,即可输出频率为fo的光滑的正弦波。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。