实验目的:使用FPGA电路板上的6位数码管以静态方式依次显示000000、111111、222222至FFFFFF,结束后继续从000000开始计数,每0.5 s变化一次。

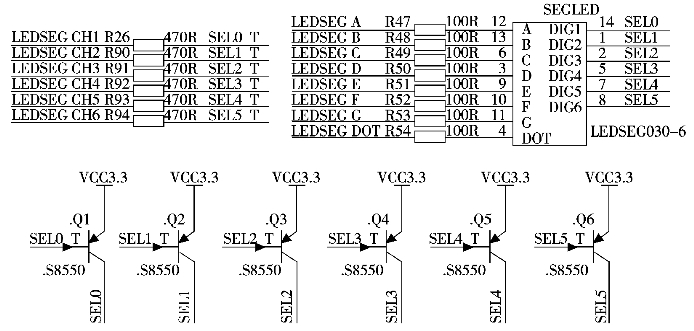

实验原理:数码管也称半导体数码管,它是将若干发光二极管按一定图形排列并封装在一起的一种数码显示器件。本次实验使用的是八段数码管,又称8字形数码管,可用来显示小数点、数字0~9和英文字母A~F。FPGA电路板上有6位共阳极数码管(每个二极管的阳极在数码管内部全部连接在一起而阴极独立),其原理图如图5-21所示。为了增加FPGA输出信号的驱动能力,使用PNP型三极管驱动数码管的位选段,所以给三极管基极提供低电平时,位选信号为高电平。

图5-21 数码管硬件原理图

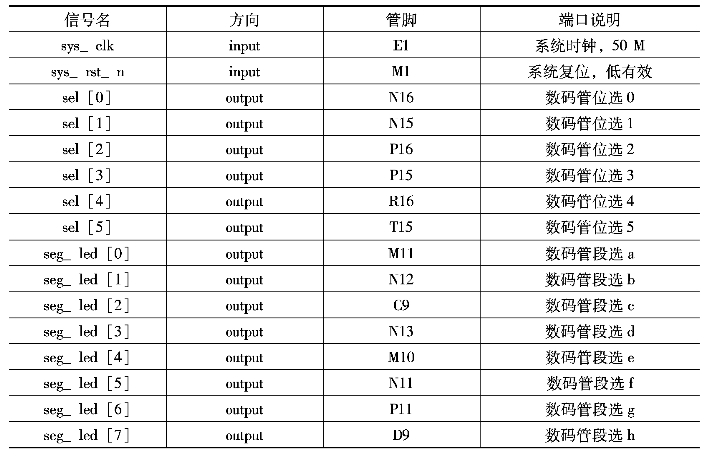

本实验中,各端口信号的管脚分配如表5-8所示。

表5-8 静态数码管显示实验管脚分配

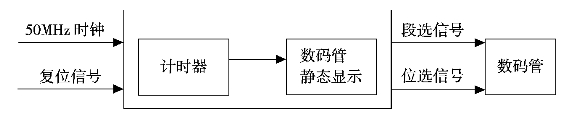

根据实验任务,我们可以大致规划出系统的控制流程:首先我们需要一个静态数码管显示模块在数码管上显示数据,其次需要一个计时模块每当计时到0.5 s时改变数码管显示的数值。由此画出系统的功能框图如图5-22所示。

图5-22 数码管静态显示实验系统框图

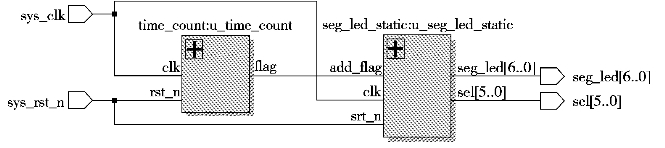

程序中各模块端口及信号连接如图5-23所示。

图5-23 顶层模块原理图

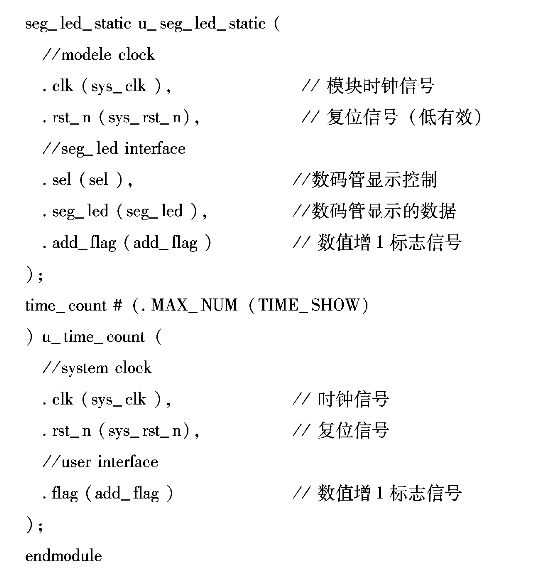

FPGA顶层(seg_led_static_top)例化了以下两个模块:计时模块(time_count)和数码管静态显示模块(seg_led_static),实现各模块之间数据的交互。计时模块将计时到0.5 s时的标志信号flag传递给数码管静态显示模块,数码管静态显示模块在数码管上以静态方式显示数值,接收到计时模块传递来的标志信号时显示的数值增加1。

实验流程:理解任务、分析原理、硬件设计、程序编码、仿真验证、具体实现。(https://www.xing528.com)

示例程序:

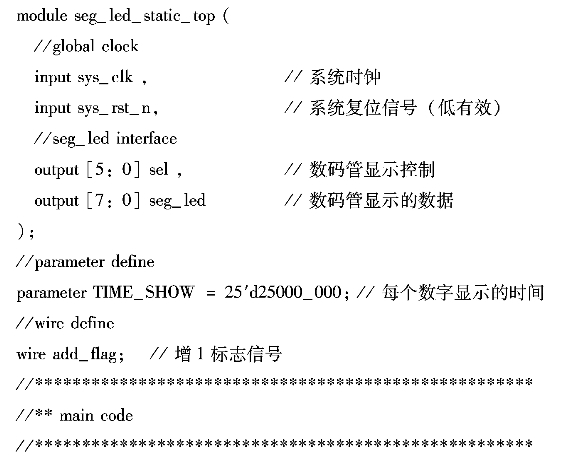

顶层模块主要完成对其余模块的例化,代码如下:

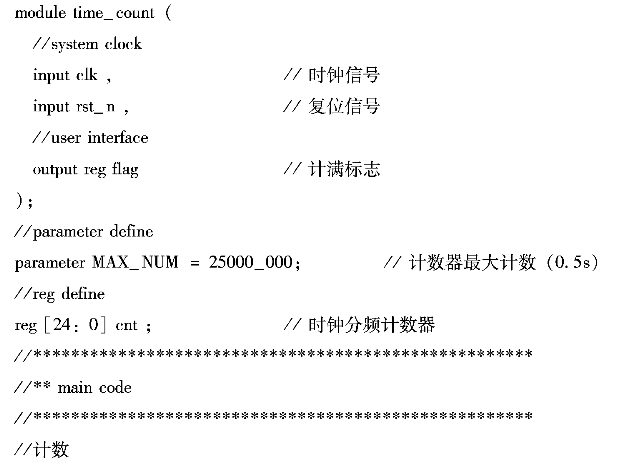

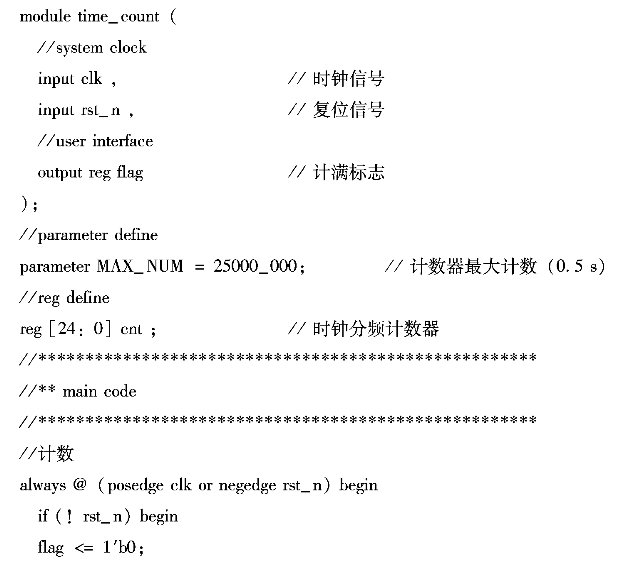

计时模块的代码如下所示:

计时模块的代码如下所示:

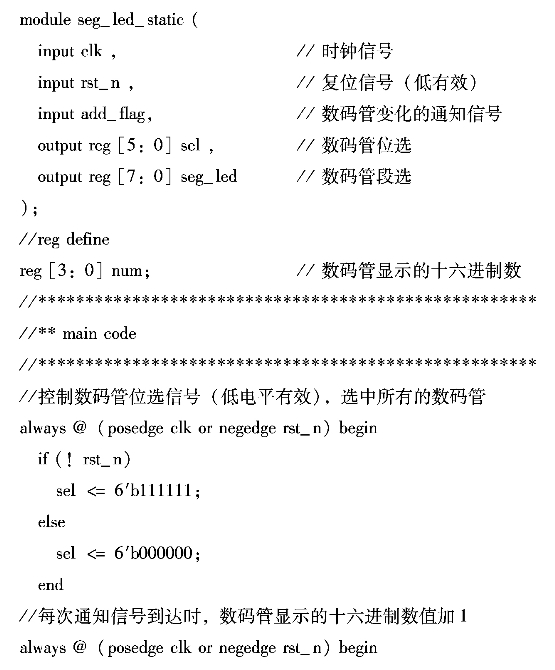

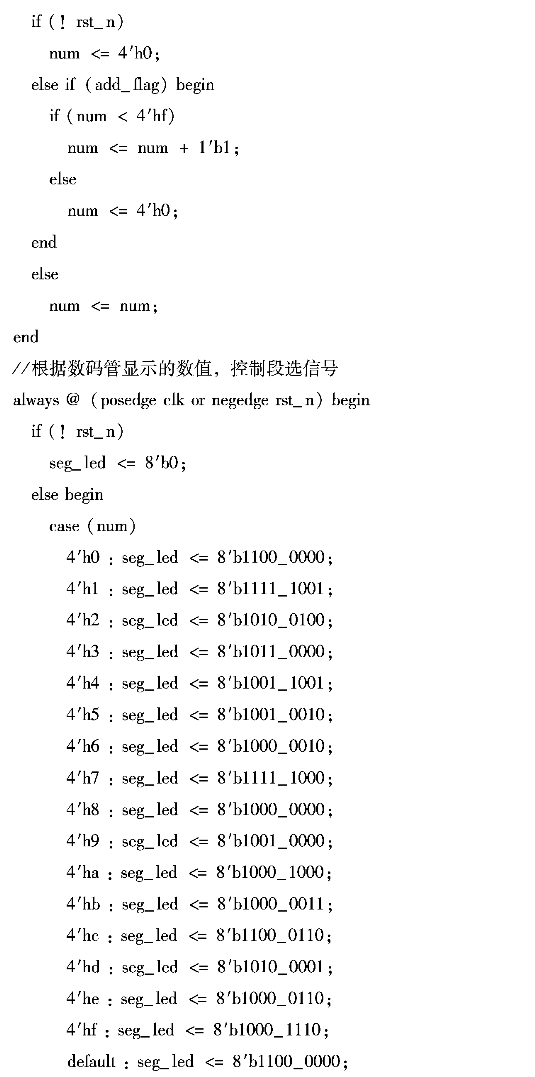

数码管静态显示模块的代码如下:

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。