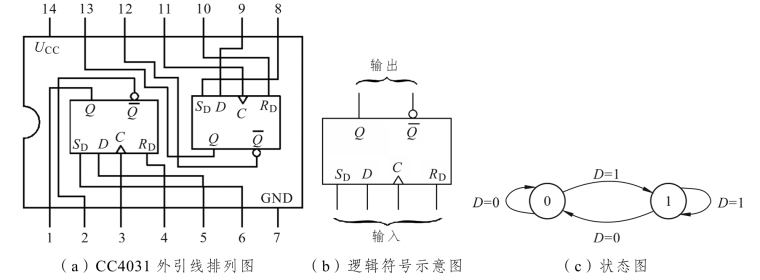

D 触发器逻辑部件CC4031 如图11.6 所示。

图11.5 时钟脉冲CP

图11.6 边沿型D 触发器

1.基本概念

输入端C:C 端的输入为CP 时钟信号,如图11.2(a)所示。图11.6(b)所示D 触发器为“上升沿”触发方式。

输入端D:数据信号由D 端输入,称为数据输入端。

输入端 SD、RD:图11.6(b)所示置位 SD和复位 RD为高电平有效。即当 SD=1、RD=0时,SD直接置位Q 状态为“1”;当 SD=0、RD=1时,RD直接复位Q 状态为“0”;当 SD=RD=0时,Qn+1状态由时钟信号CP 和输入数据D 决定。

注意:图11.6(b)所示触发器图的 SD、RD端“无小圆圈”,即高电平置位和复位;C 端“无小圆圈”,即CP 时钟信号上升沿触发。

2.逻辑功能、特性方程、状态图和时序波形图

1)逻辑功能

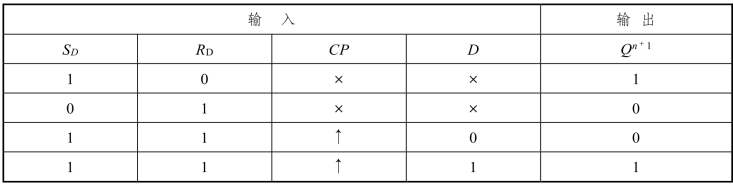

以图11.6(b)所示D 触发器逻辑符号为例,其功能如表11.2 所示。

表11.2 D 触发器功能表

注释:“↑”表示上升沿触发,即上升沿后产生新状态Qn+1。

由功能表11.2 可知,当 SD=RD=0时,在CP 的触发作用下,D 触发器的功能如下:

(1)当D=1时,Qn+1=D=1;

(2)当D=0时,Qn+1=D=0。(https://www.xing528.com)

2)特性方程

D 触发器的特性方程为

![]()

3)状态图

由功能表11.2 可知,当 SD=RD=0时,D 触发器的状态图如图11.6(c)所示。

4)时序波形图

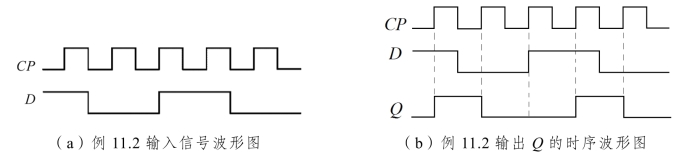

【例11.2】 已知图11.6(b)所示边沿型D 触发器的输入信号D、CP 如图11.7(a)所示,SD=RD=0,D 触发器的初始状态Q 为0。试画出输出Q 的时序波形图。

分析:

(1)已知 SD=RD=0;初始状态Q 为0;并由图11.6(b)可知CP 脉冲为上升沿触发。

(2)第1、4 个CP 上升沿前D=1,则Qn+1=D=1;第2、3、5 个CP 上升沿前D=0,则Qn+1=D=0。

解 根据表11.2 或特性方程式(11.2),画出相应的Q 的时序波形图11.7(b)。

图11.7 例11.2 时序波形图

结论:

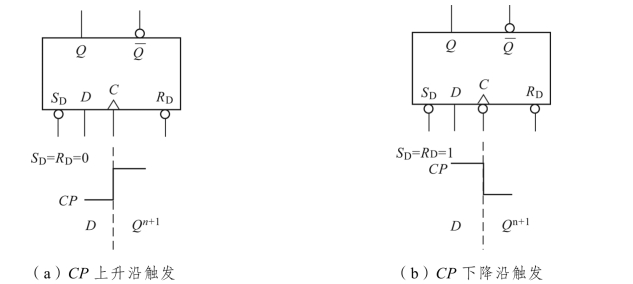

(1)图11.8(a)中 SD=RD=0[图11.8(b)中 SD=RD=1]时,状态Qn+1由输入信号D、CP 决定。

(2)D 触发器的CP 也分“上升沿”和“下降沿”两种触发方式,如图11.8(a)(b)所示。

(3)CP 触发沿前的输入信号D,决定触发沿后的新态Qn+1,即Qn+1=D,如图11.8(a)(b)所示。

图11.8 时钟脉冲CP

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。