1)计数器的功能和常见类型

计数器是数字电路中较为常用的基本逻辑器件,它不仅可用来记录脉冲数,还可以实现数字系统的定时、分频和执行数字运算等逻辑功能。计数器的长度是指计数器能够统计输入脉冲信号的最大数目,也称为计数器的模,用M表示。计数器的模就是电路的有效状态。计数器的种类很多,见表7.15。

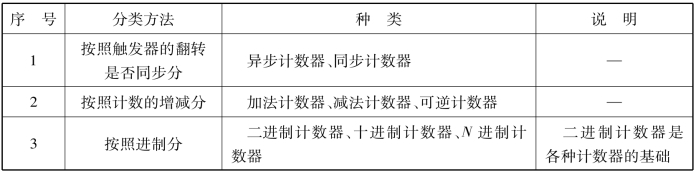

表7.15 计数器的种类

2)典型集成计数器

实际使用的计数器一般不需自己用单个触发器来构成,因为有许多TTL和CMOS专用集成计数器芯片可供选用。常用集成计数器型号有74LS161、74LS192、74LS290以及CD4040等。

【阅读窗】

集成计数器74LS163

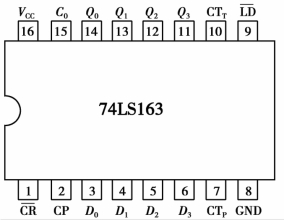

74LS163是集成4位二进制同步加法计数器,其引脚如图7.33所示,图中![]() 是同步清零端,

是同步清零端,![]() 是置数端,都是低电平有效;CTP和CTT是计数器工作状态控制端,CP是时钟脉冲端,D0~D3是输入端,C0是进位信号端,Q0~Q3是计数器输出端。

是置数端,都是低电平有效;CTP和CTT是计数器工作状态控制端,CP是时钟脉冲端,D0~D3是输入端,C0是进位信号端,Q0~Q3是计数器输出端。

图7.33 74LS163的引脚图

其逻辑功能如下:

①同步清零:当![]() 时,在CP脉冲上升沿的作用下,计数器清零,即Q3Q2Q1Q0=0000。

时,在CP脉冲上升沿的作用下,计数器清零,即Q3Q2Q1Q0=0000。

②同步置数:当![]() 时,在CP脉冲上升沿的作用下,计数器置数,即

时,在CP脉冲上升沿的作用下,计数器置数,即

![]() 。

。

③计数功能:当![]() 时,在时钟脉冲的作用下,计数器进行二进制加法计数。

时,在时钟脉冲的作用下,计数器进行二进制加法计数。

④保持功能:当![]() ,且CTT和CTP任何一个为0,计数器均保持原来的状态。

,且CTT和CTP任何一个为0,计数器均保持原来的状态。

【思考与练习】

一、填空题

1.实现____________的电路,称为编码器。

2.用________位二进制代码对________个信号进行编码的电路,称为二进制编码器。

3.将________________转换为____________的电路,称为二—十进制编码器。

4.___________是编码的逆过程。

5.实现____________的电路称为译码器。

6.将____________________译成________输出的电路称为二进制译码器。

7.对于共阴极接法的发光二极管数字显示器,应采用________电平驱动七段显示译码器。

8.用来统计输入脉冲个数的电路称为____________。

9.计数器的________是指计数器能够统计输入脉冲信号的最大数目,也称为计数器的________。

10.按照计数的增减可将计数器分为____________、___________和____________。

二、选择题(https://www.xing528.com)

1.对于8421BCD码编码器,下列说法正确的是( )。

A.有16根输入线,4根输出线

B.有10根输入线,4根输出线

C.有4根输入线,16根输出线

D.有4根输入线,10根输出线

2.对于8线—3线优先编码器,下列说法正确的是( )。

A.有8根输入线,3根输出线

B.有3根输入线,8根输出线

C.有8根输入线,8根输出线

D.有3根输入线,3根输出线

3.编码电路和译码电路中,( )电路的输出是二进制代码。

A.编码 B.译码 C.编码和译码 D.以上都不对

4.3线—8线译码电路是( )译码器。

A.二进制 B.三进制 C.三—八进制 D.八进制

5.用n个触发器构成计数器,可得到的最大计数长度为( )。

A.n B.2n C.2n D.n2

6.一个4位二进制减法计数器的起始值为1001,经过100个时钟脉冲作用之后的值为( )。

A.1100 B.0100 C.0101 D.1101

7.N进制计数器状态转换的特点是:设置初态后,每来( )个CP时,计数器又重回初态。

A.N﹣1 B.N+1 C.N2 D.N

8.计数器按照进制可分为( )。

A.加法、减法及加减可逆 B.同步和异步

C.N进制 D.二进制、十进制和N进制

【本章小结】

1.根据电路结构和工作原理的不同,数字电路可分为组合逻辑电路和时序逻辑电路两大类。

2.组合逻辑电路在任何时刻的输出都只取决于该时刻的输入,与之前的状态无关,具有即时性,因此它主要由基本门电路构成;而时序逻辑电路在任何时刻的输出不仅和该时刻的输入有关,而且还取决于电路原来的状态,因此时序逻辑电路须包含存储电路,存储电路又是由触发器构成的。

3.触发器有两个稳定状态,在输入信号的作用下,可以从一个稳定状态转变为另一个稳定状态。它常用特性表、特性方程、状态图和波形图来表示逻辑功能。

4.触发器按照逻辑功能可分为RS触发器、JK触发器、D触发器等;按照电路结构可分为基本触发器、主从触发器、边沿触发器等;按照触发方式又可分为电平触发和边沿触发。

5.组合逻辑电路的分析步骤:写出逻辑函数表达式→化简→列真值表→判断逻辑功能。组合逻辑电路的设计正好与其分析是相反的,其步骤为:列真值表→写出逻辑函数表达式→化简→画出逻辑图。

6.编码器和译码器是组合逻辑电路的典型应用,计数器是时序逻辑电路的典型应用。这些电路都已制作成相应的集成电路,须熟悉它们的逻辑功能才能灵活应用。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。