1)时序逻辑电路的概念

时序逻辑电路又称为时序电路,它是指任意时刻电路的输出不仅取决于该时刻电路的输入,而且还取决于电路之前的状态。我们把这类具有存储、记忆功能的电路称为时序逻辑电路。

2)时序逻辑电路的构成

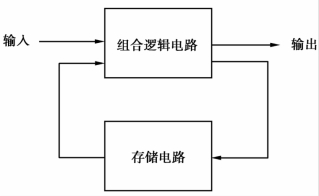

时序逻辑电路是由组合逻辑电路和存储电路构成的,而存储电路是由触发器构成的,因此我们可以用触发器的现态和次态来表示时序逻辑电路的现态和次态。另外,存储电路的输出必须反馈到输入端,与输入信号共同决定电路的输出。图7.19为时序逻辑电路的构成示意框图。

图7.19 时序逻辑电路的构成示意框图

数字电路中的数码寄存器、计数器、存储器等都是时序电路的基本单元电路。

时序逻辑电路的结构特点:除含有组合电路外,时序电路还含有存储信息的有记忆能力的触发器、寄存器、计数器等电路。

3)时序逻辑电路的种类

根据电路状态转换的时刻不同,时序逻辑电路可分为同步时序电路和异步时序电路。同步时序电路中,所有触发器的时钟控制端CP都连在一起,即在同一个时钟脉冲的控制下,触发器的状态转换和时钟脉冲是同步的。而在异步时序电路中,没有统一的时钟信号,即触发器的状态变化有先后,并不是和时钟脉冲CP同步的。

【思考与练习】

一、填空题

1.触发器有____________稳定的状态,分别是____________和____________。

2.由两个与非门构成的基本RS触发器的特性方程是____________,约束条件是____________。

3.同步RS触发器状态的改变是与____________信号同步的。

4.在CP有效期间,如果同步触发器的输入信号发生多次变化,其输出也会跟着发生多次变化,这种现象称为_____________。

5.边沿JK触发器的特性方程是__________,边沿D触发器的特性方程是__________。

6.将JK触发器的J端和K端直接相连作为输入端时,JK触发器可转换为________触发器。

7.将D触发器的D端与Q端直接相连时,D触发器可转换为成____________触发器。

8.时序逻辑电路任何时刻的输出信号不仅取决于________________,还取决于____________。

二、选择题

1.对于触发器和组合逻辑电路的区别,以下说法正确的是( )。

A.两者都有记忆能力 B.两者都无记忆能力

C.只有触发器有记忆能力 D.只有组合逻辑电路有记忆能力

2.对于JK触发器,输入J=0,K=1,CP脉冲作用后,触发器的Qn+1应为( )。

A.1 B.0(https://www.xing528.com)

C.可能是0,也可能是1 D.与Qn有关

3.具有“置0”“置1”“保持”“翻转”功能的触发器叫( )。

A.JK触发器 B.基本RS触发器 C.D触发器 D.同步RS触发器

4.只具有“保持”“翻转”功能的触发器叫( )。

A.JK触发器 B.RS触发器 C.D触发器 D.T触发器

5.D触发器用作T′触发器时,输入端D的正确接法是( )。

![]()

6.时序逻辑电路中一定包含( )。

A.移位寄存器 B.触发器 C.加法器 D.译码器

7.时序逻辑电路中必须有( )。

A.数值比较器 B.计数器 C.时钟信号 D.编码器

8.时序电路某一时刻的输出状态,与该时刻之前的电路状态( )。

A.有关 B.无关 C.有时有关,有时无关 D.以上都不对

三、判断题

1.触发器属于组合逻辑电路。( )

2.触发器有两个稳定状态,一个是现态,一个是次态。( )

3.时钟脉冲的主要作用是使触发器的输出状态稳定。( )

4.基本RS触发器和同步RS触发器的特性是完全相同的。( )

5.仅具有翻转功能的触发器是T′触发器。( )

6.RS触发器、JK触发器、D触发器和T触发器,只有RS触发器存在输入信号的约束条件。( )

7.所谓下降沿触发,是指触发器的输出状态变化是发生在CP=1期间。( )

8.同步时序逻辑电路和异步时序逻辑电路的区别在于异步时序逻辑电路没有稳定的状态。( )

四、分析计算题

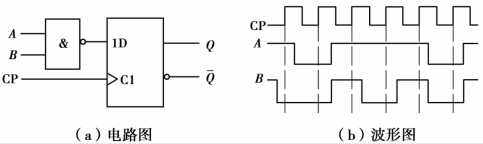

电路如图7.20(a)所示,输入CP、A、B的波形如图7.29(b)所示,试画出Q端的波形(设初始状态Q=0)。

图7.20

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。