在CP时钟脉冲作用下,输出信号由输入信号D来决定,且具有置1、置0功能的电路,称为D触发器。D触发器可以分为同步D触发器和边沿D触发器。

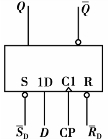

1)边沿D触发器的逻辑符号

边沿D触发器的逻辑符号如图7.13所示,D为输入端,CP为时钟脉冲控制端,方框图中CP一端标有“∧”表示在脉冲上升沿有效。![]() 和

和![]() 为直接复位端和直接置位端,都是低电平有效。

为直接复位端和直接置位端,都是低电平有效。

图7.13 边沿D触发器逻辑符号

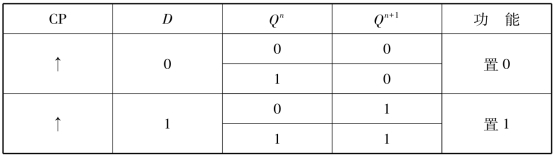

2)边沿D触发器的特性表

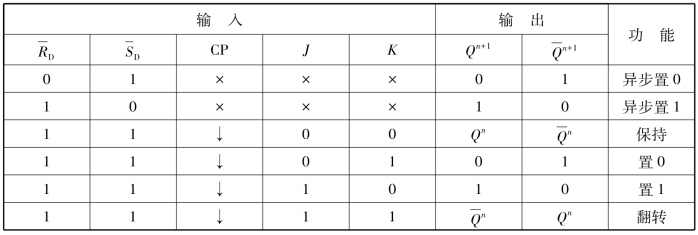

边沿D触发器的逻辑功能可用特性表7.6来描述。

表7.6 边沿D触发器的特性表

从表7.6中可看出在CP上升沿时:

①D=0,触发器置0,即Qn+1=0。

②D=1,触发器置1,即Qn+1=1。

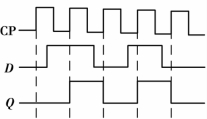

3)边沿D触发器的波形图

图7.14为边沿D触发器的波形图,图中触发器的初始态为0状态,在CP脉冲的每一个上升沿,输出信号Q都由输入信号D来决定。

图7.14 D触发器的波形图

同步D触发器的逻辑功能与边沿D触发器基本一致,只是对时钟脉冲CP的要求不一样,在此我们将不再赘述。

【阅读窗】(https://www.xing528.com)

集成触发器

集成触发器种类很多,但在实际电路中,用得较多的是JK触发器和D触发器,下面着重介绍集成JK触发器74LS112和集成D触发器74LS74。

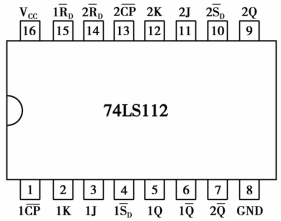

(1)集成JK触发器74LS112

集成JK触发器74LS112共有16个管脚,上面集成了两个带有异步置0和异步置1功能的边沿JK触发器,下降沿触发,其引脚排列如图7.15所示,所能实现的功能如表7.7所示。

图7.15 集成JK触发器74LS112的引脚排列

表7.7 集成JK触发器74LS112逻辑功能表

其中,×为任意值,既可取1又可取0。

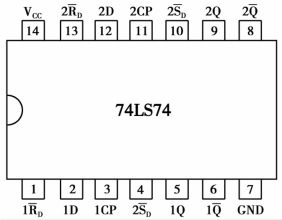

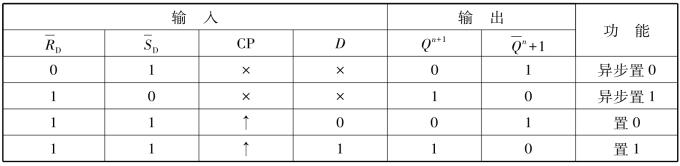

(2)集成D触发器74LS74

集成D触发器74LS74共有14个管脚,上面集成了两组上升沿触发的边沿D触发器,其引脚排列如图7.16所示,所能实现的功能见表7.8。

图7.16 集成D触发器74LS74的引脚排列

表7.8 集成D触发器74LS74逻辑功能表

注:表中×为任意值,既可取1又可取0。

在使用集成触发器时,要会判断集成器的引脚序号,这样才能知道相应引脚的功能,因此可以将集成器芯片的缺口朝左放置,那么引脚序号是按照逆时针从小到大排列,即左下脚为1号引脚,依次类推。另外,在使用集成触发器时,除了了解其性能参数外,主要就是掌握触发器的逻辑功能和外部引脚的作用,能够正确连线。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。