1.基本原理

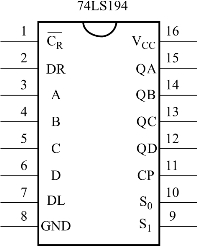

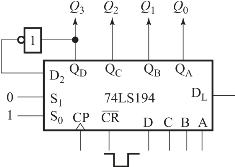

四位双向移位寄存器74LS194逻辑功能示意图如图6-43所示。

图6-43 四位双向移位寄存器74LS194逻辑功能示意图

2.真值表(简表)

四位双向移位寄存器74LS194功能真值表如表6-11所示。

表6-11 四位双向移位寄存器74LS194功能真值表

3.构成扭环形计数器

采用四位双向移位寄存器74LS194构成扭环形计数器的逻辑电路如图6-44所示。

图6-44 74LS194构成扭环形计数器的逻辑电路

(a)采用右移方式构成扭环形计数器;(b)采用左移方式构成扭环形计数器

4.构成奇数分频器

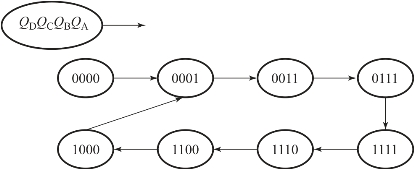

采用四位双向移位寄存器74LS194构成奇数分频器的逻辑电路如图6-45所示,七分频电路状态转换图如图6-46所示。

图6-45 74LS194构成奇数分频器的逻辑电路(七分频电路)

图6-46 74LS194构成奇数分频器(七分频电路)状态转换图

先导案例解决

日常生活中钟表的正常走时规律是:秒针正常走时1 Hz,当秒针走时60次时,分针走时1次,当分针走时60次时,时针走时1次,一天正常走时24 h。采用数字电路的解决方案就是:选用1 Hz的时钟脉冲作为秒计数器的输入信号,将秒计数器设计为六十进制计数器,当正常走时至60 s时同时进位给分计数器,将分计数器也设计为六十进制计数器,当正常走时至60 min时同时进位给时计数器,将时计数器设计为二十四进制计数器,从而实现钟表的正常走时。

任务训练

十六进制递加、递减计数器的设计(按自然态序变化)。

1.实验目的

掌握74LS74、74LS112集成触发器构成二进制计数器的方法。

2.实验器材

万用表、数字电路实验箱、74LS74、74LS112、导线(若干)。

3.实验内容及步骤

1)四位二进制(十六进制)递加计数器的设计

(1)按图6-47所示进行电路连线,并将计数器的时钟信号接单次脉冲源,输出信号接逻辑电平指示灯,同时将74LS112的直接置位端和直接复位端接高电平“1”。

图6-47 74LS112构成十六进制异步加计数器

(2)依次送入单次脉冲,观察电路输出逻辑电平指示灯是否从0000依次递加变化到1111,即实现十六进制加计数。

(3)根据逻辑电平指示灯的变化,画出状态转换图。

2)四位二进制(十六进制)递减计数器的设计

(1)如图6-48所示,进行电路连线,并将计数器的时钟信号接单次脉冲源,输出信号接逻辑电平指示灯,同时将74LS74的直接置位端和直接复位端接高电平“1”。

(2)依次送入单次脉冲,观察电路输出逻辑电平指示灯是否从1111依次递减变化到0000,即实现十六进制减计数。

(3)根据逻辑电平指示灯的变化,画出状态转换图。

图6-48 74LS74构成十六进制异步减计数器

任务拓展

试使用1个74LS74和1个74LS112分别构成十六进制加计数器和十六进制减计数器。

一、可预置四位二进制同步计数器74LS161(十六进制)的应用

1.实验目的

(1)熟悉74LS161的逻辑功能及使用方法。

(2)通过实验掌握用74LS161的反馈复位法和反馈预置法构成十进制、六进制等任意进制计数器的方法。

2.实验器材

万用表、数字电路实验箱、74LS161、74LS00、导线(若干)。

3.实验内容及步骤

1)74LS161采用反馈复位法构成十进制计数器的设计与调试

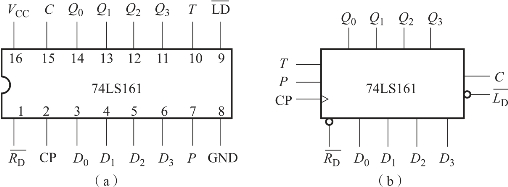

74LS161引脚图和逻辑功能示意图如图6-49所示,其功能真值表如表6-12所示。

图6-49 74LS161引脚图和逻辑功能示意图

(a)74LS161引脚图;(b)74LS161逻辑功能示意图

表6-12 74LS161功能真值表

(1)可预置四位二进制同步计数器74LS161采用反馈复位法构成十进制计数器的逻辑电路,如图6-50所示,按图接线并将CP接单次脉冲源,输出信号接数码管。

图6-50 74LS161反馈复位法构成十进制计数器的逻辑电路

(2)依次送入单次脉冲,观察数码管是否从0到9进行加计数。

2)74LS161采用反馈预置法构成六进制计数器的设计与调试

(1)可预置四位二进制同步计数器74LS161采用反馈预置法构成六进制计数器的逻辑电路,如图6-51所示,按图接线并将CP接单次脉冲源,输出信号接数码管。

图6-51 74LS161反馈预置法构成六进制计数器的逻辑电路

(2)依次送入单次脉冲,观察数码管是否从0到5进行加计数。(https://www.xing528.com)

二、双四位二进制同步计数器CD4520(十六进制)的应用

1.实验目的

(1)熟悉CD4520的逻辑功能及使用方法。

(2)通过实验掌握用CD4520构成六十进制等任意进制计数器的实现方法。

2.实验器材

万用表、数字电路实验箱、CD4520、74LS00、导线(若干)。

3.实验内容及步骤

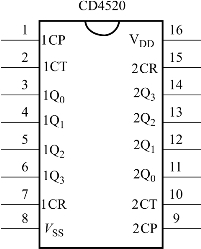

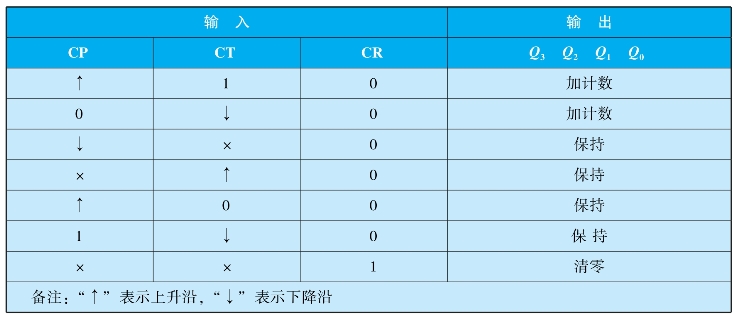

双四位二进制同步计数器CD4520构成六十进制计数器的设计与调试CD4520功能引脚图如图6-52所示,其功能真值表如表6-13所示。

图6-52 CD4520功能引脚图

表6-13 CD4520功能真值表

(1)CD4520构成六十进制计数器的逻辑电路如图6-53所示,按图接线,将计数器个位的时钟信号CP接单次脉冲源,输出信号个位和十位分别接数码管。

图6-53 CD4520构成六十进制计数器的逻辑电路

(2)依次送入单次脉冲或1 Hz脉冲信号源,观察数码管的变化是否从0到59进行加计数。

4.任务完成结论

如果个位的进位信号不是送到十位的“CT”而是送到“CP”,将出现什么结果?请用实验回答。

图6-54 74LS194引脚图

三、移位寄存器74LS194的功能测试及应用

1.实验目的

(1)掌握74LS194四位双向移位寄存器的逻辑功能。

(2)掌握74LS194的典型应用。

2.实验器材

万用表、数字电路实验箱、双踪示波器、74LS194、74LS00、导线(若干)。

3.实验方法及步骤

1)74LS194的功能测试

74LS194引脚图如图6-54所示,其功能真值表如表6-14所示。

表6-14 74LS194功能真值表

按图6-55所示进行连线,并设置S1=S0=1,清零端![]() 接逻辑电平开关,输入D3~D0接逻辑电平开关,输出Q3~Q0接逻辑电平指示灯,CP接时钟脉冲源,按表6-15进行实验,将结果填入表中,并总结送数方法。

接逻辑电平开关,输入D3~D0接逻辑电平开关,输出Q3~Q0接逻辑电平指示灯,CP接时钟脉冲源,按表6-15进行实验,将结果填入表中,并总结送数方法。

图6-55 74LS194功能测试原理图

表6-15 74LS194功能测试表

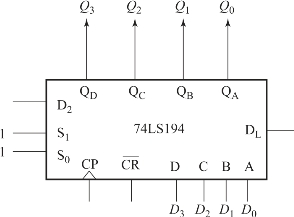

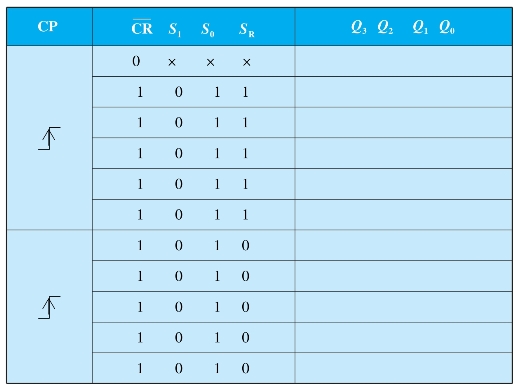

2)74S194右移功能

按图6-55进行连线,并设置S1=0,S0=1,S R为尾添加数据,按表6-16进行实验,将结果填入表中,并分析右移的过程。

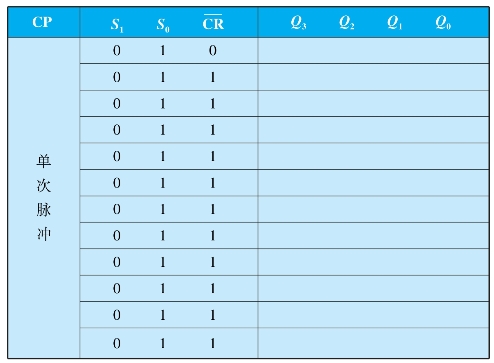

表6-16 74LS194右移功能测试表

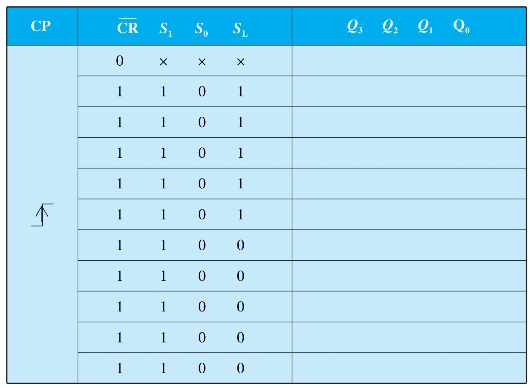

3)74S194左移功能

按图6-55进行连线,并设置S1=1,S0=0,S L为尾添加数据,按表6-17进行实验,将结果填入表中,并分析左移的过程。

表6-17 74LS194左移功能测试表

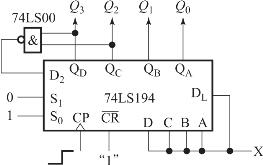

4)74LS194构成扭环形计数器

(1)74LS194采用右移方式构成扭环形计数器的逻辑电路如图6-56所示,控制方式选择S1 S0=01,将输出接逻辑电平开关,并将输出最高位Q3经“非门”(采用74LS00与非门实现)反馈送到D R端,清零信号端![]() 加的负脉冲作用过后就消失。在单次时钟脉冲CP作用下将进行右移操作。

加的负脉冲作用过后就消失。在单次时钟脉冲CP作用下将进行右移操作。

图6-56 74LS194构成扭环形计数器的逻辑电路

(2)按表6-18进行实验,分析电路功能,说明计数器的(有效)模长。

(3)思考:如要求采用左移方式同样实现扭环形计数,电路应做如何改变,请画出电路图。

表6-18 74LS194构成扭环形计数器状态转换真值表

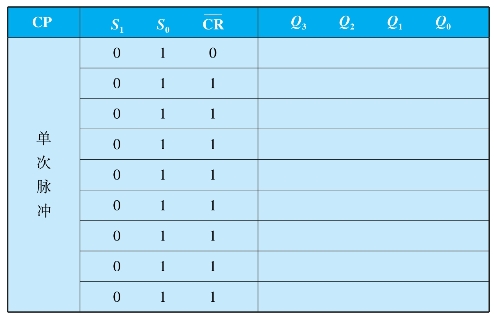

5)74LS194构成奇数分频器

74LS194构成奇数分频器的逻辑电路如图6-57所示,控制方式选择S1 S0=01,将Q3Q2两端经“与非门”反馈至D R端,按表6-19进行实验,并画出Q3 Q2 Q1 Q0的波形分析。

图6-57 74LS194构成奇数分频器的逻辑电路

表6-19 74LS194构成奇数分频器状态转换真值表

4.任务完成结论

(1)如果将图6-57所示的反馈方式变为Q1Q0经“与非门”反馈到D R端,其他不变,重复上述过程,并记录实验结果,试分析电路的功能。

习题6.5

(2)如果CP端输入10 kHz连续脉冲,用示波器观察Q3Q2Q1Q0的波形并记录。

(3)思考奇数分频器分频与反馈方式之间的关系是什么?

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。