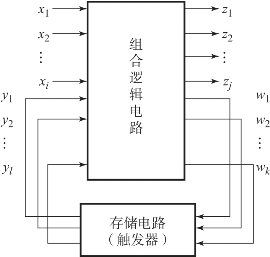

【摘要】:图6-1时序逻辑电路结构框图除有组合逻辑电路外,时序逻辑电路中还有触发器等器件构成的存储电路,因此具有记忆过去输入信号的功能;存储电路的状态(图6-1中的y1、y2…这些信号之间的逻辑关系可以用下列三个方程来表示。

时序逻辑电路结构框图如图6-1所示,与组合逻辑电路相比较,时序逻辑电路在结构上有下列两个特点:

图6-1 时序逻辑电路结构框图

(1)除有组合逻辑电路外,时序逻辑电路中还有触发器等器件构成的存储电路,因此具有记忆过去输入信号的功能;

(2)存储电路的状态(图6-1中的y1、y2…yl)反馈到输入端,与输入信号共同决定其组合部分的输出(图6-1中的z1、z2…zj)。

在图6-1中,时钟信号省略,X(x1,x2,…,xi)代表输入信号,Z(z1,z2,…,zj)代表输出信号,W(w1,w2,…,wk)代表存储电路的驱动信号,Y(y1,y2,…,yl)代表存储电路的输出状态。这些信号之间的逻辑关系可以用下列三个方程来表示。(https://www.xing528.com)

X(x1,x2,…,xi)——输入信号 Z(z1,z2,…,zj)——输出信号

W(w1,w2,…,wk)——驱动信号 Y(y1,y2,…,yl)——输出状态

驱动方程:W(tn)=H[X(tn),Y(tn)]

状态方程:Y(tn+1)=G[W(tn),Y(tn)]

输出方程:Z(tn)=F[X(tn),Y(tn)]

方程中的tn、tn+1表示两个相邻的离散时间,Y(tn)一般表示存储电路各触发器输出的现时状态,简称现态或初态;Y(tn+1)则描述了存储电路下一个工作周期(来过一个时钟脉冲以后)的状态,简称次态。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。