4位二进制数比较器,也称4位数值比较器。比较两个n位数的大小时,应该从高向低逐位比较,某位出现大小区别时,更低位就不用再比较,而直接得到两个数的大小关系。只有在高位相等时,才需要比较低位,如果两个数的各数位均相等,则给出两个数相等的比较结果。

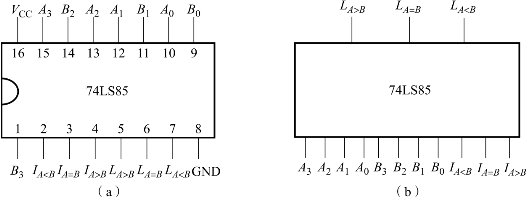

目前,常用的集成数值比较器有4位数值比较器74LS85。其芯片引脚图和逻辑符号如图4-40所示。A3 A2 A1 A0、B3 B2 B1 B0为两个待比较的4位二进制数输入端,LA>B、LA=B、LA<B是总的比较结果输出端。另外,为了芯片间连接以实现比较器位数的扩展,还设置了3个扩展端IA>B、IA=B、IA<B。

图4-40 74LS85引脚图和逻辑符号

(a)74LS85引脚图;(b)74LS85逻辑符号

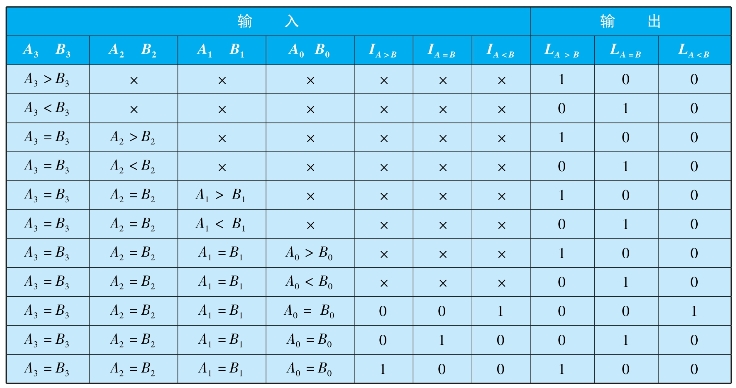

观察表4-16数值比较器74LS85功能表,不难发现,当A3=B3、A2=B2、A1=B1、A0=B0时,输出结果由级联输入端输入信号决定,有三种可能。而在其他情况下,则高四位就可决定A>B还是A<B,其最后输出与扩展输入端无关。

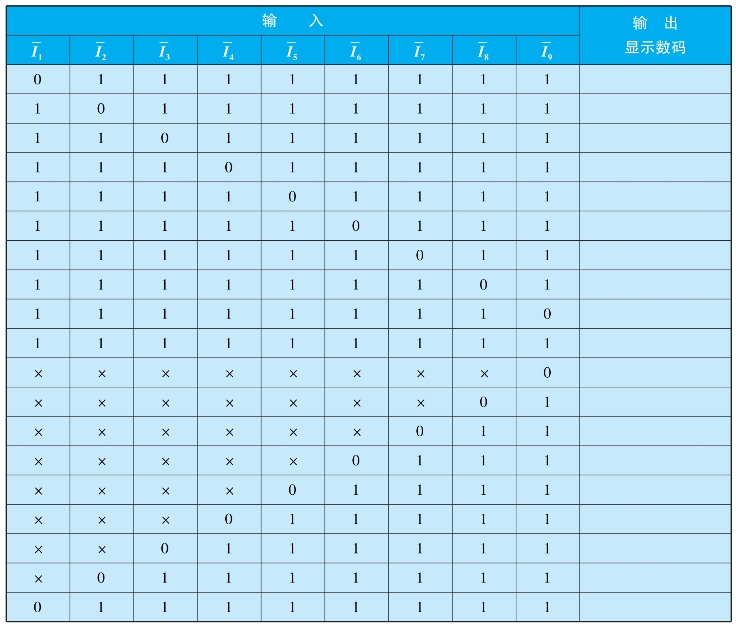

表4-16 数值比较器74LS85功能表

注:表中“×”表示任意逻辑值。

74LS85逻辑功能测试

加扩展输入端的作用是为了芯片的扩展应用,图4-41所示为两片74LS85连接构成的8位二进制数值比较器的电路图。

图4-41 8位二进制数值比较器的电路图

根据多位数比较时从高到低比较的原则,将8位数分为高4位和低4位。两个数的高4位A7 A6 A5 A4、B7 B6 B5 B4接入片Ⅱ(高位片)输入端。两个数的低4位A3 A2 A1 A0、B3 B2 B1 B0接入片Ⅰ(低位片)输入端。低位片的三个输出端LA>B、LA=B、LA<B对位接到高位片的级联输入端IA>B、IA=B、IA<B,8位数值比较结果从高位片的输出端LA>B、LA=B、LA<B输出。

如果两个数的高4位已经有了确定的大小,则不论高位片的级联输入端为多少,直接给出A>B或者A<B的输出结果;如果高4位相同,则输出根据高位片的级联输入端取值决定。而高位片的级联输入端接入的正是低位片的比较结果,等于将低位比较结果通过这样的级联输入传送到电路的输出端。

注意:

低位片的级联输入端IA>B、IA=B、IA<B应该分别接0、1、0,这样如果两个数完全相等,输出端也就可以正确给出A=B的比较结果。

先导案例解决

在数字系统中处理和运算的数据都是二进制,而人们日常生活中使用的都是十进制数,编-译-显电路可以实现这种转换,所以在数字电路中被广泛地应用。电路首先通过编码器将十进制数进行编码,然后将生成的编码信号通过译码驱动器进行译码,输出a,b,c,d,e,f,g七段码去驱动LED数码管,并在数码管上显示编码对应的十进制数字。具体电路可以选用本章中介绍的优先编码器74LS147、译码驱动器CD4511和数码管来实现,需要注意的是74LS147的输出端DCBA是反码输出,所以DCBA需要经过四个非门再送入CD4511的输入端,同时CD4511的三个使能端LE、 、

、 设为0、1、1。

设为0、1、1。

任务训练

一、译码器的应用

1.实验目的

(1)熟悉3线-8线译码器74LS138的基本功能。

(2)掌握3线-8线译码器74LS138的应用。

2.实验器材

(1)74LS138:3线-8线译码器。

(2)74LS20:二-4输入与非门。

(3)万用表、数字电路实验箱、导线(若干)。

3.实验内容及步骤

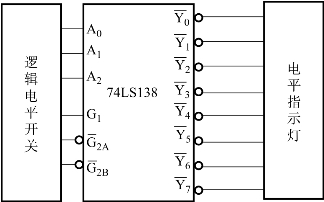

1)74LS138逻辑功能测试

(1)测试电路线路连接。按图4-42所示完成连线。连接芯片74LS138电源线(5 V)、地线。连接输入输出信号线:芯片的输入端(译码输入端:A2 A1 A0,使能端:![]() )分别接实验箱6个电平开关,输出端(译码输出端

)分别接实验箱6个电平开关,输出端(译码输出端![]() )分别接8个电平指示灯。74LS138芯片引脚图如图4-16(b)所示。

)分别接8个电平指示灯。74LS138芯片引脚图如图4-16(b)所示。

图4-42 74LS138逻辑功能测试连线图

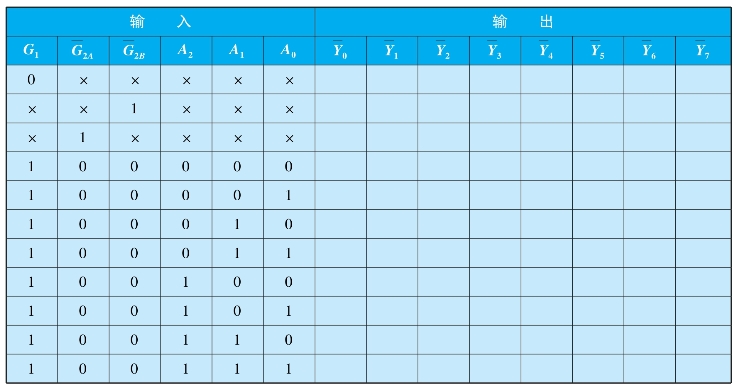

(2)测试。使能输入端![]() 、译码输入端A2 A1 A0按表4-17所示依次分别送入11组逻辑值,观察输出端

、译码输入端A2 A1 A0按表4-17所示依次分别送入11组逻辑值,观察输出端![]() 的输出逻辑值并记录在表4-17输出栏中。

的输出逻辑值并记录在表4-17输出栏中。

表4-17 74LS138功能真值表

2)构成函数发生器

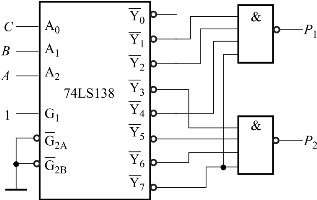

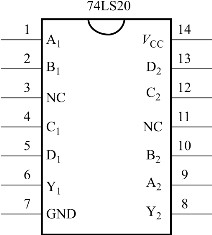

用74LS138及与非门74LS20构成1位全加器,按图4-43接线。74LS20芯片引脚图如图4-44所示。

图4-43 74LS138实现全加器电路

图4-44 74LS20芯片引脚图

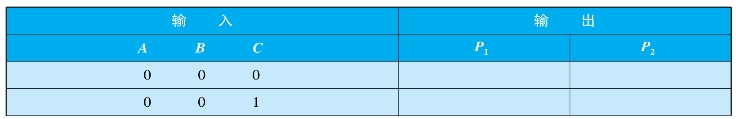

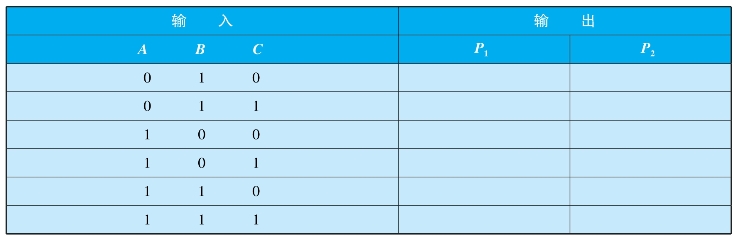

按表4-18分别输入逻辑值并记录P1和P2输出逻辑值。

表4-18 74LS138实现全加器电路

续表

4.任务完成结论

(1)当![]() =100时,译码输入A2 A1 A0=000,译码输出

=100时,译码输入A2 A1 A0=000,译码输出![]() =_ __ __ __ __ __ __ _,即译码输出结果为_ __ __ ___ _,输出_ __ __ ___ _(高/低)电平有效。A2 A1 A0分别为:001,010,100,101,110,111时译码输出结果分别为__________, ___ __ __ __ _, ___ __ __ __ _,__________,_ __ __ __ __ _, 。

=_ __ __ __ __ __ __ _,即译码输出结果为_ __ __ ___ _,输出_ __ __ ___ _(高/低)电平有效。A2 A1 A0分别为:001,010,100,101,110,111时译码输出结果分别为__________, ___ __ __ __ _, ___ __ __ __ _,__________,_ __ __ __ __ _, 。

(2)当使能端输入不满足![]() =100时,译码输出

=100时,译码输出![]() _________(0/1),即译码器74LS138____________(不译码/正常译码)。

_________(0/1),即译码器74LS138____________(不译码/正常译码)。

(3)根据表4-18,写出P1=____________,P2=____________。其中P1为____________(和/进位),P2为____________(和/进位)。

二、数据选择器的应用

1.实验目的

(1)熟悉8选1数据选择器74LS151的基本功能。

(2)掌握8选1数据选择器74LS151的应用。

2.实验器材

(1)74LS151:8选1数据选择器。

(2)万用表、数字电路实验箱、导线(若干)。

3.实验内容及步骤

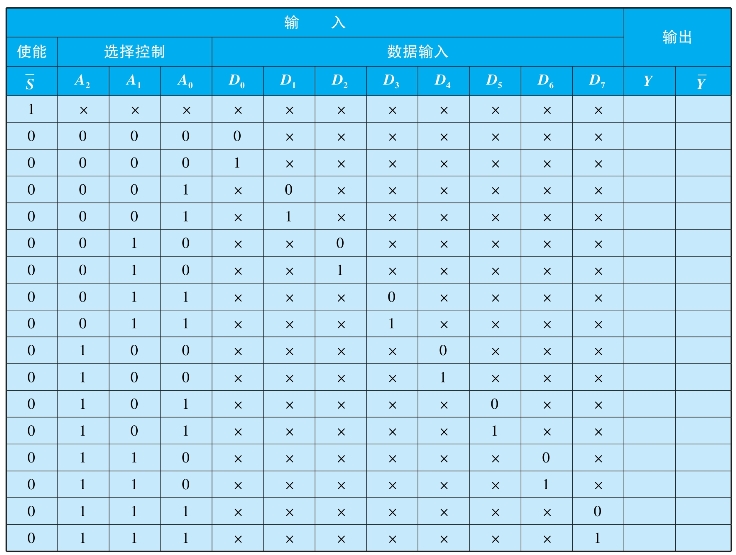

1)数据选择器74LS151的数据选择功能测试

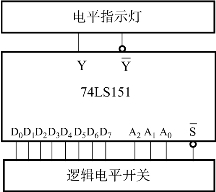

图4-45 74LS151逻辑功能测试连线图

(1)测试电路线路连接。按图4-45所示完成连线。连接芯片74LS151电源线(5 V)、地线。连接输入输出信号线;芯片输入端(数据输入端D0~D7),选择控制端A2 A1 A0,使能端 分别接实验箱12个电平开关,数据输出端Y、

分别接实验箱12个电平开关,数据输出端Y、 分别接2个电平指示灯。74LS151芯片引脚图如图4-29(a)所示。(https://www.xing528.com)

分别接2个电平指示灯。74LS151芯片引脚图如图4-29(a)所示。(https://www.xing528.com)

(2)测试。使能端 、数据输入端D0~D7按表4-19依次输入逻辑值,观察输出端逻辑值并记录在表4-19输出栏中。

、数据输入端D0~D7按表4-19依次输入逻辑值,观察输出端逻辑值并记录在表4-19输出栏中。

表4-19 74LS151功能真值表

2)数据选择器74LS151的并-串转换功能测试

使能端 送入逻辑值0,数据输入端D0~D7按表4-20并行送入数据“01100001”,选择控制端A2 A1 A0依次送入000,001,…,111等数据,观察输出端逻辑值并记录在表4-20输出栏中。

送入逻辑值0,数据输入端D0~D7按表4-20并行送入数据“01100001”,选择控制端A2 A1 A0依次送入000,001,…,111等数据,观察输出端逻辑值并记录在表4-20输出栏中。

表4-20 74LS151并-串转换功能测试

4.任务完成结论

(1)当数_据选择器74LS151使能端 =0时,选择控制端A2 A1 A0=000,当D0=0时,Y=________,

=0时,选择控制端A2 A1 A0=000,当D0=0时,Y=________, =________;当D0=1时,Y=__________,

=________;当D0=1时,Y=__________, =__________,即Y=__________,

=__________,即Y=__________, =________,此时D1~D7_________(影响/不影响)输出逻辑值。当A2 A1 A0分别为:001,010,011,100,101,110,111时译码输出逻辑值分别为________,_____,______,_ __ __ _, ___ __ _,_ __ __ _, ___ __ _,即输出信号为在选择控制信号作用下从多个输入数据中选出一个输出。

=________,此时D1~D7_________(影响/不影响)输出逻辑值。当A2 A1 A0分别为:001,010,011,100,101,110,111时译码输出逻辑值分别为________,_____,______,_ __ __ _, ___ __ _,_ __ __ _, ___ __ _,即输出信号为在选择控制信号作用下从多个输入数据中选出一个输出。

(2)当数据选择器74LS151使能端 =1时,输出端Y=______,

=1时,输出端Y=______, =______,即数据选择器________(工作/不工作),因此使能端

=______,即数据选择器________(工作/不工作),因此使能端 为 ___ _(高/低)电平有效。

为 ___ _(高/低)电平有效。

(3)当数据选择器74LS151正常工作时,要实现数据的并-串转换,数据输入端要并行送入数据D0~D7,选择控制端要依次先后送入数据000~111,则输出端Y依次串行输出为______、_ __ __ _、 ___ __ _、 ___ __ _、 ___ __ _、 ___ __ _、_ __ __ _、_ __ __ _,即D0~D7串行输出。

三、全加器和数值比较器的应用

1.实验目的

(1)熟悉74LS283、74LS85的基本功能。

(2)用全加器和数值比较器构成定值报警器。

2.实验器材

(1)74LS283:四位二进制数全加器。

(2)74LS85:四位二进制数值比较器。

(3)万用表、数字电路实验箱、导线(若干)。

3.实验内容及步骤

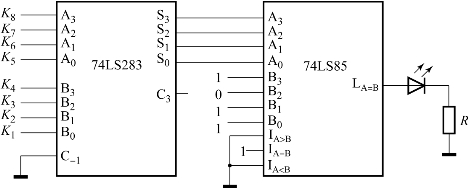

1)电路线路连接

按图4-46完成连线。连接芯片74LS283、74LS85电源线(5 V)、地线。74LS283数据输入端A3 A2 A1 A0、B3 B2 B1 B0分别接8个电平开关,数值比较器的输出端L(A=B)接1个电平指示灯。74LS283的和值输出端S3 S2 S1 S0分别接74LS85的数据A输入端A3 A2 A1 A0。74LS85的B数据输入端B3 B2 B1 B0送入“1011”,74LS283的C-1端送入“0”,74LS85的扩展输入端I(A>B)I(A=B)I(A<B)送入“010”。

74LS283和74LS85芯片引脚图分别如图4-36(a)和图4-40(a)所示。

图4-46 全加器和数值比较器构成定值报警器

2)调试

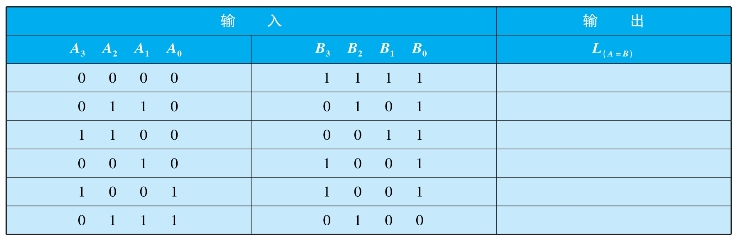

按表4-21所给74LS283数据输入端A3 A2 A1 A0、B3 B2 B1 B0分别输入相应数据,调试并记录输出逻辑值。

表4-21 定值报警器测试结果

4.任务完成结论

(1)当A3 A2 A1 A0+B3 B2 B1 B0= ___ __ __ _时,L(A=B)指示灯点亮报警。

(2)电路的工作原理是74LS85的扩展输入端IA>B、IA=B、IA<B=________,即实现对两个4位二进制数比较,输出LA=B接电平指示灯,当74LS85输入数据A′和B′为______时,指示灯点亮报警。74LS85的数据B′为“1011”,数据A′端口接74LS283的和值输出端S,即74LS85的A′数据为74LS283输入加数A与B的和值。即当被加数A与加数B的和值为定值________时,指示灯点亮报警。

四、编码器、译码器、显示器综合电路

1.实验目的

(1)熟悉编码器、译码器、显示器的功能及使用方法。

(2)搭试一个数字显示电路,使它所显示的数字与开关的编号相一致。

2.实验器材

(1)74LS147:10线-4线的高位优先编码器。

(2)CD4069:六反相器。

(3)CD4511:七段显示译码/驱动器。

(4)LC5011:共阴极数码管。

(5)万用表、数字电路实验箱、导线(若干)。

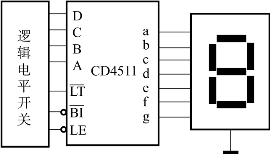

图4-47 译码显示电路

3.实验内容及步骤

(1)七段译码器/驱动器CD4511三个使能端的测试。

按图4-47所示完成连线。CD4511芯片引脚图如图4-25(a)所示。

使能端LE、![]() 和输入端DCBA按表4-22依次输入逻辑值,观察输出端逻辑值并记录在表格4-22输出栏中。

和输入端DCBA按表4-22依次输入逻辑值,观察输出端逻辑值并记录在表格4-22输出栏中。

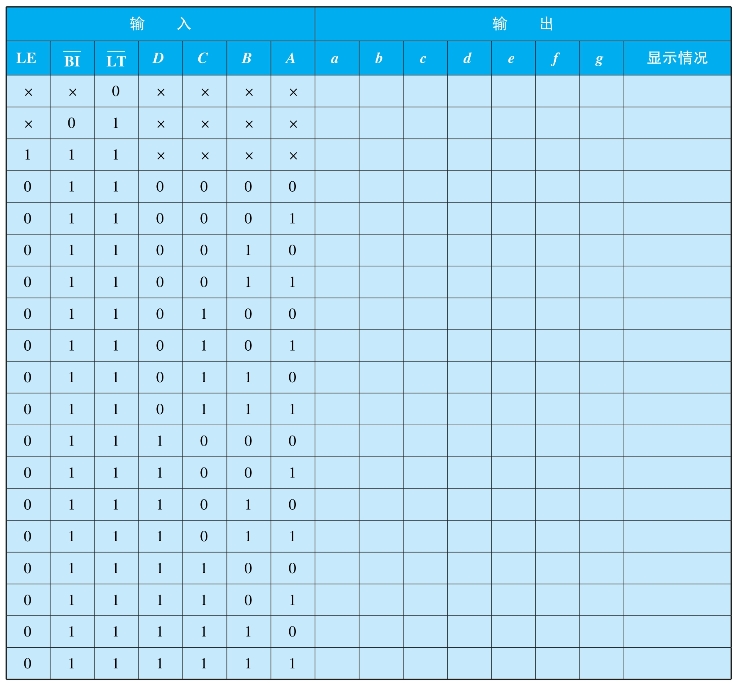

表4-22 CD4511功能测试

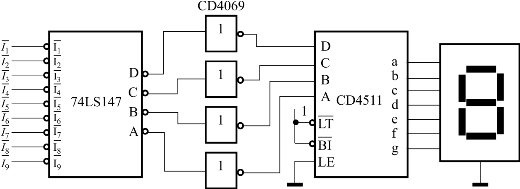

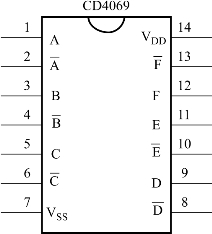

(2)按图4-48所示完成连线,CD4069芯片引脚如图4-49所示,按表4-23进行实验并将实验结果填入表中。74LS147芯片引脚和数码管引脚图如图4-14(a)和图4-22(a)所示。

图4-48 编码器-译码器-显示器电路

图4-49 CD4069芯片引脚图

表4-23 编码器-译码器-显示器电路测试结果

4.任务完成结论

_(1)74LS147是优先编码器,当多个输入为有效信号时,对优先级_最高_的进行编码。当![]() 均有效(000000000)时,对_ __ __ __ _进行编码,即 ___ __ __ _(

均有效(000000000)时,对_ __ __ __ _进行编码,即 ___ __ __ _(![]() )优先级最高_。当

)优先级最高_。当![]() 无效(

无效(![]() =1),

=1),![]() 均有效(00000000)时,对_ __ _进行编码,即_ __ __ __ _(

均有效(00000000)时,对_ __ _进行编码,即_ __ __ __ _(![]() )优先级次高,等等。由此_可知_,输入端 ___ __ __ _(

)优先级次高,等等。由此_可知_,输入端 ___ __ __ _(![]() )优先级最高,_ __ __ __ _优先级最低。图4-48中,当输入

)优先级最高,_ __ __ __ _优先级最低。图4-48中,当输入![]() 均无效(111111111)时,编码输出结果DCBA为_ __ __ __ _,CD4511的DCBA为_ __ __ __ __ __ _,数码管显示_ __ __ __ _。

均无效(111111111)时,编码输出结果DCBA为_ __ __ __ _,CD4511的DCBA为_ __ __ __ __ __ _,数码管显示_ __ __ __ _。

习题4.7

(2)请分析图4-49中CD4069的作用是什么?如果不使用会出现什么实验结果?

(3)如果数码管显示只出现“0、2、4、6、8”而不出现“1、3、5、7、9”,试分析电路可能出现的故障是什么?

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。