74LS151逻辑功能测试

1.构成函数发生器

利用数据选择器可以构成函数发生器,实现各种逻辑函数。只需将数据选择器的地址输入作为输入变量,并按要求将数据输入端接成所需状态,便可实现各种功能的组合逻辑函数。下面结合74LS151的实例应用,说明数据选择器构成函数发生器的方法。

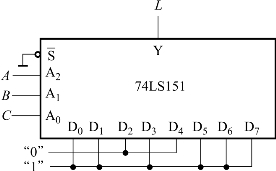

例如:用数据选择器74LS151实现逻辑函数L=C+![]() +AB。

+AB。

(1)由函数式输入变量个数确定数据选择器的规模。因L为三变量函数,故可选用8选1数据选择器74LS151,其选择输入变量A2 A1 A0与函数A、B、C正好对应。

(2)写出函数式的最小项与或表达式,并与数据选择器的输出式相比较。

74LS151输出函数表达式:

![]()

(3)由比较结果确定数据选择器输出端Y及各输入端A2 A1 A0、D0~D7与L逻辑函数式中各变量(A、B、C)的关系,并画出逻辑图。

若令 Y=L,A2=A,A1=B,A0=C

则 D2=D4=0, D0=D1=D3=D5=D6=D7=1

便可画出图4-30所示电路图。

图4-30 74LS151实现逻辑函数电路图(https://www.xing528.com)

特别提示

采用中规模逻辑器件设计构成函数发生器,一般可以采用二进制译码器或数据选择器,本章完整地介绍了两种器件的应用方法。采用数据选择器,不能实现多输出函数,而采用二进制译码器,则可以实现多输出函数。

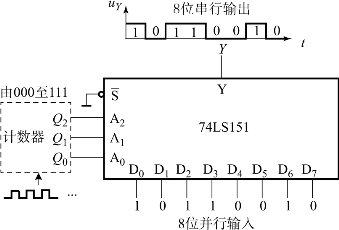

2.数据选择器实现并-串转换

数据选择器可以实现信号的并-串转换。并行是指,多位数据同时传送,具有并行特点的输入(输出)端叫作并行输入(输出)端,此时输入(输出)的数据叫作并行输入(输出)数据。串行是指,数据排成一行,一位一位经过一个端口先后依次传送,具有串行特点的输入(输出)端叫作串行输入(输出)端,此时输入(输出)的数据叫作串行输入(输出)数据。

如图4-31所示,若数据选择器的数据输入端D0~D7并行输入8个数据,选择控制端A2 A1 A0按照某一频率依次输入“000”~“111”8个控制数据,那么输出端就按照此频率依次先后输出D0,D1,D2,…,D7这8个数据,由此并行输入数据D0~D7在控制数据作用下依次串行输出,实现数据的并-串转换。

图4-31 并行输入数据转换成串行输出

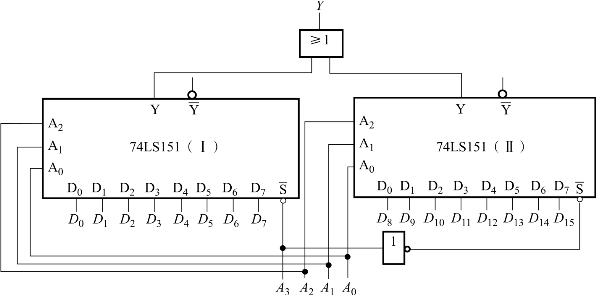

3.级联扩展

数据选择器的级联扩展主要工作是扩展输入地址位数,采用的思路是芯片的低位地址共用,用芯片的控制端生成最高地址,作为系统的片选信号,区别每个芯片的工作区。首先最高地址先起作用,进行片选,然后再根据片内低位地址作片内选,从片内数据段选择其中的一路输出。任何时候,系统中只会有一个芯片工作,其他芯片禁止。禁止的数据选择器的输出为0,两个输出端采用或门连接即可。

例如:用两个8选1数据选择器74LS151,可构成16选1数据选择器。

具体电路如图4-32所示。

当A3=0时,片Ⅰ工作,片Ⅱ禁止,在A2 A1 A0控制端作用下可实现D0~D7数据的选择输出;A3=1时,片Ⅱ工作,片Ⅰ禁止,在A2 A1 A0控制端作用下可实现D8~D15数据的选择输出。

图4-32 用74LS151构成16选1数据选择器

习题4.5

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。