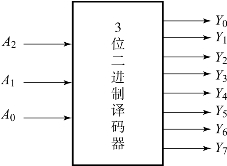

二进制译码器的输入为二进制代码,输出是一组与输入代码相对应的高、低电平信号。若输入为n位二进制代码,代码组合就有2n种,可译出对应的2n个输出信号。图4-15所示为3位二进制译码器框图,它的输入是3位二进制代码,有8种状态,8个输出端分别对应其中一种输入状态。因此,又将3位二进制译码器称为3线-8线译码器。

图4-15 3位二进制译码器框图

1.74LS138的逻辑功能

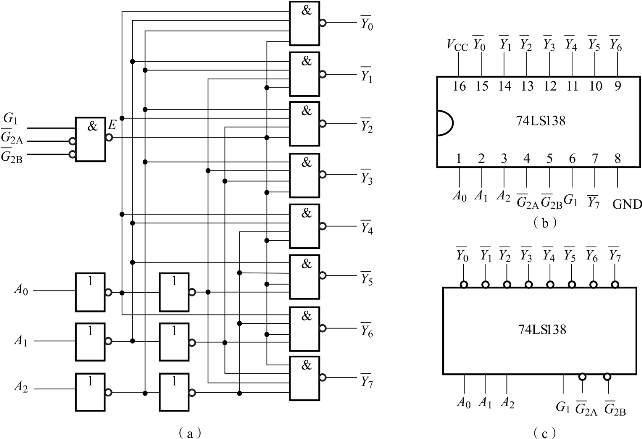

现以集成芯片74LS138为例分析二进制译码器的特点及应用。图4-16(a)所示为3线-8线译码器74LS138的逻辑电路图,图4-16(b)所示为74LS138的引脚图,图4-16(c)所示为74LS138的逻辑符号,表4-8所示为74LS138功能真值表。

图4-16 74LS138 3线-8线译码器

(a)逻辑电路图;(b)引脚图;(c)逻辑符号

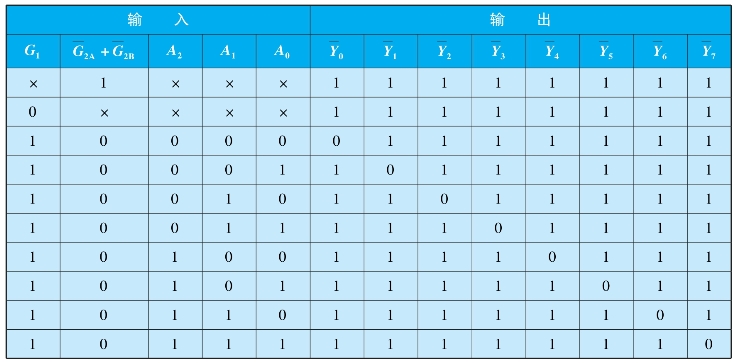

表4-8 74LS138功能真值表

由图4-16(a)逻辑电路图可知,74LS138有三个译码输入端(又称地址输入端)A2,A1,A0,8个译码输出端![]() ~

~![]() ,以及三个控制端(又称使能端)G1,

,以及三个控制端(又称使能端)G1,![]() ,

,![]() 。当E=0时,

。当E=0时,![]() ~

~![]() 均为1,即封锁了译码器的输出,译码器处于禁止工作状态;当E=1时,译码器被选通,处于工作状态,由输入变量A2,A1,A0来决定

均为1,即封锁了译码器的输出,译码器处于禁止工作状态;当E=1时,译码器被选通,处于工作状态,由输入变量A2,A1,A0来决定![]() ~

~![]() 的状态。由图4-16可知,E=G1·

的状态。由图4-16可知,E=G1·![]() ·

·![]() =G1·

=G1·![]() ,当G1=1,

,当G1=1,![]() +

+![]() =0(

=0(![]() 和

和![]() 均为0)时,电路才处于工作状态。否则,译码器被禁止,所有的输出端被封锁在高电平。G1,

均为0)时,电路才处于工作状态。否则,译码器被禁止,所有的输出端被封锁在高电平。G1,![]() ,

,![]() 这三个控制端又叫作“片选”输入端,利用片选的作用可以将多片电路连接起来,以扩展译码器的功能。

这三个控制端又叫作“片选”输入端,利用片选的作用可以将多片电路连接起来,以扩展译码器的功能。

特别提示

使能端经常出现在中规模集成电路中,用来扩展电路功能。74LS138由于使能端G1, 、

、 的加入,功能发生了变化。当G1

的加入,功能发生了变化。当G1 =100时译码器正常译码,否则译码器不工作。将逻辑值为“1”时芯片正常工作的使能端叫作高电平有效使能端,为“0”时的叫作低电平有效,则G1为高电平有效的使能端,

=100时译码器正常译码,否则译码器不工作。将逻辑值为“1”时芯片正常工作的使能端叫作高电平有效使能端,为“0”时的叫作低电平有效,则G1为高电平有效的使能端, 为低电平有效。

为低电平有效。

从表4-8功能真值表中可以看出,当译码器处于工作状态时,每输入一个二进制代码将对应一个输出端为低电平,而其他输出端均为高电平,也可以说对应的输出端被“译中”。例如,当A2 A1 A0输入为000时,输出端![]() 被“译中”,

被“译中”,![]() 输出0;当A2 A1 A0输入为100时,输出端

输出0;当A2 A1 A0输入为100时,输出端![]() 被“译中”,

被“译中”,![]() 输出0。

输出0。

74LS138的逻辑功能测试

2.74LS138的应用

1)构成函数发生器

用3线-8线译码器74LS138可以构成函数发生器。如果将地址输入端作为逻辑函数的输入变量,那么译码器的每个输出端都与某一个最小项相对应,只要加上适当的门电路,就可以实现预定的逻辑函数。

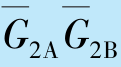

根据芯片74LS138的逻辑电路图得出,当![]() =100时,各个译码输出变量的逻辑函数为

=100时,各个译码输出变量的逻辑函数为

由以上函数式可以看出,若将译码输入变量A2、A1、A0作为逻辑函数三个输入逻辑变量,则译码输出变量![]() ~

~![]() 是这三个输入逻辑变量的全部最小项的反函数,即

是这三个输入逻辑变量的全部最小项的反函数,即![]() ~

~![]() 。利用附加门电路将这些最小项的反函数适当地组合起来,便可产生任何形式的组合逻辑函数。

。利用附加门电路将这些最小项的反函数适当地组合起来,便可产生任何形式的组合逻辑函数。

例如:试利用译码器74LS138和与非门设计一个多输出的组合逻辑电路。

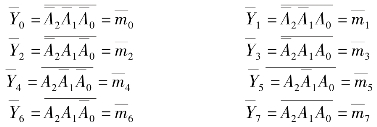

解:(1)将函数Y1、Y2写成最小项表达式并做相应变换。

(https://www.xing528.com)

(https://www.xing528.com)

(2)将函数输入变量A、B、C对应接到译码器74LS138的三个输入端,即A=A2,B=A1,C=A0,在输出端附加两个四输入与非门,即可得到Y1、Y2的逻辑电路,如图4-17所示。

图4-17 译码器74LS138实现三变量逻辑函数连线图

特别提示

若要用74LS138实现四变量逻辑函数,就必须先用两片74LS138扩展成四变量译码器,才能按上述方法构成所需函数。

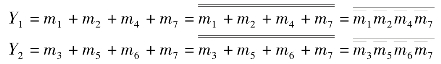

2)构成数据分配器

数据分配器相当于多路分配器,它的逻辑功能是在选择控制信号控制下将一个输入数据分配到多个数据输出端的其中一个输出。通常数据分配器有1个数据输入端,2n个数据输出端,n位选择控制端。n位选择控制变量可以组成2n个代码,每次根据选择变量的不同代码组合将输入数据分配输出到其中一个输出端,图4-18所示为数据分配器框图。

图4-18 数据分配器框图

若数据分配器有n个选择控制端,则数据输出端应为2n个,称此分配器为2n路数据分配器。用74LS138实现数据分配器功能时,须将其译码输入端A2 A1 A0作为数据分配器的选择控制端,使能端![]() 或G1作为数据输入端D,译码输出端作为数据输出端。

或G1作为数据输入端D,译码输出端作为数据输出端。

由表4-9可以看出,使能控制端![]() 作为数据分配器的数据输入端D使用,当D=1时,所有数据输出值

作为数据分配器的数据输入端D使用,当D=1时,所有数据输出值![]() 全部为1,与选择控制信号A2 A1 A0无关。当D=0时,就由选择控制信号A2 A1 A0选出8个输出端的一个,将D=0的信息分配输出。数据选择器74LS138的数据分配功能测试线路连接图如图4-19所示。

全部为1,与选择控制信号A2 A1 A0无关。当D=0时,就由选择控制信号A2 A1 A0选出8个输出端的一个,将D=0的信息分配输出。数据选择器74LS138的数据分配功能测试线路连接图如图4-19所示。

表4-9 74LS138构成数据分配器

图4-19 数据选择器74LS138的数据分配功能测试线路连接图

3)级联扩展

若将使能端作为变量输入端,进行适当的组合,可以扩大译码器输入变量数。

图4-20所示为由两片74LS138译码器构成的四线-十六线译码器的连接图。从图4-20中不难看出,片Ⅰ的8个输出端作为低位的输出,片Ⅱ的8个输出端作为高位的输出。当E=1时,片Ⅰ和片Ⅱ均处于禁止态,![]() 均输出1。当E=0时,若A3=0,则片Ⅰ的

均输出1。当E=0时,若A3=0,则片Ⅰ的![]() =0,片Ⅱ的G1=0,因此片Ⅰ处于工作态,片Ⅱ处于禁止工作态,由A2 A1 A0决定

=0,片Ⅱ的G1=0,因此片Ⅰ处于工作态,片Ⅱ处于禁止工作态,由A2 A1 A0决定![]() 的状态;若A3=1,则片Ⅰ的

的状态;若A3=1,则片Ⅰ的![]() =1,片Ⅱ的G1=1,因此,片Ⅰ不工作,片Ⅱ工作,由A2 A1 A0决定

=1,片Ⅱ的G1=1,因此,片Ⅰ不工作,片Ⅱ工作,由A2 A1 A0决定![]() 的状态。

的状态。

图4-20 由两片74LS138译码器构成的四线-十六线译码器的连接图

特别提示

译码器级联扩展的基本思路和工作过程总结如下:

(1)根据设计要求和所用芯片类型,确定需要芯片个数,以保证输出信号端子够用。

(2)设计过程主要工作有两步:输入的片内低位代码共用;用控制端生成最高位代码,也就是形成芯片的片选信号,以区分芯片的工作区。

(3)根据芯片工作区,确定输出信号标号的排布即可。

对于译码器的级联扩展,不论设计要求和所用芯片的单片规模之间有多大差异,级联扩展时的基本过程都是一样的,按如上思路即可。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。