1.TTL输出驱动CMOS输入

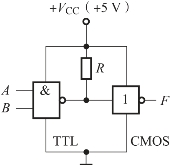

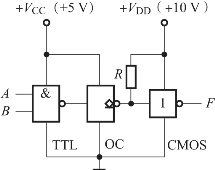

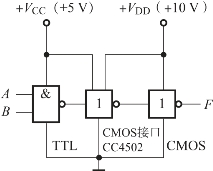

(1)当TTL电路驱动4000系列和HC系列CMOS时,如果电源电压V CC与V DD均为5 V时,从表3-1可以看出,TTL门的U OH不符合CMOS的U IH要求,为了很好地解决这个电平匹配问题,在TTL门电路的输出端外接一个上拉电阻R P,如图3-18所示,使TTL门电路的U OH≈5 V。如果CMOS的电源电压较高,则TTL电路需采用OC门,在其输出端接上拉电阻,如图3-19所示,上拉电阻的大小将影响其工作速度。或采用另一种方法用专用的CMOS接口电路(如CC4502、CC40109等),如图3-20所示。

表3-1 TTL的74LS系列和CMOS的4000、74HC系列的输入、输出高电平和低电平

图3-18 TTL驱动COMS采用外接上拉电阻

图3-19 TTL驱动COMS采用OC门

(2)当TTL电路驱动74HCT系列和74ACT系列的CMOS门电路时,因两类电路性能兼容,故可以直接相连,不需要外加元件和器件。

2.CMOS输出驱动TTL输入

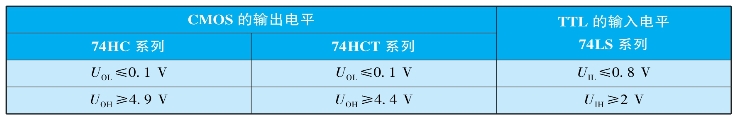

74HC/74HCT系列CMOS和74LS系列TTL输入、输出高电平与低电平如表3-2所示。由表3-2可知,CMOS的输出电平同TTL的输入电平兼容。若CMOS电路的电源电压为+5 V时,则两者可直接相连。当CMOS电源电压较高时,可采用专用的电平转换电路,如图3-20所示。

表3-2 74HC/74HCT系列CMOS和74LS系列TTL输入、输出高电平与低电平

图3-20 TTL驱动COMS采用专用的接口电路

知识链接

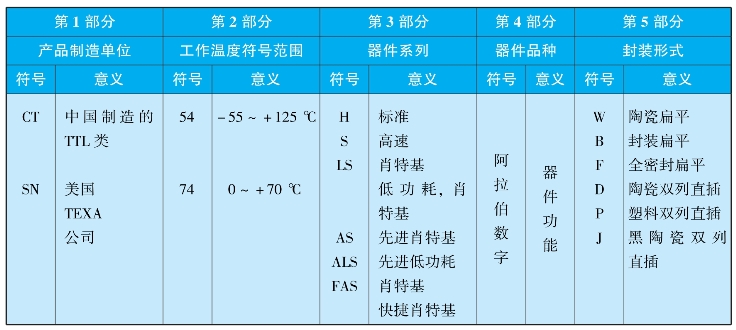

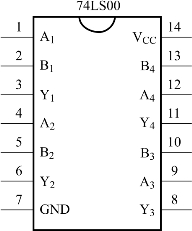

TTL门电路是基本逻辑单元,是构成各种TTL电路的基础,实际生产的TTL集成电路品种齐全、种类繁多、应用十分普遍。TTL器件型号由五部分组成,其符号和意义如表3-3所示。

表3-3 TTL器件型号组成的符号和意义

例如:

目前,我国TTL集成电路主要有CT54/74(普通)、T54/74H(高速)、CT54/74S(肖特基)、CT54/74LS(低功耗)四个系列国家标准的集成门电路。它们的主要性能指标如表3-4所示。由于CT54/74LS系列产品具有最佳的综合性能,因而得到广泛应用。

表3-4 TTL各系列集成门电路主要性能指标

在不同系列TTL门电路中,无论是哪一种系列,只要器件品名相同,那么器件功能就相同,只是性能不同。例如:7420、74H20、74S20、74LS20都是双4输入与非门(内部有两个4输入的与非门),都采用14条引脚双列直插式封装,而且,输入端、输出端、电源、地线的引脚位置也是相同的。

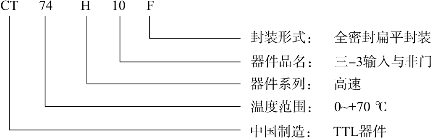

常用的CMOS产品有4000系列、74C××系列等,表3-5所示为4000系列CMOS器件型号组成符号及意义。

表3-5 4000系列CMOS器件型号组成符号及意义

74C××系列有普通74C××系列、高速74HC××/HCT××系列及先进的74AC××/ACT××系列。

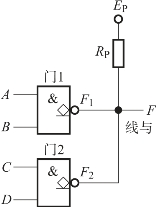

先导案例解决

74LS04和CD4069所实现的逻辑功能是一样的,都表示六非门,74LS04是TTL电路,悬空相当于接1;而CD4069是CMOS电路,其特点是:功耗低、电源电压范围宽、抗干扰能力强、逻辑摆幅大、带负载能力强,但输入端不能悬空。74LS00和74LS03表示的都是四-2输入与非门,74LS00是普通TTL电路,输出端不能并接,而74LS03是四-2输入OC与非门,在使用过程中必须接上拉电阻和上拉电源。

任务训练

一、门电路功能测试

1.实验目的

(1)熟悉面包板使用,正确识读集成芯片。

(2)了解与非门、或非门、与或非门、异或门的工作原理。

(3)会测试74LS00、74LS02、74LS51、74LS86的逻辑功能。

2.实验器材

(1)74LS00 四-2输入与非门。

(2)74LS02 四-2输入或非门。

(3)74LS51 双2路3-3、2-2输入与或非门。

(4)74LS86 四-2输入异或门。

(5)万用表、数字电路实验箱、导线(若干)。

3.实验内容及步骤

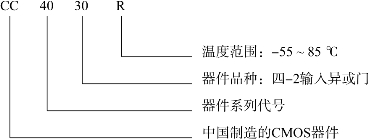

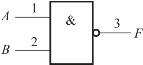

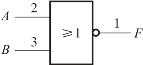

1)与非门(74LS00)电路逻辑功能测试

(1)将芯片74LS00缺口朝左插入面包板。

(2)根据芯片引脚图3-21,按图3-22所示完成连线[首先将地线GND(V SS)脚接地,将V CC(V DD)接+5 V]。

(3)输入端A、B接逻辑电平开关,输出端F接指示灯。根据表3-6进行测试,将结果记入表中,并写出逻辑表达式F=________。

图3-21 74LS00 四-2输入与非门引脚

图3-22 与非门测试电路

表3-6 与非门测试结果

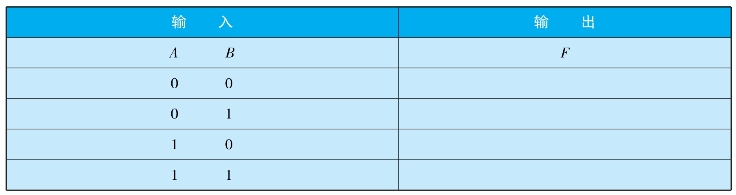

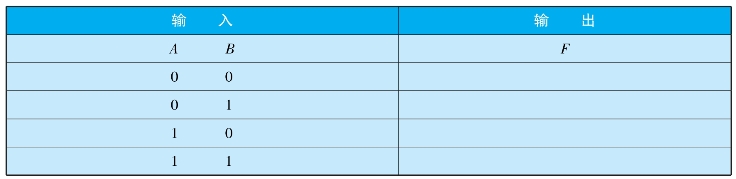

2)或非门(74LS02)电路逻辑功能测试

(1)将芯片74LS02缺口朝左插入面包板。

(2)根据芯片引脚图3-23,按图3-24所示完成连线[首先将地线GND(V SS)脚接地,将V CC(V DD)接+5 V]。

图3-23 74LS02 四-2输入或非门引脚

图3-24 或非门测试电路

(3)输入端A、B接逻辑电平开关,输出端F接指示灯。根据表3-7进行测试,将结果记入表中,并写出逻辑表达式F=________。(https://www.xing528.com)

表3-7 或非门测试结果

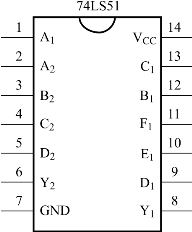

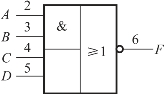

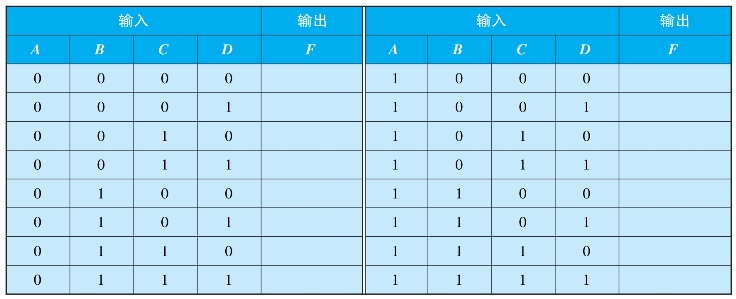

3)与或非门(74LS51)电路逻辑功能测试

(1)将芯片74LS51缺口朝左插入面包板。

(2)根据芯片引脚图3-25,按图3-26所示完成连线[首先将地线GND(V SS)脚接地,将V CC(V DD)接+5 V]。

图3-25 74LS51 双2路3-3、2-2输入与或非门引脚

图3-26 与或非门测试电路

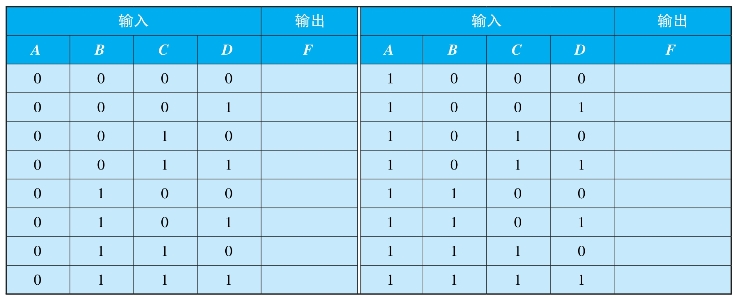

(3)输入端A、B、C、D接逻辑电平开关,输出端F接指示灯。根据表3-8进行测试,将结果记入表中,并写出逻辑表达式F=________。

表3-8 与或非门测试结果

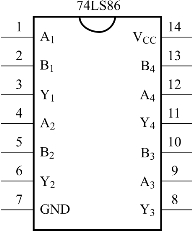

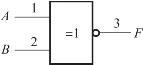

4)异或门(74LS86)电路逻辑功能测试

(1)将芯片74LS86缺口朝左插入面包板。

(2)根据芯片引脚图3-27,按图3-28所示完成连线[首先将地线GND(V SS)脚接地,将V CC(V DD)接+5 V]。

图3-27 74LS86 四-2输入异或

门引脚

图3-28 异或门测试电路

(3)输入端A、B接逻辑电平开关,输出端F接指示灯。根据表3-9进行测试,将结果记入表中,并写出逻辑表达式F=________。

表3-9 异或门测试结果

4.任务完成结论

(1)根据表3-6的测试结果可以看出与非门输入有“0”时,输出为_ __ __ _,输入全“1”时,输出为______。如果与非门改作非门用则多余输入端接_ __ __ __ __ _。

(2)根据表3-7的测试结果可以看出或非门输入有“1”时,输出为_ __ __ _,输入全“0”时,输出为______。如果或非门改作非门用则多余输入端接_ __ __ __ _。

(3)根据表3-8的测试结果可以看出与或非门输入AB或CD的与项为“1”时,输出为______,输入AB、CD的与项全为“0”时,输出为 ___ __ _。

(4)根据表3-9的测试结果可以看出异或门输入A,B相同时,输出为_ __ __ _,输入A,B不相同时,输出为______。如果异或门改作非门用,则多余输入端接_ __ __ __ _。

二、OC门和三态门逻辑功能测试

1.实验目的

(1)了解OC门和三态门的工作原理。

(2)会测试74LS03、74LS125的逻辑功能。

2.实验器材

(1)74LS03 四-2输入OC与非门引脚。

(2)74LS125 三态四总线驱动器。

(3)万用表、数字电路实验箱、导线(若干)。

3.实验内容及步骤

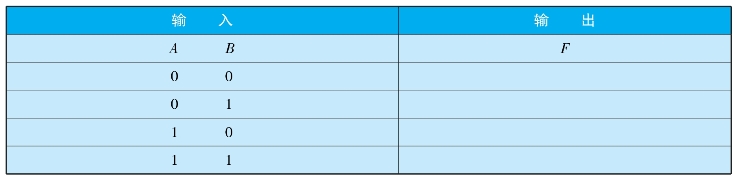

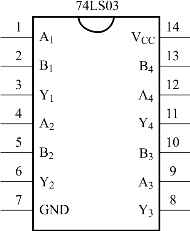

1)OC与非门(74LS03)电路逻辑功能测试

(1)将芯片74LS03缺口朝左插入面包板。

(2)根据芯片引脚图3-29,按图3-30所示完成连线[首先将地线GND(V SS)脚接地,将V CC(V DD)接+5 V]。

图3-29 74LS03 四-2输入OC与非门引脚

图3-30 OC与非门测试电路

(3)输入端A、B、C、D接逻辑电平开关,上拉电源5 V,上拉电阻1 kΩ,输出端F接指示灯。根据表3-10进行测试,并将结果记入表中,并写出逻辑表达式F= 。

表3-10 OC与非门功能测试结果

2)三态门(74LS125)电路逻辑功能测试

(1)将芯片74LS125缺口朝左插入面包板。

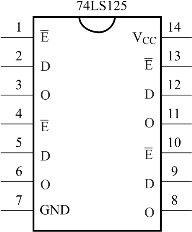

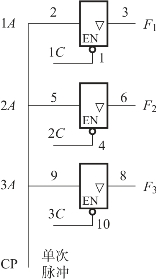

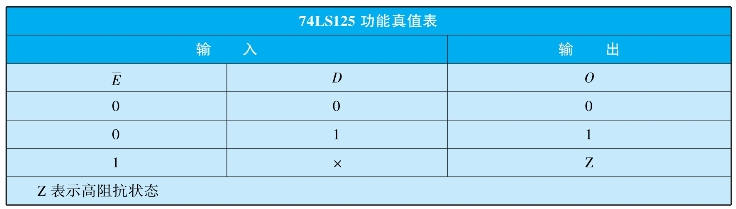

(2)根据芯片引脚图3-31及表3-11的74LS125真值表,按图3-32所示完成连线[首先将地线GND(V SS)脚接地,将V CC(V DD)接+5 V]。

图3-31 74LS125 三态四总线驱动器引脚

图3-32 三态门测试电路

表3-11 74LS125真值表

(3)输入端1A、2A、3A并接,接单次脉冲,使能端1C、2C、3C接逻辑电平开关,根据表3-12进行测试,按动单次脉冲,将结果记入表中,并写出逻辑表达式F= 。

表3-12 三态门功能测试结果

4.任务完成结论

(1)根据表3-11的测试结果可以看出多个OC与非门并接可以实现_ __ __ __ ___ __ _功能。

(2)根据表3-12的测试结果得三态门有_ __ __ __ __ __ ___ __ _三种工作状态,74LS125控制端为______________(高电平/低电平)输入与输出实现传输,控制端为______________(高电平/低电平)输出为高阻抗状态。

习题3.3

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。