FPGA的基本结构是将逻辑功能块排成阵列,并由可编程的互连资源连接这些功能块来实现各种逻辑设计。但各公司生产的FPGA器件有各自的特点,下面通过对Xilinx公司和Altera公司的FPGA产品的介绍进一步说明其结构。

1)Xilinx公司的FPGA结构特点

表8.6为Xilinx公司的XC系列产品的基本逻辑门、输入/输出模块(Input/Output Block,IOB)、触发器以及可编程逻辑块(Configurable Logic Block,CLB)的容量。实际工作条件如表8.7所示。由表可见,FPGA的逻辑容量密度大,集成度高,可大大减少印制电路板的空间,降低系统功耗,同时还可提高系统设计的工艺性和产品的可靠性。

表8.6 Xilinx公司的XC系列

表8.7 XC系列的实际工作条件

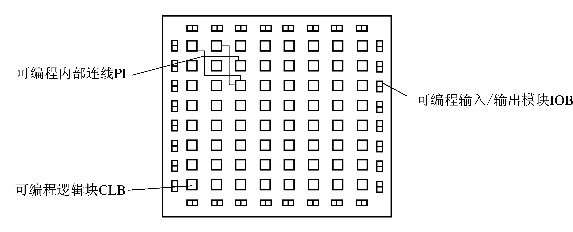

XC系列FPGA的基本结构为逻辑单元阵列(Logic Cell Array,LCA)的分布结构。LCA主要是由可配置存储器SRAM阵列、可编程逻辑块CLB矩阵及周围的输入/输出模块IOB、可编程内部连线(Programmable Interconnect,PI)构成。图8.13为FPGA结构示意图,下面对图中各部分进行简单介绍。

图8.13 FPGA平面结构示意图

(1)可配置存储器(SRAM)

静态存储器(Static RAM,SRAM)以点阵形式分布于FPGA器件芯片中。对FPGA器件的编程,就是通过对SRAM加载不同的配置数据,来决定和控制各个CLB、IOB及PI的逻辑功能和它们之间的相互连接关系,完成对芯片的设计。图8.14给出了FPGA中SRAM的基本单元结构。

图8.14 SRAM的基本单元结构

(2)可编程逻辑块(CLB)

CLB由可编程的组合逻辑块和寄存器组成。寄存器的输入可为组合逻辑块或CLB的输出。寄存器的输出也可以驱动组合逻辑部分。FPGA的不同系列产品,其CLB的功能原理相同,但结构和性能有差异。

(3)可编程输入/输出块(IOB)

IOB块分布于芯片四周,可以通过编程实现不同的逻辑功能和逻辑接口的需要。例如,XC3000/3100和XC4000系列器件的每个IOB控制一个外部引脚,可以通过编程定义该引脚为输入、输出或双向传输三种功能。XC4000系列的IOB还增加了时钟极性、输出缓冲器配置等可选择项,使逻辑设计更灵活。

(4)可编程的内部连线(PI)

在SRAM控制下,通过对PI的配置、定义,将CLB和IOB进行组合以实现系统的逻辑功能。FPGA器件的PI主要由金属线段组成。XC2000/3000/3100系列的PI分布于CLB阵列周围,有通用连线、直接连接线、长线、全局连线等几种。通用连线主要用于CLB之间的连接,长线用于长距离和多分支信号的传送,全局连线用于输送公共信号,直接连线用于相邻的CLB信号端之间的直接相连。PI通过SRAM配置、控制的可编程连接点与CLB、IOB和开关矩阵(Switching Matrices,SM)相连,实现系统的布线。图8.15为PI布局情况。XC4000系列的PI有三种内部连线:单长线、双长线和长线,采用块与块之间对称的周边的可编程开关点和开关矩阵结构的金属线连接,因此布线方式更多、更灵活。(https://www.xing528.com)

图8.15 FPGA的内部连线

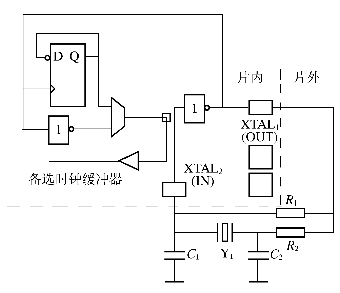

图8.16 FPGA的晶体振荡器电路

(5)晶体振荡器电路

FPGA芯片内提供了一个高速反相器,用于和外接晶体振荡器连接,形成振荡电路。其原理如图8.16所示。XC4000系列中还设有分频器,把晶振信号分频输出各种时钟信号来满足系统需要。

2)Altera公司的FLEX系列FPGA器件

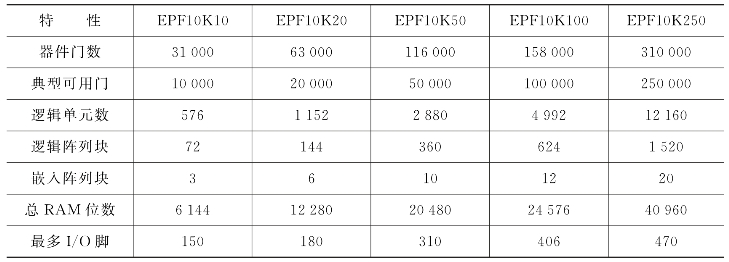

Altera公 司 的FLEX系 列FPGA器 件 包 括FLEX10K、FLEX20K、FLEX6000和FLEX8000等系列,其中FLEX10K系列是一种嵌入式可编程逻辑器件,具有密度高、成本低、功耗小等特点。该系列包括FLEX10K、FLEX10KA、FLEX10KB、FLEX10KV、FLEX10KE五个子系列。表8.8列出了FLE10K系列典型器件的性能。图8.17为FLEX10K的结构框图。下面进行简单介绍。

表8.8 FLE10K系列典型器件的性能

图8.17 FLEX10K的结构框图

(1)嵌入式阵列

嵌入式阵列由一系列嵌入式阵列块(Embedded Array Block,EAB)构成。EAB是在输入/输出口上带有寄存器的柔性(可变更)RAM块,可单独使用,也可组合起来使用。在要实现存储器功能时,每个EAB可提供2 048个存储位,来构造RAM、ROM及双口RAM等。在要实现乘法器、微控制器、状态机及复杂逻辑时,每个EAB可提供100~600个门。

(2)逻辑阵列

由一系列逻辑阵列块(LAB)组成。每个LAB相当于96个可用逻辑门,可以构成一个中规模的逻辑块,如8位计数器、地址译码器或状态机等。也可以将多个LAB组合起来构成一个更大规模的逻辑块。

(3)快速通道(Fast Track)互连

Fast Track是纵横贯穿整个器件的一系列水平(行)和垂直(列)的连续式布线通道(连线带),可以灵活、快速地实现器件内部信号的互联和器件引脚之间的信号互连。

(4)I/O单元(IOE)

IOE位于Fast Track行线和列线的两端,每个I/O引脚由一个IOE馈接。每个IOE含有一个双向缓冲器和一个可作为输入/输出/双向寄存器的触发器。IOE可提供输入信号保持、输出信号延时、编程支持、摆率控制、三态缓冲和漏极开路输出等功能。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。