在第6.2节介绍了时序逻辑电路的分析方法。异步时序电路与同步时序电路的分析过程稍有不同,由于异步时序逻辑电路中各个触发器状态转换的时间不完全是由同一时钟脉冲单独控制,因此,在异步时序电路的分析中时钟方程就是必不可少的。

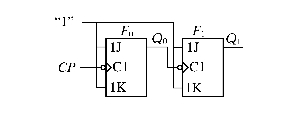

图6.15 异步2位二进制加法计数器

1)异步二进制计数器

图6.15是异步2位二进制加法计数器。

分析步骤如下:

(1)写方程

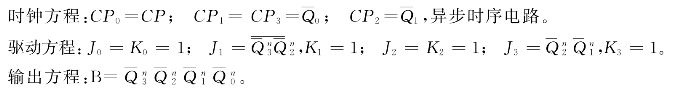

时钟方程:CP0=CP,CP1=Q0,异步时序电路。

驱动方程:T0=T1=1。

(因触发器为T′触发器,驱动方程也可不写)

(2)求状态方程

T′触发器的特性方程为:![]()

求得状态方程:![]()

(“[]”表示有效时钟条件,说明只有在相应时钟脉冲触发沿到来时,触发器才会按状态方程进行状态转换,否则将保持原来状态)

(3)列状态表

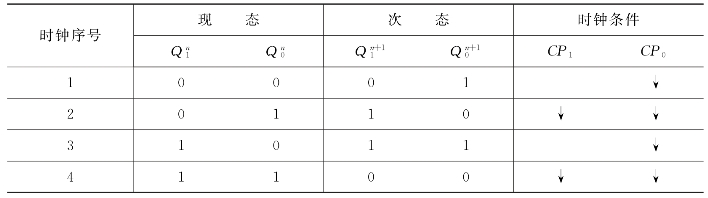

状态表见表6.8,设初始状态Q1Q0=00。

表6.8 异步2位二进制加法计数器状态表

列表时应特别注意有效时钟条件。例如,![]() 当CP下降沿到来,由于CP0=CP,触发器F0就具备了时钟条件,因此,F0将按状态方程

当CP下降沿到来,由于CP0=CP,触发器F0就具备了时钟条件,因此,F0将按状态方程![]() 来更新状态,即由0转换成1;而CP1=Q0时,此时Q0为上升沿,F1不具备时钟条件,故F1保持原来状态,即

来更新状态,即由0转换成1;而CP1=Q0时,此时Q0为上升沿,F1不具备时钟条件,故F1保持原来状态,即![]()

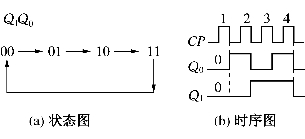

(4)画状态图和时序图

其状态图和时序图见图6.16。从时序图上能更清楚地看到各个触发器下降沿触发的特点。

(5)检查自启动,说明功能

由状态图可知,此电路只有一个有效循环,故本逻辑电路为能自启动的异步二进制加法计数器。(https://www.xing528.com)

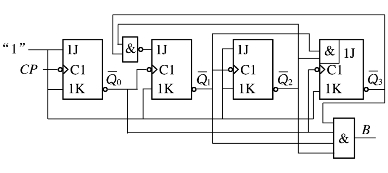

2)异步十进制减法计数器

逻辑电路如图6.17所示。

图6.16 异步2位二进制加法计数器

图6.17 异步十进制减法计数器逻辑图

分析步骤如下:

(1)写方程

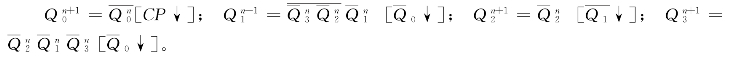

(2)求状态方程

(3)列状态表

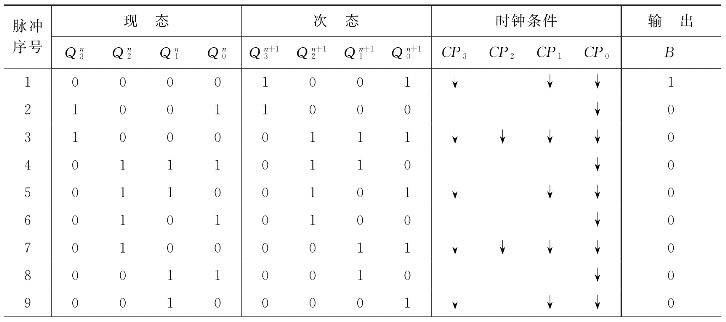

状态表如表6.9所示。设初态Q3Q2Q1Q0=0000。

表6.9 异步十进制减法计数器状态表

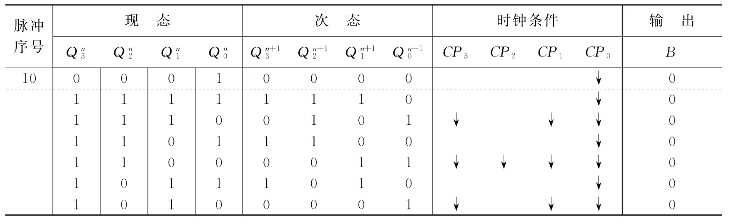

(续表6.9)

(4)画状态图和时序图

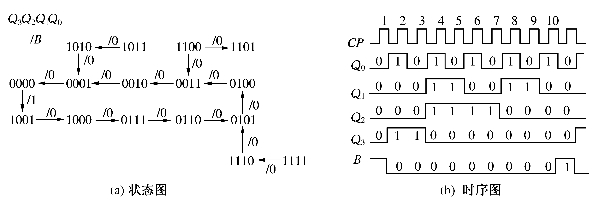

根据状态表画出的状态图和时序图如图6.18所示。

图6.18 异步十进制减法计数器

(5)检查自启动,说明功能

本电路为能自启动的8421码异步十进制减法计数器。与同步计数器相比,异步计数器具有电路简单,连接有规律,要求的时钟CP的驱动功率小等优点;而缺点是计数速度慢。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。