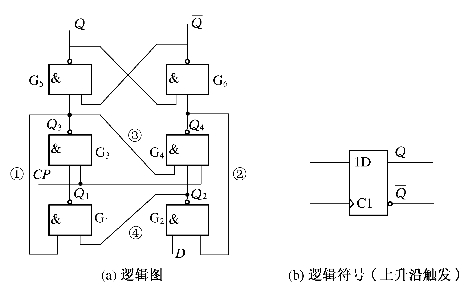

触发器接收输入数据和输出状态转换同时发生在CP的某一跳变沿的触发方式被定义为边沿触发方式。边沿触发型D触发器的电路和逻辑符号如图5.21所示。

图5.21 边沿触发的D触发器

当CP=0时![]() 故Q与

故Q与![]() 保持原状态不变,且和输入的D无关。

保持原状态不变,且和输入的D无关。

当CP由0→1,即上升跳变沿(↑),此时![]() 而

而![]() 输出Q和

输出Q和![]() 将根据D的输入改变状态。如果D为1,则

将根据D的输入改变状态。如果D为1,则![]() 就有

就有![]() 即触发器被置1;如果D为0,则Q2=1,Q3=1,Q4=0,就有

即触发器被置1;如果D为0,则Q2=1,Q3=1,Q4=0,就有![]() 即触发器被置0。

即触发器被置0。

图5.22 边沿触发D触发器时序图(设初始状态Q=0)(https://www.xing528.com)

在CP=1期间,如果在CP上升沿时是置1,则置1信号(Q3=0,Q4=1)将通过①线使Q1=1、Q3=0,即维持置1,同时通过③线使Q4=1,即阻塞置0;如果CP上升沿时是置0,则置0信号(Q3=1,Q4=0)通过②、③线使Q2=1,Q4=0,即维持置0,同时通过④线使Q1=0、Q3=1,阻塞置1。维持和阻塞作用直至CP=0到来后方才消除,因此CP=1期 间![]() 不变,且与D无关。此种触发器又叫维持阻塞型D触发器。图5.22为边沿触发D触发器的时序图。

不变,且与D无关。此种触发器又叫维持阻塞型D触发器。图5.22为边沿触发D触发器的时序图。

综上所述,该触发器接受输入数据和改变输出状态均发生在CP的上升跳变沿,因而称其为边沿触发方式。由于其实现的是D型触发器的逻辑功能,因而称为边沿触发D触发器。

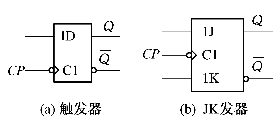

图5.23 下降沿触发的触发器

实际中,也有在CP下降跳变沿(↓)触发的触发器,这类边沿触发器的逻辑符号如图5.23所示。在边沿触发器的逻辑符号中,时钟端的“>”为动态符号,表示时钟有效信号是时钟的跳变沿,时钟端加了小圆圈表示↓触发。

对于边沿触发的触发器,由于其接收输入数据和输出状态转换均发生在CP的同一边沿,所以,抗干扰能力强。

在实际应用中,对于同一逻辑功能的触发器可以根据具体情况选择不同触发方式的电路。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。