硅-硅直接键合(SDB)技术在电力半导体器件中的应用主要体现在以下几个方面:一是代替传统的三重扩散工艺或高阻厚外延工艺提供衬底材料或者制作SOI,如用SDB技术制作功率双极型晶体管和IGBT[65];二是将复杂的器件结构分解,通过具有不同掺杂浓度分布的芯片键合,使复杂结构的器件工艺简化,降低了工艺难度和成本,如用SDB技术制作静电感应晶闸管(Static Induction Thyristor,SITH)[66]、IGBT及IGCT等器件;三是通过不同器件结构的键合,实现新器件的集成,以简化或取消外部驱动电路,如MOSFET芯片和pnp结构的键合可以制作MTO[67],或将两个MOSFET背对背键合来制作双向IGBT芯片(如5.3.2节所述)等;四是用于薄片工艺加工,如临时键合技术。

1.衬底材料制备

采用SDB技术可制备各种Si衬底,形成n-/p(n+)或p-/n+衬底结构以代替厚外延技术,用于许多分立器件的制作;也可以制备SOI衬底或者带有深阱区的SOI衬底,用于PIC的制作。

(1)制作Si衬底 采用SDB技术制作Si器件的衬底,可代替三重扩散和外延工艺。制备功率双极型晶体管时,常用传统的三重扩散和高阻厚外延工艺。三重扩散工艺需高温(1150℃)、长时间(数十甚至上百小时)热扩散,会引起硅中大量再生缺陷;采用高阻厚外延工艺,当外延层厚度达到100μm、电阻率为100Ω·cm以上时,所得外延层缺陷多、成品率低、电阻率一致性差,且自掺杂严重影响,这些缺点严重影响器件制备的成本及性能。采用SDB技术,可以克服上述缺点,为功率器件的衬底制备提供一种全新的工艺技术。

(2)制作SOI衬底 通常将两个已生长氧化膜的硅片相贴进行键合后,通过抛光或腐蚀进行减薄,可形成SOI衬底材料。根据减薄技术的不同,可分为键合与背面腐蚀SOI(Bonding and Etch Back SOI,BESOI)技术、键合与等离子辅助化学腐蚀SOI(Plasma Assisted Chemical Etching SOI,PACE SOI)技术及智能剥离(Smart Cut)技术。

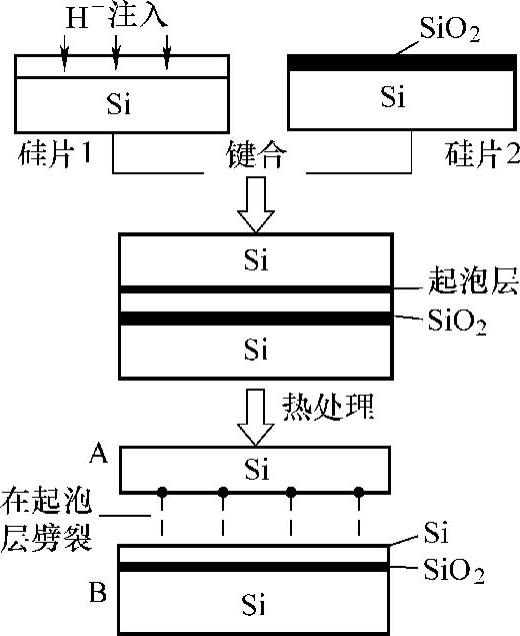

其中,智能剥离技术是离子注入与键合技术的结合,也称单键合SOI(Unibond SOI)技术。1995年由M.Bruel等人提出[68],它是利用H+(或He++)注入在硅中形成起泡层,将注氢片(硅片1)与另一个表面带SiO2支撑片(硅片2)键合,经退火使注氢片从起泡层处完整裂开,形成SOI结构,如图8-36所示。智能剥离技术是利用注氢后退火时起泡剥离来减薄。其中H+(或He++)注入深度由SOI顶层硅膜的厚度来决定;硅片2上热氧化层厚度由埋氧层(BOX)厚度来决定。

图8-36 用智能剥离技术制备SOI材料

采用SDB技术制备的SOI衬底材料,因二氧化硅层是由热氧化生成的,厚度和质量好,不会出现针孔现象;顶硅层是原单晶硅片的一部分,缺陷密度小,质量高,厚度由减薄和抛光工艺决定,可以根据要求进行;该工艺简单,不需要大型的复杂设备,价格便宜,适合大规模生产和应用。目前采用SDB技术形成的SOI衬底[69],已研制出580V的阳极短路SOI-LIG-BT,关断时间为250ns。

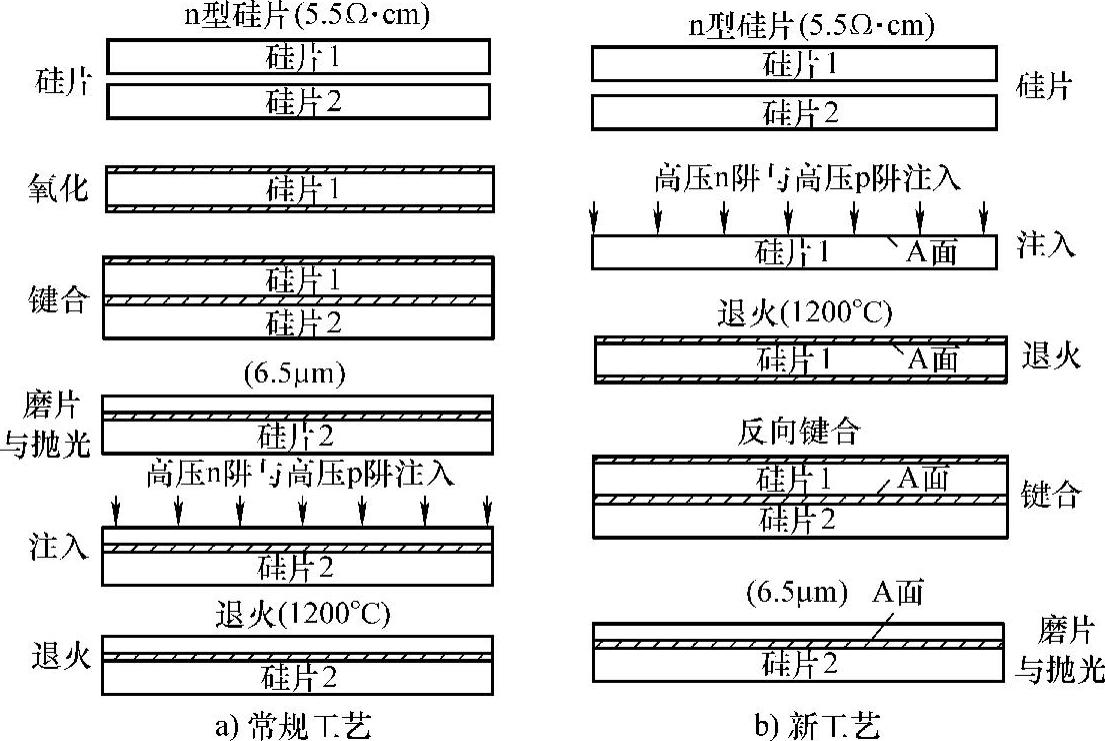

除了制作SOI衬底外,还可以利用SDB技术制作SOI基PIC的高压n阱和p阱等工艺[70]。如图8-37a所示,在常规工艺中,硅片氧化后与另一个硅片进行键合,然后通过磨片与抛光进行减薄,最后通过离子注入制作高压阱,也就是说,高压阱是在SOI衬底制作好之后注入的。如图8-37b所示,在新工艺中,先通过注入形成高压阱,然后将注入过高压阱的硅片1与另一个硅片2进行反向键合。相比较而言,采用常规工艺形成的高压阱区表面浓度比底部高,采用新工艺形成的高压阱区表面浓度比底部低,即所谓倒置阱,有利于提高器件的可靠性。

图8-37 用SDB技术实现SOI基PIC的制作

2.器件制备

SDB技术可用于制作超高压二极管、超高压晶闸管、IGBT及MTO等器件。下面介绍几种器件的制作方法。

(1)用SDB技术制作IGBT对于穿通型(PT)器件结构,在n-区和p集电区之间增加一层低掺杂浓度的n型缓冲层,以提高器件的耐压,并降低饱和电压。缓冲层通常采用扩散或离子注入形成,导致工艺难度和成本较大。对于场阻止(FS)型器件结构,由于nFS层和p集电区是在正面元胞完成后通过注入形成的,退火工艺会对正面的元胞结构及金属化产生严重影响。若采用SDB技术来制作PT-IGBT和FS-IGBT,则工艺大大简化。

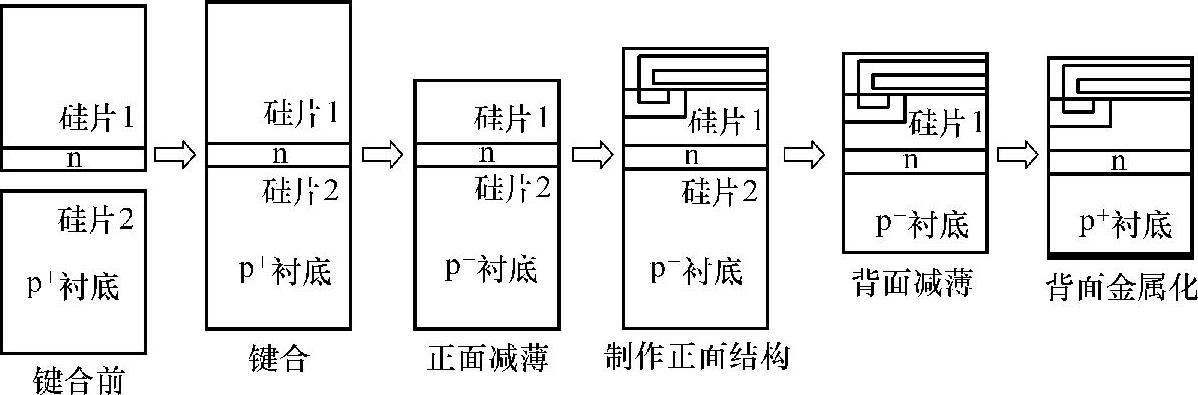

如图8-38所示,采用SDB技术制作平面栅PT-IGBT的工艺过程如下[71]:首先,在n-区熔硅片1上利用磷离子注入形成n掺杂区;然后,将含有n掺杂区的区熔硅片1的n侧与p型直拉单晶硅片2相贴进行键合,可形成掺杂浓度和厚度均满足要求的n缓冲层。接着,将键合片经退火、磨片、化学机械抛光(CMP)后形成约为100μm的n-漂移区,再在n-区上面形成元胞结构及其金属化层,然后减薄背面p衬底,并制作金属化电极。

图8-38 SDB技术制作PT-IGBT的工艺流程

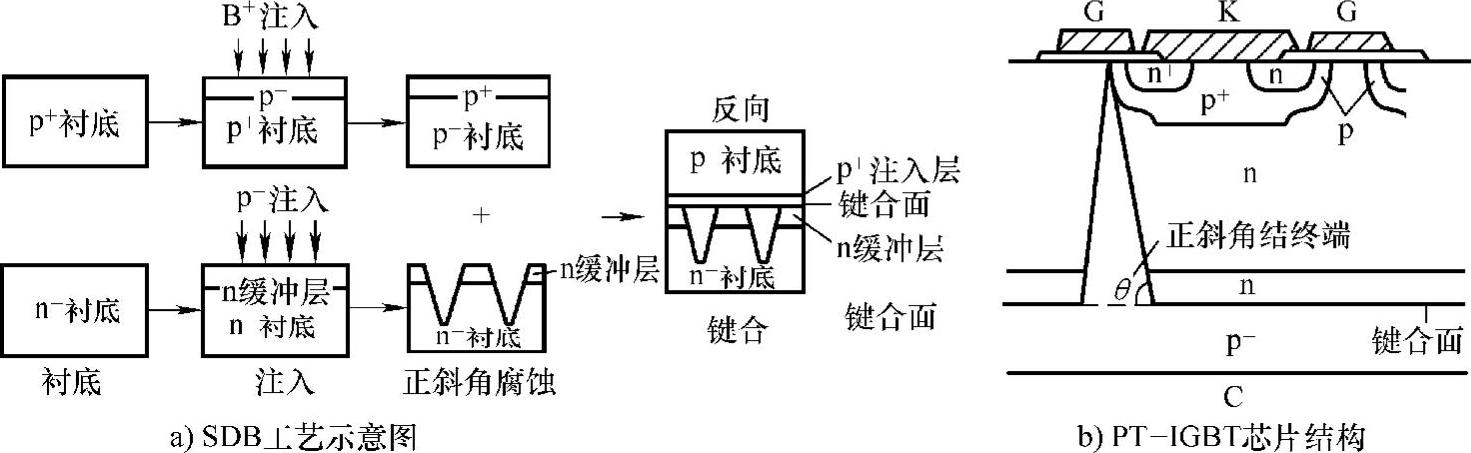

SDB技术也可用于实现具有正斜角终端结构的IGBT[73],如图8-39a所示。先在p+衬底与n-衬底片上分别进行B+和P+注入,形成相应的缓冲层。接着,对n/n-片进行终端正斜角腐蚀,使p++/p+硅片的p++注入层与带腐蚀槽的n-/n硅片的n缓冲层相贴进行键合,然后通过CMP减薄n-衬底,于是形成带有正斜角(45°~85°)和n缓冲层的硅衬底。最后在含有正斜角的硅衬底上,采用大面积的高质量栅氧化、多晶硅栅淀积、自对准进行离子注入等工艺,实现图8-39b所示的IGBT结构。可见,在结终端元胞处自然形成了一个正、反向均带有正斜角为θ的终端结构。(https://www.xing528.com)

图8-39 用SDB技术同时实现正斜角终端和缓冲层的工艺示意图及PT-IGBT芯片结构

图8-40 用SDB技术实现双向IGBT结构剖面

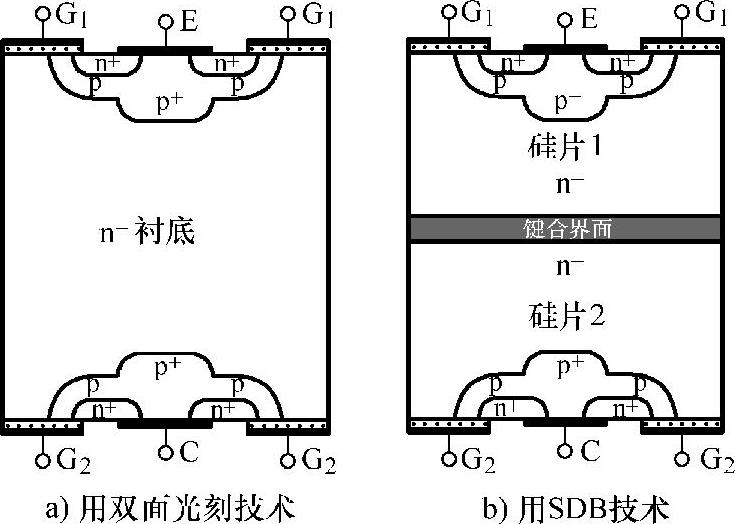

在如图8-40a所示的双向IGBT芯片制作过程中,需采用双面光刻,并需要多次离子注入与退火工艺(如终端的p+场限环、p基区与p+阱区及n+发射区离子注入),且退火温度高达1100℃。若采用SDB工艺,不仅可以省去双面光刻,而且可有效地利用高温退火过程来实现两硅片的高温键合,这与IGBT芯片制作工艺完全兼容[74]。采用高温SDB工艺制作RB-IGBT时,先分别在两个硅片上利用相同的工艺条件实现MOS结构,然后两硅片背面相贴进行键合,如图8-40b所示。这样做有两个优点:一是在相同的条件下实现正面和背面的MOS结构,有利于获得对称的正、反向特性;二是与常规的双面光刻工艺相比,可显著减小高温时间,防止可能出现的污染。其缺点是键合界面会影响器件的导通和阻断特性。

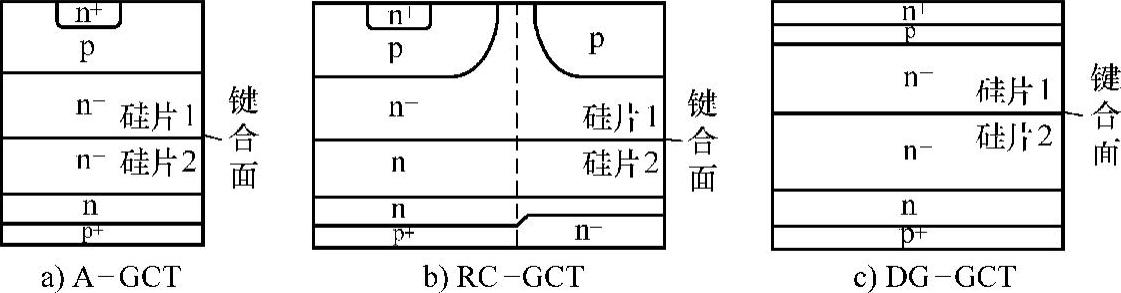

(2)用SDB技术制作GCT 由于非对称GCT(A-GCT,见图3-32a)是一个含有五层n+pn-np+的晶闸管结构,与普通的非对称型晶闸管不同,因其中含有nFS层和透明阳极,其掺杂浓度较低且厚度较薄。采用常规工艺形成A-GCT时,很难精确控制p基区与n FS层及透明阳极区之间的相互影响。若将非对称GCT芯片分为上、下两部分来制作(见图8-41a),进行减薄后利用SDB技术键合成一个完整结构,可大大简化工艺。

逆导GCT(RC-GCT,见图3-32b)是由一个非对称的五层n+pn-np+晶闸管与一个四层的p+n-nn+二极管反并联的集成,FS层和透明阳极的实现也存在上述问题。并且非对称GCT和集成二极管的n+阴极区形成时需要进行双面光刻,所以采用常规工艺制作RC-GCT的难度比A-GCT更大。采用SDB技术形成RC-GCT结构的流程如下:首先,选择两片n-型区熔硅单晶片,硅片1通过两次掺杂先后形成选择性的p基区和非对称GCT的n+阴极区;硅片2先通过磷低温预沉积和主扩散形成n FS层,再通过选择性磷扩散形成集成二极管的n+阴极区,然后利用离子注入形成透明阳极;接着,对两个硅片背面分别进行磨片、抛光,直至n-衬底达到所需的厚度后,再将两个n-衬底面相贴进行高温键合兼退火,便形成图8-41b所示的RC-GCT结构。最后,再进行隔离区和门极区挖槽及电极金属化等工艺。可见,采用SDB形成RC-GCT时,不仅可以避免前后道工艺之间的相互影响,而且不需要进行双面光刻,大大降低工艺难度。

图8-41 用SDB形成A-GCT和RC-GCT及DG-GCT的示意图

双门极GCT(DG-GCT,见图3-33)结构是以中央的n-基区为中心的上下对称结构[59],其中阳极pnp为宽基区(由nn-组成)晶体管,阴极npn为窄基区晶体管,若采用常规工艺来制作,则很难保证两者的基区宽度,而采用SDB工艺控制,则比较简单。如图8-41c所示,首先在n-衬底上通过扩散或离子注入分别形成n-pn+结构(硅片1)和n-np+结构(硅片2);其次,对两硅片的n-侧进行减薄,使n-区达到一定的厚度;再将两者的n-区表面相贴进行键合;最后完成门极挖槽、电极制作等工艺。可见,利用SDB技术来制作DG-GCT,不仅可以简化工艺步骤,降低了工艺难度和成本,而且避免了直接形成五层p+nn-pn+结构的多次高温过程,可大大改善器件的特性。

3.薄片加工

采用SDB技术可实现薄片工艺加工。在FRD、IGBT等器件的制作中,由于芯片太薄,且较脆,在传输和加工过程中容易发生碎片。除了采用真空吸笔、改造芯片夹具及承片台等措施外,还可以采用一种临时SDB技术。它是在硅片正面工序或大部分工序完成后,把硅片减薄,再把薄硅片和一个支撑托片粘接在一起,形成一个“厚”片,继续进行后面的加工工序。等加工完成或部分完成后,再设法把支撑托片拿走或把支撑片磨掉,继续完成后面的工艺。

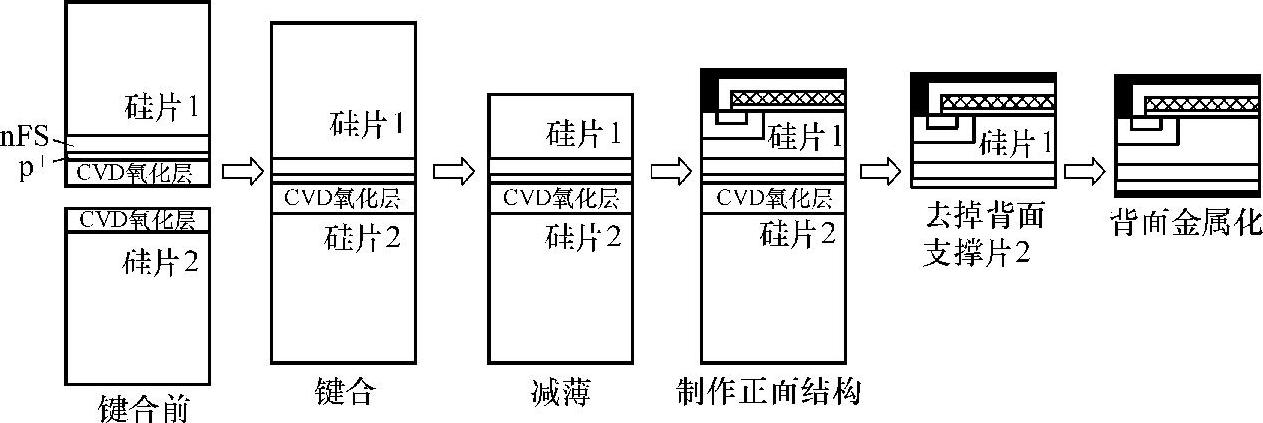

如图8-42所示,采用SDB技术辅助制作平面栅FS-IGBT的工艺过程如下[72]:首先,在硅片1上通过离子注入依次形成nFS层和p+透明集电区,由于没有热条件限制,FS层和p+透明集电区的掺杂浓度和深度可以自由调节。然后,利用化学气相淀积工艺在硅片1、硅片2(支撑片)上分别生长CVD氧化层;接着,将两个硅片的氧化层相贴进行键合,并对硅片1正面进行减薄,厚度和表面质量应符合器件要求;然后在键合片的正面形成元胞结构,不受温度和片厚的限制,可完成正面器件的金属化层及钝化层;之后,利用CVD氧化层作为研磨的阻挡层,磨去背面支撑的硅片2,并保持器件厚度;最后进行背面金属化。可见,采用SDB技术可精确控制n-漂移区及n缓冲层的厚度和掺杂浓度,并降低工艺难度和成本。

图8-42 用SDB技术辅助制作FS-IGBT的工艺流程

4.SDB工艺特点

采用SDB技术制作电力半导体器件,使硅片经历的高温时间缩短,温度相对较低,并可灵活地选择硅片的晶向、掺杂浓度和电阻率,并且能显著简化器件的制作工艺,提高其成品率。当然,SDB技术本身也存在一些缺点,如SDB技术同时需要两个硅片,当芯片厚度较薄时,碎片率增加,都会导致材料成本和工艺成本增加。

用SDB技术制作电力半导体器件是基于成熟的SDB工艺以及比常规工艺更低的工艺成本。当芯片很厚或结构比较复杂时,SDB技术的优越性才会发挥出来。所以,用SDB技术替代传统工艺用来制作超大功率器件或结构复杂的电力半导体器件,可以更好地改善器件的性能、简化其制作工艺,有广泛的应用前景。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。