化学气相淀积(Chemical Vapor Deposition,CVD)是指使一种或多种物质的气体,以特定方式激活后,在衬底表面发生化学反应,并淀积出所需固体薄膜的生长技术。如IGBT芯片制作过程中,多晶硅栅、钝化用的氮氧化硅(Silicon Oxyni-tride,SiON)、磷硅玻璃(Phosphosilicate Glass,PSG)、以及侧墙氧化层(Spacer Oxide)等薄膜,均需采用CVD工艺来制作。与气相外延和热氧化相比,化学气相淀积有许多优点,如温度比较低(600~900℃),淀积膜厚度范围宽(几百埃(Å)~毫米),样品本身不参与化学反应;所淀积的薄膜可以是导体、绝缘体或者半导体材料;淀积膜结构完整、致密,与衬底黏附性好等。

1.化学气相淀积方法

化学气相淀积系统的分类很多。按淀积时的温度分,有低温CVD(200~500℃)、中温CVD(500~900℃);按淀积系统的压强来分,有常压CVD(APCVD)、低压CVD(LPCVD);按淀积系统壁的温度来分,有热壁CVD、冷壁CVD;按淀积反应激活方式来分,有热CVD、等离子增强CVD(13.3~26.6Pa)光CVD及微波CVD等。常用的方法为LPCVD和PECVD。

(1)LPCVD 是指在30~250Pa压强下进行的化学气相淀积。由于系统压强较低,化学反应速率低于反应剂的气相质量传输速率,并且在较低的温度下,淀积速率可以摆脱固体表面解吸与吸附的控制。因此,LPCVD的淀积速率仅受固体表面化学反应的控制。LPCVD可用于制备多晶硅、Si3N4、SiO2、磷硅玻璃(PSG)及硼磷硅玻璃(BPSG)和金属钨(W)膜等。LPCVD制备薄膜时,淀积速率低,温度较高(600~700℃),薄膜的均匀性好、纯度高、膜层绝对误差小及成本低。

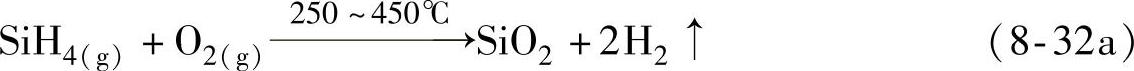

利用低温APCVD或LPCVD淀积SiO2膜可采用硅烷(SiH4)-氧气(O2)体系,化学反应式如下:

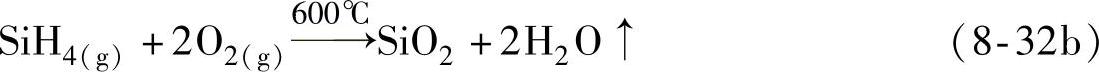

用LPCVD制备SiO2膜时,淀积速度与温度及反应剂分压等有关,可用氮气(N2)来调节系统压强,淀积速率约为200~500nm/min。但淀积膜表面不十分光洁,台阶覆盖差,密度低,需在700~1000℃下增密,并且硅烷遇空气时容易燃烧,存在安全隐患。通常采用正硅酸四乙酯[Si(OC2H5)4](常记为TEOS)与氧气(O2)来淀积SiO2膜,其化学反应式如下:

用LPCVD制备SiO2膜时,淀积速度较低,在TEOS中加入少量的臭氧(O3),可将淀积速率提高到100~200nm/min,并获得均匀的覆盖膜。

(2)等离子增强CVD(PECVD) 是由气体辉光放电的物理过程与化学反应相结合的薄膜生长技术。在一定压力(13.3~26.6Pa)的反应器内加上射频电源,其中的气体分子发生碰撞电离,产生大量的正、负离子,使反应器处于等离子体状态,这些带电离子会发生辉光放电而成为中性粒子,并放出能量。在这种活跃的等离子场中,化学反应在低温下就可发生,于是在衬底表面淀积成膜。

PECVD的突出优点是淀积温度低,淀积速度比LPCVD要快,制备的薄膜具有附着性好、针孔密度低、台阶覆盖好及电学性能好等特点,因此特别适用于金属化后钝化膜和多层布线介质膜的淀积。PECVD常用于制备Si3N4、SiO2、PSG及BPSG等薄膜,对高深宽比沟槽或间隙,可用高密度等离子体化学气相淀积(HDP-CVD),具有良好的填充能力。但PECVD会引起辐射损伤,可通过适当的淀积条件及低温退火来消除。

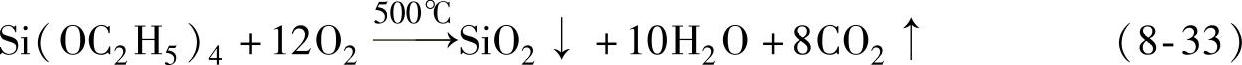

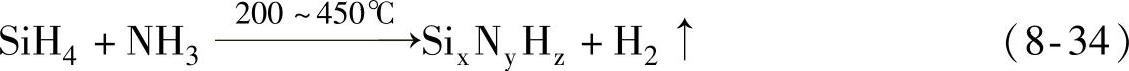

利用PECVD制作Si3N4膜,常用硅烷(SiH4)-氨气(NH3)-氮气(N2)体系,其化学反应式如下:

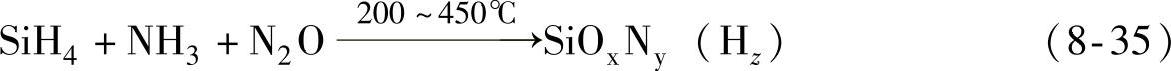

SiON膜的性能介于氮化硅与氧化硅之间,可用硅烷(SiH4)-氨气(NH3)-笑气(N2O)体系,其化学反应式如下:(https://www.xing528.com)

由于SiO2膜具有压应力(Compressive Stress),Si3N4膜具有张应力(Tensile Stress),故SiOxNy(Hz)膜应力接近于零,作为钝化层可用以防潮和防污染。

在功率MOSFET与IGBT芯片制作中,多晶硅平面栅采用LPCVD制作,多晶硅沟槽栅、侧墙氧化层及SiON、PSG钝化膜则采用PECVD来制作。

2.台阶覆盖

在薄膜淀积过程中,由于芯片表面存在台阶,导致薄膜在芯片表面各处覆盖的厚度均不相同。根据表面的覆盖情况,可分为保形覆盖和非保形覆盖。理想的覆盖为保形覆盖,即芯片表面各处覆盖膜厚完全相同。若形成非保形覆盖,会造成金属布线在台阶处开路或无法通过较大的工作电流。所以台阶覆盖(Step Coverage)是薄膜的重要特性。

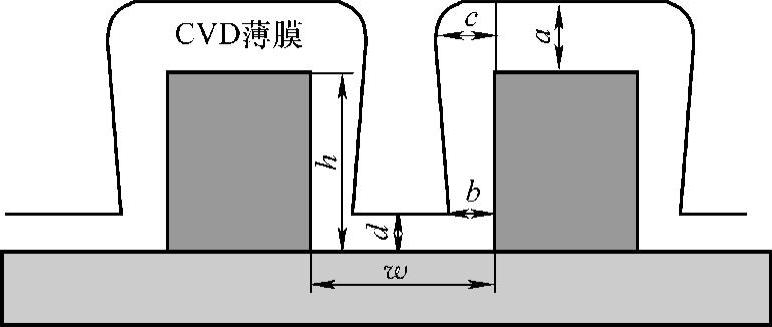

图8-19给出了晶片经CVD后表面台阶覆盖剖面的示意图。台阶覆盖形状可用侧壁台阶覆盖(b/a)、底部台阶覆盖(d/a)、共形性(b/c)、悬突((c-b)/b)以及深宽比(h/w)五个特征量来描述。其中a为台阶上表面处的纵向膜厚,c为台阶上侧壁处的横向膜厚,b为台阶下侧壁处的横向膜厚,d为台阶下表面处的纵向膜厚。通常台阶覆盖是指侧壁台阶覆盖,保形覆盖时侧壁台阶覆盖(b/a)等于1。

图8-19 晶片经CVD后表面台阶覆盖剖面的示意图

3.通孔填充

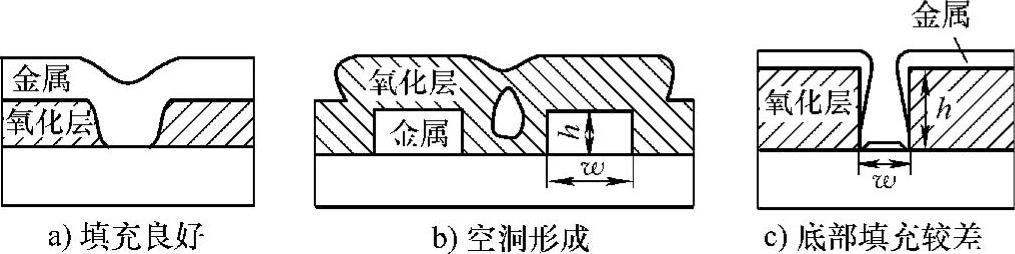

在HVIC多层布线的制作过程中,存在通孔填充问题。通孔填充与台阶覆盖均取决于CVD反应剂向衬底表面的输运机制,包括直接入射、再发射及表面迁移,其中表面迁移起决定性作用,再发射也很关键。覆盖情况主要与反应物或中间产物在晶片表面的迁移、气体分子的平均自由程及台阶的深宽比等因素有关。当反应物或中间产物在晶片表面能迅速迁移时,晶片表面的反应物浓度处处均匀,与几何尺寸形貌无关,就得到厚度均匀的保形覆盖和理想的通孔填充,如图8-20a所示。当吸附在晶片表面的反应物不能沿表面明显迁移且气体平均自由程大于台阶宽度时,淀积膜在间隙入口处产生夹断现象,导致在间隙填充中出现空洞,如图8-20b所示。当没有表面迁移、平均自由程又较小时,在台阶顶部弯角处产生较厚的淀积,而底部淀积得很少,如图8-20c所示,底部填充较差。

图8-20 通孔填充情况示意图

为了改善台阶覆盖与通孔填充效果,在晶片表面淀积金属膜时,可采用多源淀积、旋转晶片或增加校准器等方法;也可以采用高密度等离子体化学气相淀积(HDP-CVD)或淀积-刻蚀-淀积交替工艺。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。