SOI衬底自20世纪90年代以来,广泛用于功率集成电路(PIC)。第6章中已经介绍了SOI基的功率器件和功率集成电路。本节主要介绍SOI衬底的制作方法。

1.SOI衬底的特点

SOI衬底采用三明治结构,根据顶层硅膜的厚度和掺杂浓度不同,可分为厚膜SOI材料和薄膜SOI材料[5]。厚膜SOI材料是指顶层硅膜厚度大于2Xdmax(Xdmax为最大耗尽区宽度),可达几十微米,正面、背面耗尽区之间不相互影响;薄膜SOI材料是指硅膜厚度小于Xdmax,只有几个微米甚至更小(0.25μm),硅膜可全部耗尽而不取决于背栅电压。中等膜厚SOI材料是处于厚膜和薄膜之间的SOI材料,其膜厚和掺杂将对SOI器件击穿电压产生影响。

在PIC中,采用SOI材料与体硅材料相比,有以下特点:一是可以有效地实现高、低压器件之间的隔离,彻底消除电干扰,简化器件设计,便于集成不同的电路和器件;二是可用于制作耗尽型器件,漏电流小,栅压对漏电流的控制能力强,亚阈值斜率较小,可获得更好的频率特性;三是可用于制作在辐射、高温、低温等恶劣环境中工作的器件;四是SOI基PIC的隔离区面积小,可以节约芯片面积,减小寄生电容。

2.SOI衬底制备方法

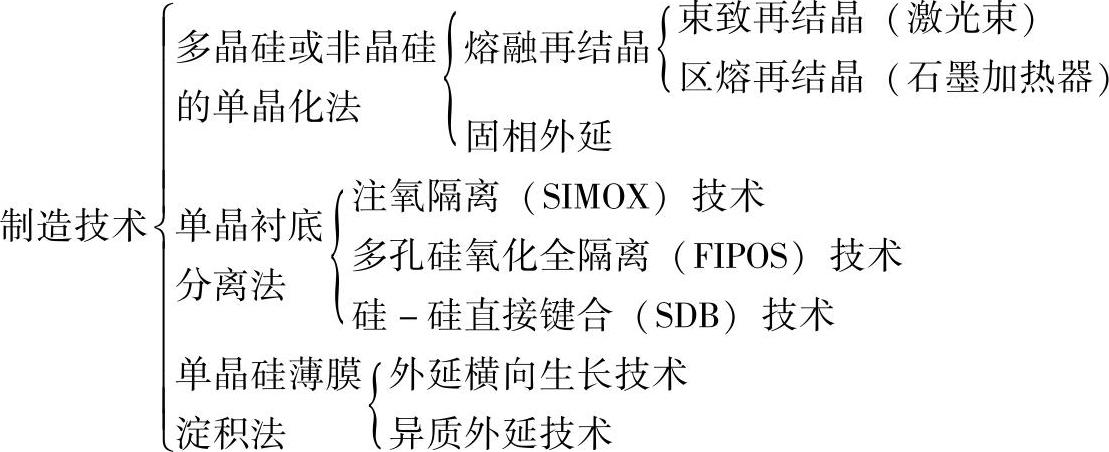

SOI衬底的制备有多种方法,见表8-1[6]。它包括多晶硅或非晶硅的单晶化法、单晶衬底分离法及单晶硅薄膜淀积法。其中,常用的方法是单晶衬底分离法,包括注氧隔离(Separation-by-Implantation of Oxygen,SIMOX)技术[7]、多孔硅氧化全隔离(Full Isolation by Porous Oxidized Silicon,FIPOS)技术[8]及硅-硅直接键合(SDB)技术[9]。(https://www.xing528.com)

(1)注氧隔离(SIMOX)技术 是用能量为(150~200)keV、剂量为1.8×1018cm-2的O+注入到硅衬底中,在1300℃高温以上经5~6h退火后,在硅表面以下形成几百纳米的埋氧层,从而形成有三层结构的SOI材料。与注氧退火形成埋氧层一样,也可以进行注氮隔离(SIMNI),即用能量为(160~200)keV、剂量为1.1×1018cm-2的氮离子(N+)注入到硅衬底中,经退火形成绝缘层为氮化硅(Si3N4)的SOI结构。

表8-1 SOI衬底材料的制造技术

(2)多孔硅氧化全隔离(FIPOS)技术 是在多孔硅(指内部含有许多空洞的单晶硅)上先生长常规的单晶硅;然后通过腐蚀顶层硅达到多孔硅层,再对隐埋的多孔硅层进行等厚的阳极氧化而形成埋氧层。该技术需要用分子束外延(MBE)或等离子体化学气相淀积(PECVD)来精确控制单晶硅膜的生长,成本较高,现已用于大规模集成电路及薄膜SOI基器件的制备。

(3)硅-硅直接键合(SDB)技术 是指将两片已经生长氧化膜的硅片进行键合,然后通过抛光和腐蚀进行减薄,从而形成SOI衬底材料。与前两种制备方法相比,采用SDB技术制备的SOI材料有很多优点:一是工艺简单,不需要大型的复杂设备,故成本低,适合大规模生产和应用;二是埋氧层是由热氧化生成的,厚度和质量好,不会出现针孔现象;三是顶层硅是原单晶硅片的一部分,缺陷密度小,质量高,且厚度由减薄和抛光工艺决定。所以,完全适用于SOI基PIC的制作。关于硅-硅直接键合技术的原理与方法将在8.4节中详细介绍。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。