对于功率MOSFET、IGBT等器件,由于结深较浅(通常小于8μm),这意味很难采用机械研磨的方法来形成台面结终端。目前,这类器件大多采用场限环结终端或场限环与场板的复合结终端。当击穿电压要求较高时,采用这些结终端结构所需的结终端尺寸或面积很大,导致芯片面积的有效利用率很低。因此,需要寻求新结终端结构,以满足实际需求。下面介绍两种适用于浅结MOS器件的台面结终端结构。

1.浅沟槽负斜角结终端

如图7-28所示,图中点画线所围的区域为功率MOSFET芯片结终端区。在主结p区的末端处,通过刻蚀工艺形成了一个两侧垂直、底部为大V形的负斜角台面结终端结构。与传统的负斜角不同之处在于,深入到n-区的沟槽深度很浅,以保证芯片有足够的机械强度。采用感应耦合等离子体(ICP)刻蚀可以精确控制沟槽刻蚀的深度,同时用氮化硅进行沟槽钝化[34],可以减小漏电流。

图7-28 浅沟槽负斜角结终端结构示意图

在阻断期间,因沟槽底部存在负斜角θ,为了达到电荷平衡,n-区的空间电荷区向V形槽壁收缩,如果能保证空间电荷区的展宽在槽壁斜面上,则该处的电场集中将被有效缓解,器件的击穿电压就可提高。由于p区很浅,不能为耗尽区提供足够的扩展宽度空间,所以需要对pn结两侧空间电荷区的电荷量加以有效控制。图7-28中的负斜角是为了扩展空间电荷区,以降低表面电场强度,浅沟槽是为了限制空间电荷区的电荷量。因此,沟槽深度和宽度变化都会改变空间电荷区的电荷量及空间电荷区的扩展宽度,从而影响器件的结终端耐压。设计时,沟槽深度可控制在p区一侧空间电荷区内靠近边界处。如果沟槽底远离其边界,不利于电荷控制;如果沟槽底进入空间电荷区内部太深,则沟槽拐角处会发生电场集中,使器件的击穿电压大幅下降。所以,通过合理地设计沟槽深度d1、沟槽宽度w、负斜角θ及斜面高度d2等参数,可以实现器件耐压与芯片面积之间的折中选择。

功率MOSFET采用浅槽负斜角结终端时,击穿电压UBRS随各参数的变化曲线如图7-29所示。可见,UBRS随沟槽深度d1的增加先增大后减小,且当d1为3.5μm时,UBRS达到最大值630V;UBRS随沟槽宽度w的增加而增加,但增加幅度逐渐减缓;UBRS随斜角增加先迅速增加后逐渐减小,且当θ为4°时,UBRS达到最大值630V;UBRS随斜面高度d2的增大而减小。

相比较而言,沟槽深度d1是UBRS的敏感参数,其值取在p区空间电荷区内靠近边缘处最好。斜角θ对器件面积的影响很大,斜面高度d2则主要取决于耐压要求。理论上,可通过加大沟槽宽度w来使器件击穿电压接近于平行平面结击穿电压,但这不仅会增大芯片结终端区的面积,而且会导致反向漏电流增加,使器件特性变差。如果能够保证沟槽内的钝化层在划片过程中不会碎裂,则沟槽宽度w会减半,这会大大减小结终端尺寸,提高芯片面积的有效利用率。

图7-29 终端击穿电压随沟槽参数的变化

2.深沟槽斜角结终端

深沟槽斜角结终端结构如图7-30所示[42,43],是在VDMOS最外侧元胞的pn结弯曲处,通过特殊的刻蚀工艺,形成一个与表面法线方向夹角为θ的斜角沟槽,并在沟槽底部通过硼离子注入形成一个p+区,相当于场限环。根据θ角的大小和沟槽形状不同,可分为正斜角、直角和负斜角[44]。在外加电压下,p+n结两侧的空间电荷区扩展宽度主要在轻掺杂的n-区一侧。如果沟槽设置合适,沟槽壁可阻挡部分电力线,其余大部分的电力线则聚集在沟槽拐角附近。在沟槽底部设置一个p+区,使体内平行平面结发生击穿前恰好全部耗尽,于是超出沟槽深度的电力线就会沿沟槽底部均匀分布,可有效缓解沟槽拐角处的电场集中。(https://www.xing528.com)

图7-30 不同角度的深沟槽斜角结终端结构

由于受到沟槽侧壁的平整度、表面电荷、沟槽造型及填充绝缘介质的质量等因素影响,器件很容易在槽壁p+/n结截止处及沟槽拐角处发生击穿,导致器件的击穿电压下降。为了提高器件的击穿电压及稳定性,需缓解沟槽壁及拐角处的电场强度集中,使击穿稳定发生于体内。采用如图7-30a所示的深沟槽正斜角结终端,可使低掺杂浓度一侧的空间电荷区展宽,有效缓解p+/n结截止处的电场强度集中,同时沟槽底部的p型掺杂则可缓解沟槽拐角处的电场强度集中。但采用现有的刻蚀工艺很难得到理想的正斜角结构,而通常会形成如图7-30b、c所示的直角沟槽或负斜角沟槽。

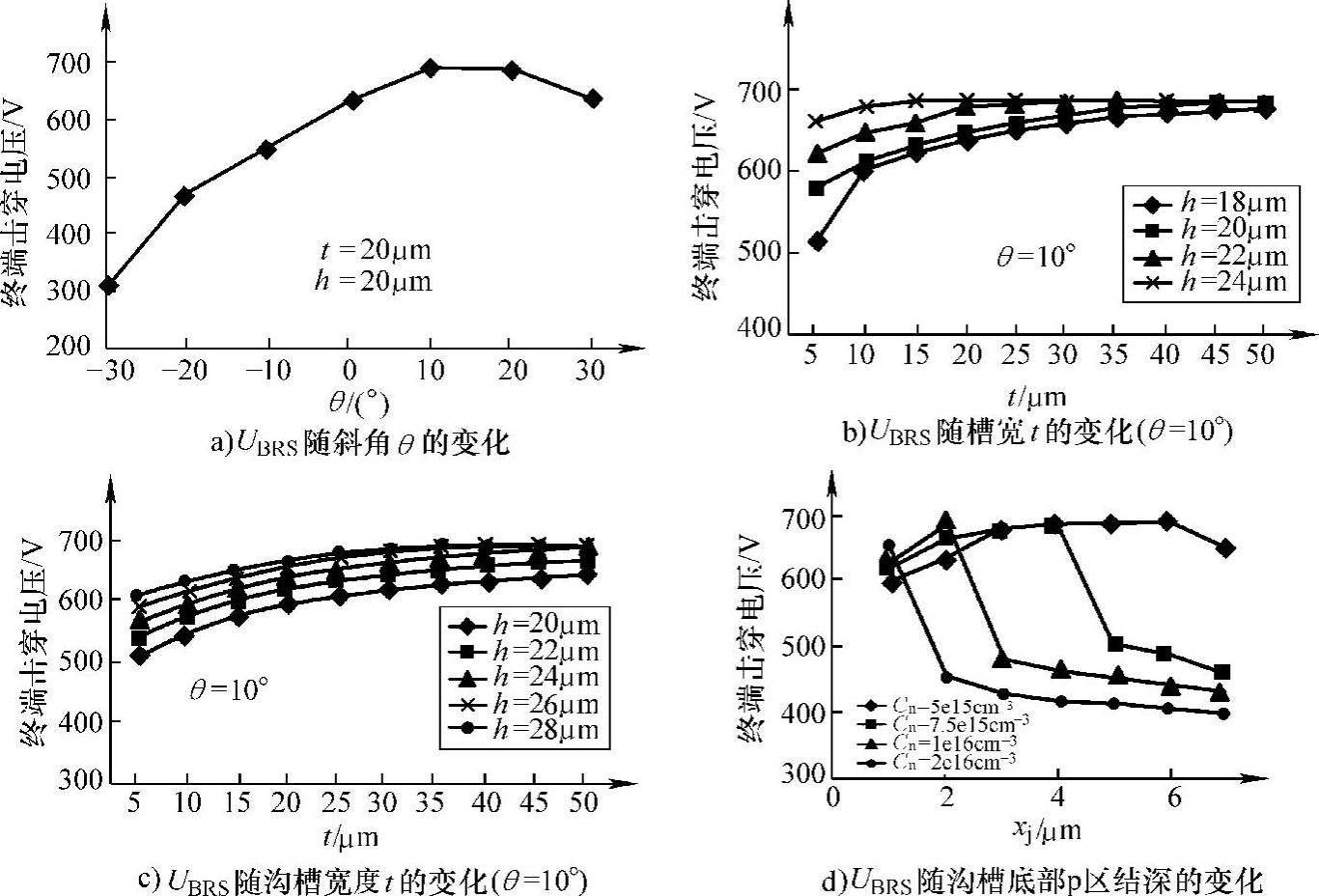

终端击穿电压UBRS随斜角θ的变化曲线如图7-31a所示,当斜角θ从-30°到30°之间变化时,UBRS先增大后减小,且当斜角θ为10°时,UBRS有最大值;如图7-31b所示,当θ为10°、沟槽宽度t一定时,UBRS随沟槽深度h的增加而增大,但增加幅度随沟槽宽度t增加而逐渐减小;当沟槽深度h一定时,UBRS随沟槽宽度增大而增大,并逐渐趋于稳定;如图7-31c所示,当θ=0°时,UBRS随沟槽参数变化曲线的趋势与θ为10°时保持一致;如图7-31d所示,当Cs为5×1015cm-3、xj为2μm时,UBRS保持较高的值。若杂质剂量过高,p+区不能完全耗尽,电场集中于沟槽外侧拐角处,导致击穿电压降低;若杂质剂量过低,耗尽的p+区对槽底的电场集中起不到很好的缓解作用,沟槽内侧拐角处将首先发生击穿,也会导致击穿电压下降。所以,槽底p+区的杂质剂量需严格控制。

表7-1给出了三种深槽斜角结终端结构的特征参数比较。比如要实现约600V的终端击穿电压,采用正斜角时所需的沟槽深度和宽度均比直角或负斜角时要小。在实际刻槽时,要形成一定正斜角且表面平整的深槽,工艺难度较大。综合考虑芯片的耐压效率、结终端面积及制作工艺等来选取沟槽深度、宽度、角度及槽底p型区的表面掺杂浓度与结深。研究表明,当耐压效率为85%时,采用深槽正斜角结终端尺寸需25μm,约为场限环结终端尺寸的13.9%,为浅槽负斜角结终端尺寸的27.8%。

图7-31 击穿电压UBRS随关键结构参数的变化

表7-1 三种深槽斜角结终端结构比较

深槽斜角结终端结构优点在于所占用芯片面积较小,这与PIC追求高效、高集成度、小芯片面积的设计理念极为相符。所以这种深槽斜角结终端结构可用于PIC中来提高横向器件的终端击穿电压。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。