1.台面终端结构

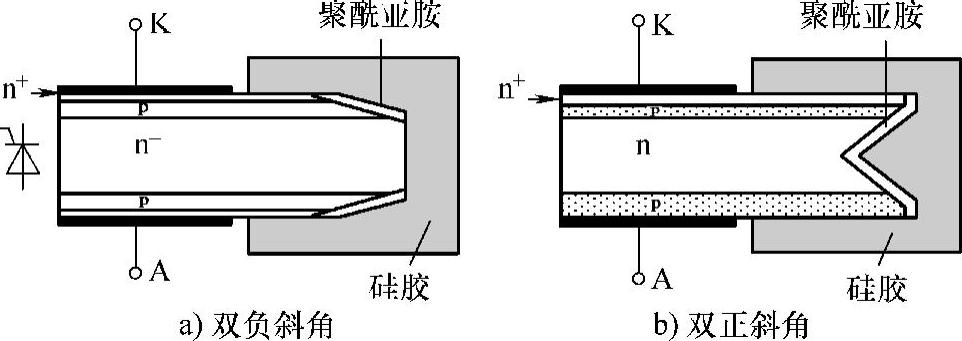

对于低压晶闸管,常用正负斜角结终端;对超高压晶闸管,常用双正斜角或双负斜角结终端。对于焊接式晶闸管,由于采用烧结工艺形成阳极接触,在阳极欧姆接触形成后,采用磨角工艺形成正负斜角,工艺简单,成品率较高。对于压接式晶闸管,由于芯片两侧的电极是通过蒸铝形成的,因而常用双正斜角或双负斜角,如图7-20所示[26]。管芯磨角后,经腐蚀去除掉表面的机械损伤层,然后用很薄的聚酰亚胺(Polyimide)膜钝化腐蚀过的斜面,最后外面涂覆硅胶(Silicon Rubber)进行保护。

图7-20 晶闸管常用的台面结终端结构剖面

台面结终端结构设计关键是斜角的大小及结终端截止的位置。采用双斜角结终端时,通常还会在最外侧设计一个包围整个器件的特别短路区,可以将在周边区域内流动的任何位移电流分流至阴极。

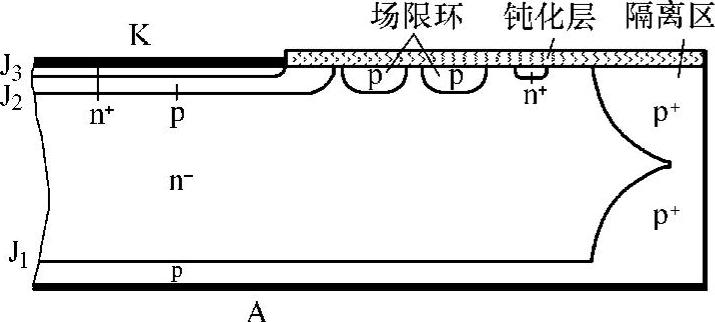

图7-21 方芯晶闸管采用FLR结终端结构剖面

2.平面结终端结构

除了上述的台面结终端结构外,晶闸管也可采用平面结终端结构,如场限环和横向变掺杂(VLD)结终端。

(1)场限环结终端结构 对具有正、反向阻断能力的方芯晶闸管而言,除了采用图7-9所示的双面沟槽结构外,还可以利用深扩散形成图7-21所示的场限环结构。上面的J2结外侧设置了场限环(FLR)和沟道截止环,下面的J1结与p深扩散区连通,相当于结终端延伸。芯片制作时,首先在芯片两侧同时进行p区深扩散,直至将两侧的p区连通,芯片做成后可以在连通的p扩散区进行划片。该扩散结终端结构的优点是,终端区的制作工艺与有源区工艺相兼容,只需要在芯片的单边进行光刻工艺即可。IXYS公司的晶闸管和二极管方形芯片多数采用这种结终端结构[36]。此外,图5-43所示的RB-IGBT也可采用这种深扩散结终端结构,以实现正、反向阻断能力[26]。(https://www.xing528.com)

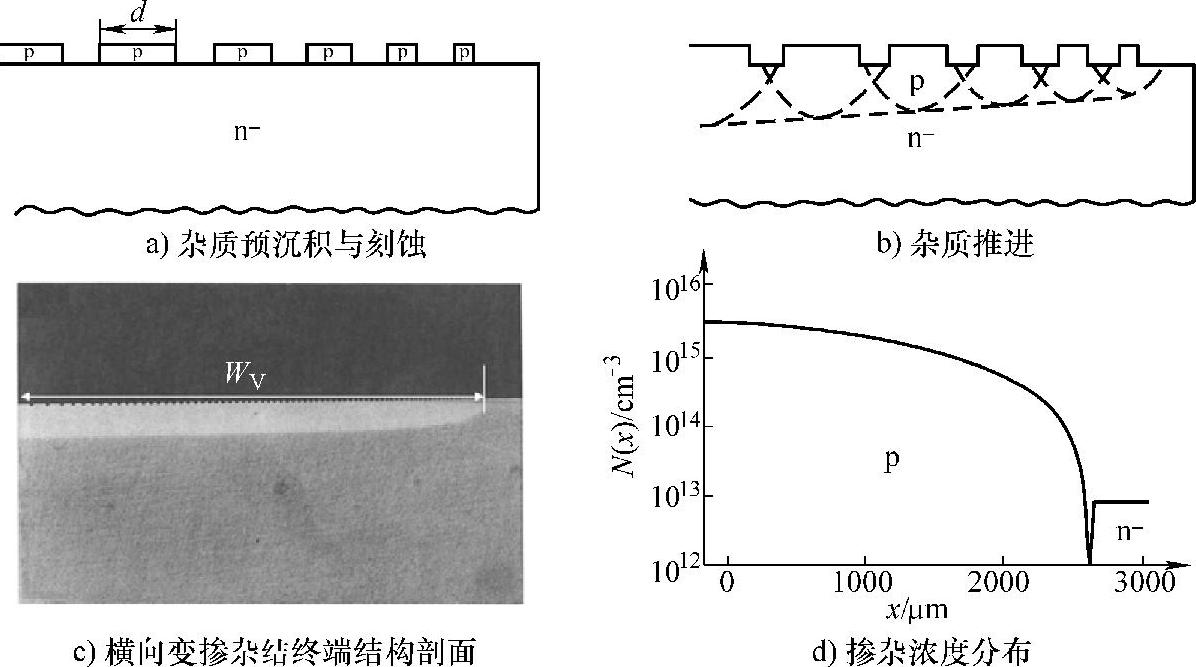

(2)横向变掺杂结构 图7-22给出了晶闸管所用VLD结构、制作工艺流程、结构剖面及掺杂浓度分布[37]。可见,它是在n-衬底上先淀积一薄层铝杂质源,然后刻蚀掉部分杂质源(图7-22a中,d表示表面预留的杂质源尺寸),在高温下进行扩散。由于硅片表面预留的杂质源剂量不同,高温推进后的结深就不同(见图7-22b),由此得到结深缓变的横向变掺杂结构。图7-22c所示为扩散后测试的掺杂剖面,其中WV是横向变掺杂区的宽度,图7-22d所示为对应的横向掺杂浓度分布。

图7-22 横向变掺杂结终端结构剖面、掺杂浓度分布及制作流程

采用该平面结终端结构可实现不同的耐压效果。当电阻率分别为500Ω·cm、270Ω·cm及90Ω·cm时,VLD区的宽度WV与n-区空间电荷层最大宽度WD之比(WV/WD)分别可达2.08、3.33及7.91,对应的终端击穿电压可达9.1kV、6.1kV及3.4kV,分别为理想体击穿电压的89%、95%及100%。这说明当击穿电压较低时,VLD结终端结构的耐压效率较高;当击穿电压较高时,其耐压效率会下降。

深结横向变掺杂结终端结构设计的关键是杂质剂量的控制。预留的杂质剂量由尺寸d决定,从内到外逐渐减小,最小尺寸受制于光刻精度的限制;同时p薄层的厚度(即预沉积的铝源总量)也很关键。此外,横向变掺杂的剖面还与推进的工艺条件有关,由于铝扩散比较特殊,其表面掺杂浓度远低于铝在扩散温度下的固溶度。可见,采用这种扩散方法形成深结的VLD结构,工艺难度很大。采用铝离子注入来实现,可以大大降低其工艺难度。

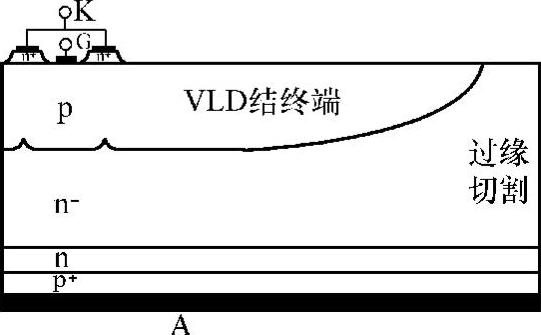

GCT所用的VLD结终端剖面如图7-23所示[9]。有源区采用波状p基区结构,可以改善其反偏安全工作区(RBSOA)。终端区设计为VLD结构,可以优化器件的高温性能。波状p基区是在n+阴极区的掩蔽下,通过铝注入形成的。所以,利用n+阴极区掩蔽在结终端区很容易实现p基区的横向变掺杂,从而解决了选择性铝扩散问题。该结终端结构设计的关键是n+掩蔽区的尺寸及间距,其间距决定了杂质源剂量。采用铝注入形成的VLD结构,其杂质源剂量与注入剂量有关,得到的掺杂剖面也与推进条件有关。

图7-23 GCT采用的VLD结终端剖面

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。