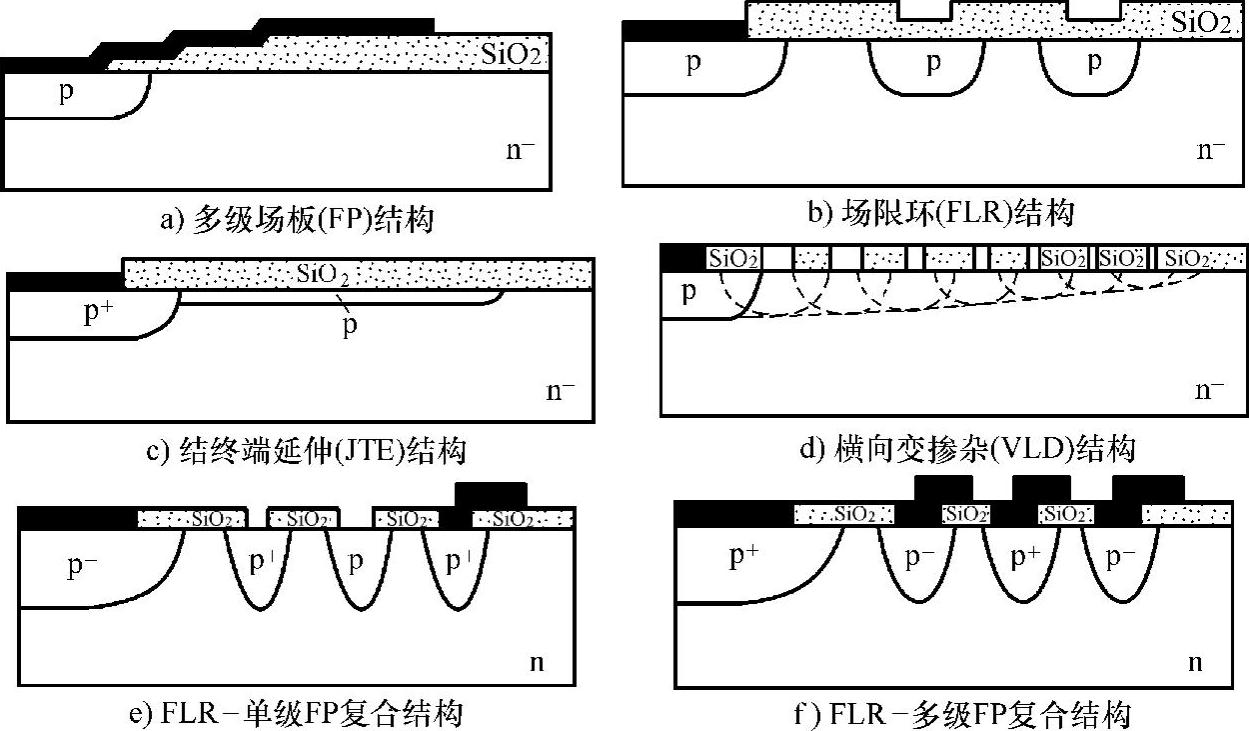

常用的结终端结构如图7-1所示[1]。图7-1a所示是场板(FP)结构,图7-1b所示是场限环(FLR)结构,图7-1c所示是结终端延伸(JTE)结构,图7-1d所示是横向变掺杂(VLD)结构,图7-1e、f所示是场限环-场板(FLR-FP)复合结终端结构。

1.场板技术

如图7-1a所示,场板是把金属电极条扩展到扩散区表面的氧化层上,当pn结加反偏电压时,金属电极为负电位,可以抵消氧化层中正电荷对表面的影响,并且排斥表面电子,使表面耗尽区在Si及SiO2界面处展宽,从而提高击穿电压。按场板级数的不同,可分为单级场板与多级场板。按场板的材料不同,可分为金属场板、半绝缘多晶硅场板等。按场板的位置不同,可分为接触式场板和浮空场板[2],目前多采用接触式场板结构。

图7-1 常用的平面结终端结构

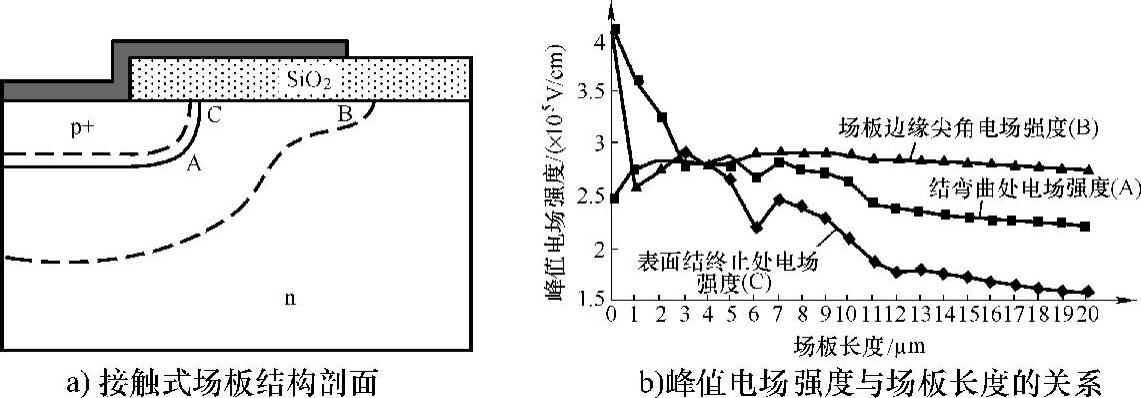

在图7-2a所示的接触式场板结构中,金属场板与阳极连为一体覆盖在较厚氧化层上,相当于与pn结并联一个MOS电容,电容承担的电压会在半导体表面产生耗尽区,与pn结耗尽区连为一体,使得pn结表面电场强度分布更加平缓。所以,采用场板可减小主结结面弯曲处的电场强度,从而提高终端击穿电压(即表面击穿电压)。

图7-2 接触式场板结构及其峰值电场强度与场板长度关系曲线

终端击穿电压与场板长度、氧化层厚度有关。当场板长度一定时,终端击穿电压随氧化层厚度的增加而增加。场板的长度也需进行优化,场板过短,不能达到改善表面电场强度分布的目的;场板过长,击穿点将出现在表面,器件可靠性下降,且占用面积过大。图7-2b给出了n区掺杂浓度为2×1014cm-3、氧化层厚度为1μm、界面电荷密度为1×109cm-2时,体内及表面峰值电场强度与场板长度之间的关系[3]。可见,当场板长度较短时,表面结终止处(C)、结弯曲处(A)、场板边缘处(B)电场强度相互影响,击穿情况复杂。当场板长度大于13μm,各处的峰值电场强度趋于稳定,故优化的场板长度应在10μm以上。

由于场板边缘处(B)与硅之间的电势差较大,导致该处电场强度较高,在此表面处容易发生过早击穿,故要求介质层的质量要高。场板技术适用于耐压低于250V的分立器件及功率集成电路。对于3.3kV左右的分立器件,多采用场板与场限环的复合结终端结构。

2.场限环技术

如图7-1b所示,场限环结终端结构是在有源区外侧,设置与主结有完全相同掺杂浓度分布的环结,以缓解pn结弯曲处电场集中,提高终端击穿电压。根据器件耐压需要,可采用一个或者若干个场限环。

当在电极上加反向电压时,由于场限环是浮置的,与主结及其他电极并无电接触。随着反向电压逐渐增高,主结的耗尽区也随之向外扩展。当主结的耗尽区扩展到与相邻的第一个场限环穿通后,主结附近的最大电场强度便可降低,第一个环将承担继续增加的反向电压,直到逐渐增大的耗尽区与下一个环穿通。由于在主结发生雪崩击穿之前,主结的耗尽区已扩展到所有环结,耗尽区展宽显著增大,使主结弯曲处的高电场被削弱,击穿电压得以提高。场限环的存在相当于在主结上串联了一个分压电阻,使主结上承受的电压降低,故场限环也可称为分压环。

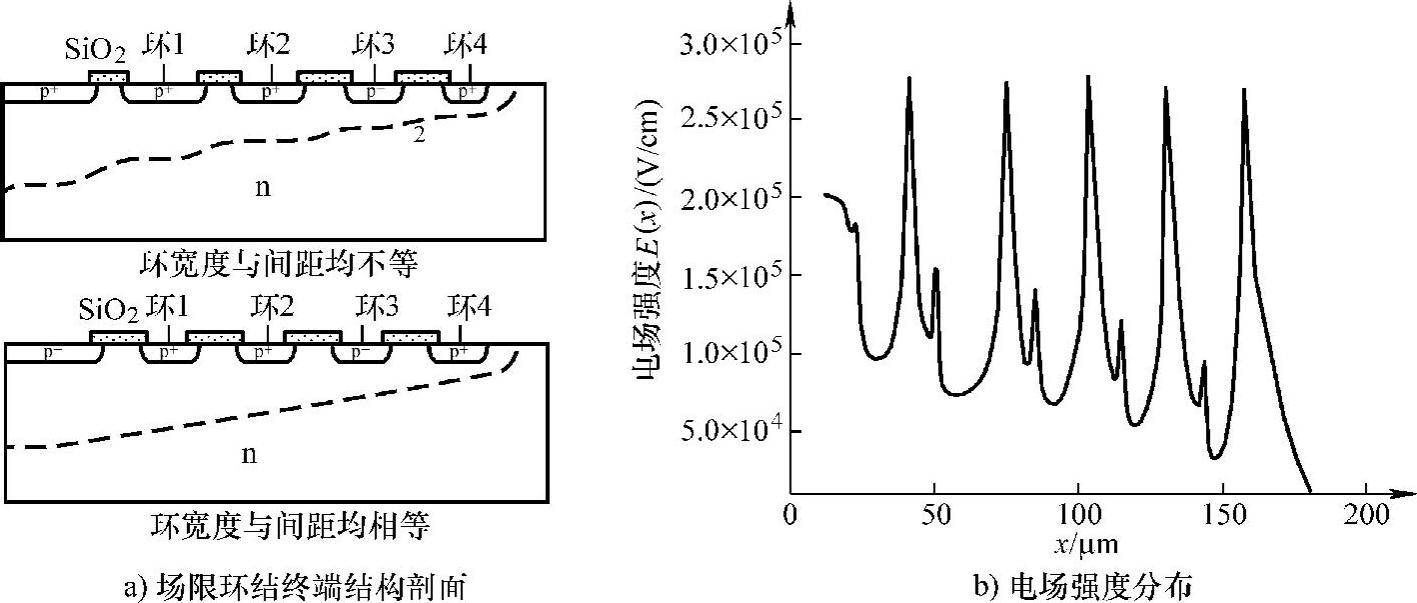

场限环的结深、间距、环宽度及个数都会影响击穿电压的高低。结深越浅,pn结的电场强度峰值越高,击穿电压则越低。比如当圆柱pn结的结深从10μm减小到2μm时,电场强度峰值从2.6×105V/cm增加到3.4×105V/cm,击穿电压则从250V下降到150V。如果间距设置合适,主结与环结可以同时达到临界击穿电场强度,此时终端击穿电压最高。随着环数的增加,击穿电压虽呈非线性增加,但场限环占用的面积也越大。所以,设计场限环时,既要考虑提高终端击穿电压,也要考虑终端区占有的芯片面积,需要对环间距、环宽度、衬底掺杂浓度、扩散环的掺杂浓度、结深、氧化层电荷密度等因素进行综合考虑。需注意以下两个问题:一是尽可能增加pn结的曲率半径,曲率半径越大,耐压能力就越强。二是合理设计环宽度和环间距。环宽度取决于该环承受的电压及p区的掺杂浓度,环间距决定了该环是否能有效地起分压作用。环间距偏小,后一个环将承受高的电压;反之,前一个环将承受高的电压。环间距太大时,击穿将会发生在前一个环上,后一个环不起分压作用。环间距与环宽度的设计通常有两种方法[4]:一是环宽度和环间距各不相等。如图7-3a所示,环宽度由内向外逐渐减小,对应的环间距则逐渐增加。假设主结与环结的扩散深度为xj,则最外环宽度一般取(2~2.5)xj[5],其他则按照环宽度由内向外递减、环间距由内向外递增原则,并基本保持每个环间距与环宽度之和为定值。这种方法特别适用于深结(xj>10μm)器件。二是采用等环间距与等环宽度,如图7-3b所示,这种方法较适合浅结(xj<10μm)器件。相比较而言,采用相等的环宽度和间距设计,可以减小结终端尺寸,并获得更好的渐变耗尽区。

利用场限环解析模型可以对电场强度进行计算,其结果与实际也比较接近,但是计算过程复杂。目前,利用器件模拟软件通过数值分析进行场限环的优化设计非常方便。图7-3b给出了按环间距与环宽度不相等设计的场限环结终端结构发生击穿时的电场强度分布[3]。可见,通过合理地选取环间距和环宽度,让每个环结分担尽可能相等的电压,并使主结和各环结上的峰值电场强度接近,且主结上的电场强度稍低,这样可以保证环结先于主结击穿,从而达到保护主结的目的。

(https://www.xing528.com)

(https://www.xing528.com)

图7-3 场限环结终端结构剖面及电场强度分布

场限环可以与主结同时扩散形成,无须增加工艺步骤,故工艺十分简单。采用场限环技术,可以达到较高击穿电压(约为平行平面结击穿电压的90%以上),但参数设计比较苛刻,对界面电荷也非常敏感,并且当耐压较高时,占用芯片表面积很大,导致其反向漏电流也很大。因此,场限环技术常用于耐压为1.2kV左右的器件。采用场限环与其他技术形成的复合结终端结构,不仅可以提高器件的耐压及稳定性,而且可以减小结终端尺寸。

3.结终端延伸技术

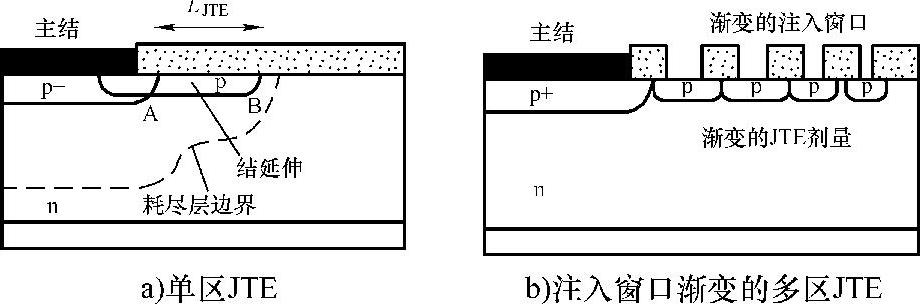

结终端延伸(JTE)结构是1977年由Temple提出的[6]。它是在有源区重掺杂的主结外侧,利用离子注入工艺形成一个低掺杂浓度、较浅(约1μm)的掺杂区,使pn结沿器件的表面得以扩展。根据耐压高低,可分为单区和多区,如图7-4所示[4]。

图7-4 结终端延伸结构

当pn结反偏时,p延伸区全部耗尽,耗尽区沿着表面向外扩展,如果延伸区长度LJTE大于主结的耗尽区扩展宽度,则表面电场强度会降到主结的峰值电场强度以下,从而达到提高击穿电压的目的。但如果延伸区厚度太薄,无法有效改善结弯曲处的电场强度分布,则不利于提高击穿电压。如果延伸区深度大于或等于主结结深,则将会明显地改善pn结的击穿特性。

终端击穿电压与延伸区的掺杂剂量密切相关,当延伸区掺杂剂量为1.3×1012 cm-2时,击穿电压最高。虽然注入剂量可以精确控制,但延伸区的电荷量在后续工艺过程中会发生变化。同时,表面电荷会影响延伸区的电场强度分布,导致击穿电压不稳定。采用图7-4b所示的多区后,延伸区的电荷可以减少1/2,击穿电压可以达到理想平行平面结时的90%以上。采用JTE技术在提高终端击穿电压的同时,所需的结终端尺寸小于场限环结构。

4.横向变掺杂技术

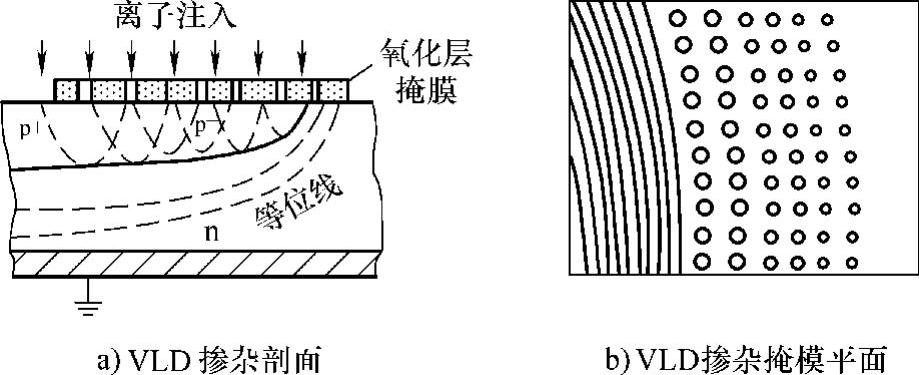

横向变掺杂(VLD)是R.Stengl等人于1986年提出的[7]。它在渐变掩模窗口的掩蔽下,利用离子注入兼推进,在硅表面形成可控的杂质分布。如图7-5a所示。图中点线所示为不同电压下的等位线,图中虚线所示为多个深度和宽度不同的小p区,这些小p区就组成了一个渐变的p型掺杂区。类似于JTE结构中的多个延伸区,与之不同的是,JTE主结外侧的p区掺杂几乎是均匀的,而VLD的p型区掺杂则是渐变的。

图7-5 横向变掺杂结终端结构剖面与掩模平面

如图7-5b所示[2],沿结终端区从内到外,掩模窗口的形状是不同的。在平均掺杂浓度较高处,所用的掩模窗口可以是环状;在平均掺杂浓度较低处,掩模窗口可以是一些小孔。这些条形窗口的密度及空隙、小孔的密度及孔径决定了掩模下面杂质的平均浓度。

VLD的耐压原理与JTE很相似。当pn结反偏时,要求VLD区全部耗尽,耗尽区就会沿着横向扩散区向外扩展,以提高终端击穿电压。但是,不论是JTE技术,还是VLD技术,都增加了pn结面积,导致反向漏电流增大。但与FLR相比,所占用结终端尺寸稍小。

采用VLD,理论上可得到最高的终端击穿电压,并使结终端所占的面积最小,但受制于光刻工艺及掺杂技术。随着离子注入技术在功率器件中的普遍使用,在高压IGBT和GCT等新型器件中,都已使用了VLD与JTE结构[8-10]。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。