1.结构的提出与发展

由上节的分析可知,IGBT中主要存在两对矛盾:一是饱和电压与开关损耗之间的矛盾;二是饱和电压与短路电流之间的矛盾。为了协调IGBT通态特性与关断特性及短路特性之间的矛盾,提高器件的综合性能和可靠性,在IGBT中引入了一种电子注入增强效应(Injection Enhancement Effect,IE),既可加强IGBT导通时的电导调制效应,又可限制阳极空穴的注入,于是形成了注入增强型IGBT(Injec-tion Enhanced Insulated Gate Bipolar Transistor,IE-IGBT)。

在IE-IGBT的发展过程中,出现了许多新结构与新技术,如1993年日本东芝(Toshiba)公司率先提出耐压为4.5kV宽栅IEGT结构[13,14],1996年日本三菱(Mitsubishi)公司提出了一种载流子存储沟槽栅双极晶体管(Carrier Storage Trench Gate Bipolar Transistor,CSTBT)结构[15];1998年东芝公司开发了具有虚拟元胞(Dummy Cell)或插入式元胞(Plugging-Cell Merged,PCM)的窄沟槽栅T-IEGT结构[16];同时日立(Hitachi)公司提出了一种高电导的平面栅IGBT结构(High-conductivity Planar Gate IGBT,HiGT)[17,18];2006年ABB公司提出了一种增强平面栅IGBT(Enhanced-Planar Gate IGBT,EP-IGBT)结构[19]等。尽管各公司对自己的产品命名不同,所采取的措施也不同,但目的都是提高通态时IGBT内部发射极侧的载流子浓度,即引入IE效应,以增强电导调制作用,从而解决IGBT通态特性和开关特性之间的矛盾,降低器件功耗。

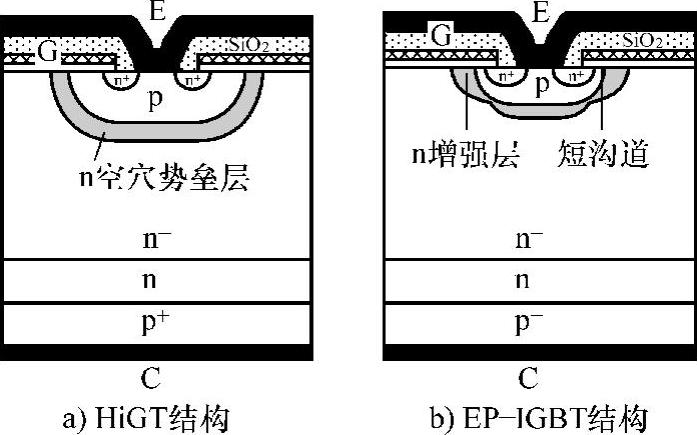

为了便于统一分析,本节将IEGT、CSTBT、HiGT及EP-IGBT通称为IE-IG-BT,把CSTBT结构中的载流子存储层(Carrier Storage,CS)层、HiGT结构中的空穴积累(Hole-Barrier,HB)层及EP-IGBT结构中的增强(Enhancement)层等统称为辅助层。

2.结构类型与特点

IE-IGBT结构有多种类型。按栅极结构来分,有平面宽栅和沟槽宽栅[20]及平面-沟槽栅(Trench-Planar Gate简称TP)结构[21];按是否有虚拟元胞来分,可分为普通元胞和虚拟元胞结构;按辅助层的位置来分,可分沟槽栅结构(如CST-BT)和平面栅结构(如EP-IGBT和HiGT)。

(1)宽栅IEGT结构 如图5-24a所示[22,23],由于P-IEGT的栅极较宽,n-漂移区靠近栅极侧的横向电阻较高,从集电极注入到n-漂移区的空穴,在横向通过p基区流入发射极时,会在栅极下方的n-漂移区中形成一层空穴积累。为了保持n-漂移区的电中性,n+发射区必须通过沟道向n-漂移区注入更多的电子,即产生电子注入增强效应。如图5-24b所示,T-IEGT沟槽栅极较宽,在导通期间,从p+集电区注入到n-漂移区的空穴也会在沟槽栅极下方形成积累,导致n+发射区的电子注入增强。由于这两种结构的栅极尺寸较大,使得元胞密度和沟道密度减小,从而会影响器件的电流容量。

图5-24 IEGT结构

(2)虚拟元胞窄槽栅IEGT结构 如图5-25a所示,由于部分元胞的p基区没有欧姆接触,成为p浮置区[24]。导通期间,集电区注入的空穴将无法经过p浮置区到达发射极,于是会在p浮置区下方的n-漂移区内形成积累;如图5-25b所示,由于部分元胞的多晶硅栅极与发射极短路[15],导通期间,栅极两侧的p基区则不会形成导电沟道,于是从集电区注入的空穴无法与电子复合,也会在栅极下方的n-漂移区内形成堆积。这两种结构均会产生电子注入增强效应。

图5-25 含虚拟元胞的窄槽栅IEGT结构

(3)n辅助层平面栅结构 如图5-26a所示,HiGT结构是通过离子注入工艺在n-漂移区和p基区之间形成一个n空穴势垒(HB)层[18],其掺杂浓度略高于n-漂移区的掺杂浓度。导通期间大量空穴会积累在空穴势垒层下方,迫使n+发射区注入增强。该结构不需要像P-IEGT那样增加栅极宽度,就可获得较强的IE效应,但对n HB的掺杂浓度要求极为严格,设计不当会严重影响器件的阻断能力。如图5-26b所示,EP-IGBT结构是在普通平面栅IGBT(P-IGBT)的p基区侧面和底部分别增加了一个n增强层[19]。与HiGT结构相比,EP-IGBT除了具有IE效应外,阻断电压较高;同时p基区侧面的n增强层会缩短沟道长度,有利于提高器件跨导和集电极电流,降低MOS沟道的压降。通过优化n增强层的参数,可增大其反偏安全工作区(RBSOA)。

(4)n辅助层沟槽栅结构 如图5-27a所示,CSTBT结构是在p基区与n-漂移区之间增加一个n载流子存储(CS)层[24],类似于HiGT结构中的n HB层。导通期间在n CS层下方会形成空穴积累层。如将n CS层和虚拟元胞相结合,可形成如图5-27b所示的CSTBT结构,导通期间的IE效应会更强,从而获得更低的导通损耗和开关损耗。

(https://www.xing528.com)

(https://www.xing528.com)

图5-26 平面栅结构

图5-27 沟槽栅结构

可见,IE-IGBT通过采用上述单项技术或者两项复合技术来增强发射极的电子注入,同时控制集电极的空穴注入[25],从而改善器件的通态特性和开关特性,达到降低损耗的目的。此外,沟槽栅IEGT还可以通过采用NPT[11]、FS及LPT型结构[26-27],进一步协调通态特性、阻断特性及开关特性之间的矛盾关系,降低损耗,并提高短路能力。

图5-28给出了IE-IGBT芯片几种不同的发射极图形。图5-28a所示为东芝公司4.5kV P-IEGT[22]芯片,尺寸为15mm×15mm,栅极压焊点均位于芯片角处。图5-28b所示为日立公司3.3kV/50A平面栅HiGT芯片[25],栅极压焊点位于芯片中央。图5-28c所示为三菱公司1.2kV/150A沟槽栅CSTBT芯片[28],栅极压焊点位于芯片的侧边和角上。

3.典型工艺

IE-IGBT的制作工艺流程与IGBT基本相同,其关键工艺在于深而窄的沟槽刻蚀、n辅助层的注入技术及少子寿命控制技术。

图5-28 各种不同IE-IGBT结构的芯片图形

(1)沟槽刻蚀工艺 在沟槽栅IEGT结构中,沟槽越深(深度约为12μm),IE效应越强。为了消除栅氧化层不均匀引起的阈值电压变化,并提高MOS沟道电子的迁移率,需采用精细的RIE刻蚀工艺先形成沟槽,再生长牺牲氧化层来获得光滑的槽壁[29]。对于宽槽栅(槽宽为8~12μm)结构,通常在氮氧化硅(SiON)掩蔽下进行沟槽刻蚀之后,再采用局部氧化(LOCOS)工艺来圆化沟槽底部拐角,并消除顶部的“鸟嘴”效应[30]。

(2)n辅助层工艺 由于n辅助层的掺杂浓度比n-漂移区的掺杂浓度稍高,常用离子注入工艺形成。但在不同的结构中,因n辅助层所处的位置不同,如HiGT结构中的n HB位于整个p基区外围,EP-IEGT结构中n EP层分别位于p基区的两侧和底部,CSTBT结构中的n CS层位于p基区正下方,所以形成n辅助层工艺条件有所不同。如图5-29a所示,若采用这种常规掺杂工艺,由于存在杂质的补偿作用,会使沟道的净掺杂浓度降低,导致阈值电压下降,并影响沟道电子的迁移率,同时也很难形成掺杂浓度和厚度均合适的n辅助层。采用倒掺杂(Retro Grade Doping)工艺,如图5-29b所示[31]可有效避免CS层对沟道掺杂浓度的补偿,有利于获得更高的沟道电子迁移率,并提高器件的均匀性,增大短路安全工作区(SCSOA)。

图5-29 载流子存储层的掺杂浓度分布

(3)载流子寿命控制技术 为了改善高压IEGT的开关特性,需要使用少子寿命控制技术。并且,寿命控制技术也会影响器件IE效应的强弱。与传统的均匀寿命控制相比,采用局部寿命控制[13,32],如质子辐照和H+、He2+等轻离子辐照,可将低寿命区控制在靠近n缓冲层的n-漂移区中,从而使器件的开关特性和通态特性同时得到改善。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。