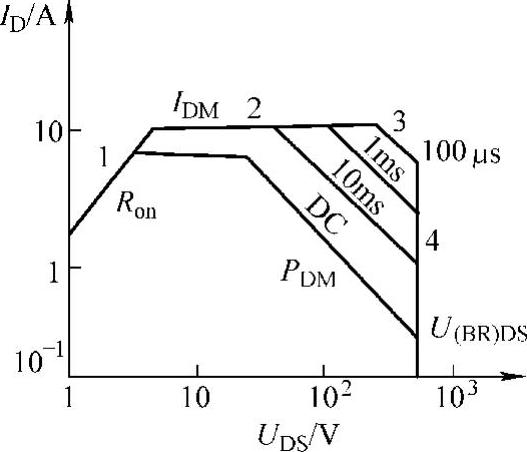

功率MOSFET必须工作在极限参数规定的区域,该区域称为安全工作区(SOA)。如图4-40所示,功率MOSFET的SOA由导通电阻Ron、最高漏极电流IDM、最大耗散功率PDM及最高漏源电压U(BR)DS决定。当UDS很小时,SOA由Ron和IDM决定;当UDS较大时,SOA由PDM决定;当UDS很大时,SOA由U(BR)DS决定。此外,SOA与脉冲持续时间有关,脉冲持续时间越长,温升对SOA影响越大,SOA越小。图中直流工作时的SOA最小。

图4-40 功率MOSFET的SOA

功率MOSFET在任何条件下工作时,其电流、电压及功耗都必须在SOA要求的范围之内。如果电流、电压及功耗超出其极限要求,则会损坏。为了增大功率MOSFET的SOA,除了降低导通电阻、提高击穿电压外,还需加强散热,以降低热阻。

2.雪崩耐量

(1)雪崩耐量的定义 功率MOSFET的雪崩耐量常用单脉冲雪崩耐量EAS和重复脉冲雪崩耐量EAR两个值来表示。单脉冲雪崩耐量EAS定义为单次雪崩状态下器件所能消耗的最大能量。重复脉冲雪崩耐量EAR定义为重复雪崩状态下器件所能消耗的最大能量。EAS越大,表示功率MOSFET承受电路电感引起过电压的能力越强。EAS与器件内部雪崩电流的分布及雪崩面积有关,还与器件的热性能和工作状态相关。雪崩电流导致器件温升,并且温升的大小与功率水平和封装热阻有关。

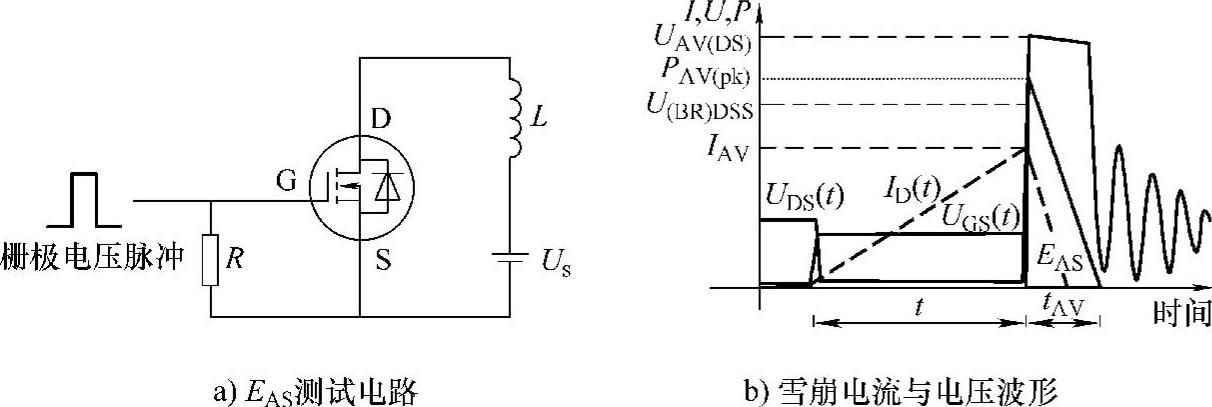

通常在非箝位的感性开关(UIS)条件下测量EAS,其测试电路如图4-41a所示[50]。当加上栅极脉冲时,功率MOSFET中的电流根据L和US的大小逐渐上升。当栅极脉冲结束时,功率MOSFET关断。由于电感中仍有电流流过,UDS会急剧上升,并达到器件的雪崩击穿电压UBR,直到电感中的电流消失。在此过程中,器件中消耗的能量(即雪崩耐量EAS)如图4-41b所示。

功率MOSFET关断之后,漏极电流不会瞬时改变,会随着击穿电压按一定的速率下降,可用下式来表示:

式中,UBR为功率MOSFET的雪崩击穿电压;US为电源电压;L为电感。

于是雪崩耐量EAS值可表示为

将式(4-68)代入式(4-69a),可得到

式中,UBR为功率MOSFET雪崩击穿电压;IAS为雪崩电流。可见,EAS除了与UBR、IAS有关外,还与电路的初始电感L成正比。(https://www.xing528.com)

图4-41 功率MOSFET的EAS测试电路及雪崩电流与电压波形

雪崩期间,器件中的雪崩能耗会引起瞬时温升ΔT。此时器件的最高结温Tjm可用下式以表示[50]:

Tjm=ΔT+Tj (4-70)

式中,ΔT为雪崩过程中器件的最大温升;Tj为器件关断前的结温。如果Tjm为175℃,则在Tj=25℃时,允许雪崩电流IAS产生的ΔT为150℃。在Tj=150℃,允许雪崩电流产生的ΔT只有25℃。

图4-42所示为功率MOSFET承受单脉冲雪崩时的SOA测试曲线。可见,当Tj=25℃时,功率MOSFET的SOA区较宽。当Tj=150℃时,由雪崩电流产生的功耗导致其SOA缩小。这说明功率MOSFET不存在由双极型晶体管过热引起的二次击穿现象,但并不排除由雪崩引起的二次击穿。

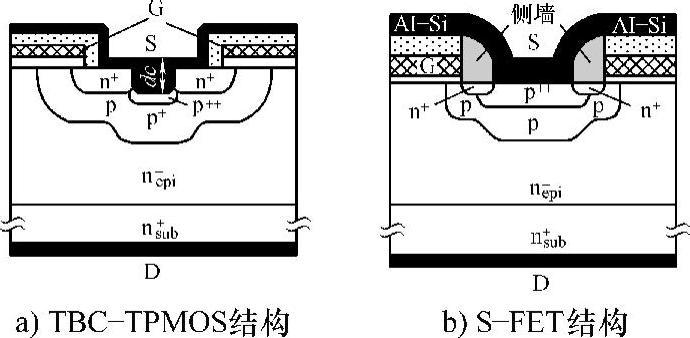

(2)提高雪崩耐量的措施 为了提高VDMOS的EAS,可以从结构上进行改进,通过增加p体区尺寸a来增加雪崩期间通流面积,还可采用沟槽平面栅(TP-MOS)结构,通过选择适当的沟槽宽度wt和深度dt来提高EAS。此外,采用沟槽体接触(Trench Body Contact,TBC)[51](见图4-43a),即在VDMOS的源区与p体区欧姆接触处通过刻蚀工艺形成一个浅沟槽,可降低源极接触电阻,有利于提高功率MOSFET的雪崩耐量。西门子(Siemens)公司的S-FET结构(见图4-43b)是采用氧化物侧墙和双离子注入的自对准超精细工艺来改善功率MOSFET的雪崩耐量及稳定性[52]。

图4-42 功率MOSFET承受单脉冲雪崩时的SOA测试曲线

图4-43 改善功率MOSFET雪崩耐量的结构

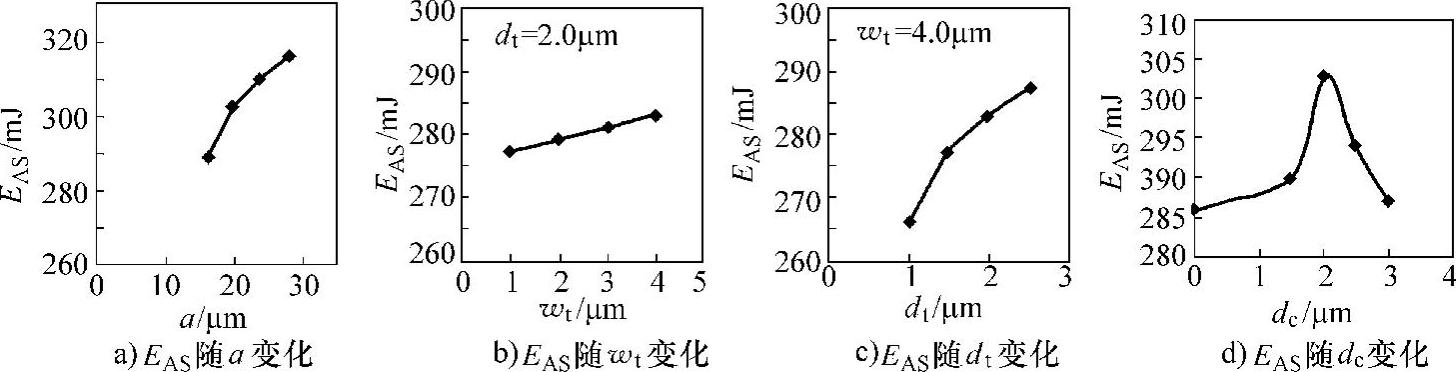

图4-44所示为TPMOS的雪崩耐量EAS随p体区尺寸a、沟槽平面栅区参数及沟槽接触区深度变化的模拟曲线。可见,当a在16~28μm范围内逐渐增大时,EAS也明显增大。当深度dt为2.0μm时,随宽度wt增大,TPMOS的EAS几乎线性增大。当wt为4.0μm,随dt增大,EAS也增大。可见,TPMOS的EAS与p体区尺寸有关,即p体区尺寸越大,雪崩面积越大,雪崩耐量越高。当接触区槽深dc为2.5μm时,雪崩耐量最高,如图4-44d所示。但接触区槽深dc不能过大,否则会在接触槽底处发生穿通击穿,导致雪崩耐量急剧下降。

图4-44 TPMOS雪崩耐量随结构参数的变化

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。