对SJMOS的广泛研究,不仅促进了SJMOS结构和工艺技术的改进,而且采用SJ的设计思想,还衍生出许多类似于SJMOS的新结构。这些新结构不仅可以降低SJ的工艺难度,而且不需要维持精确的电荷平衡,也可以改善导通电阻和击穿电压之间的矛盾关系。

1.半超结SJMOS结构

采用超结作为功率MOSFET的耐压层,必须保证n柱区和p柱区之间的电荷平衡,否则SJMOS的耐压、导通电阻及开关特性都要受到影响[31-34]。在实际的工艺实施中,p柱区和n柱区的电荷平衡很难做到精确控制。所以,SJMOS制造工艺的关键是SJ的制作。SJ制造工艺通常有两种方法:一是多次离子注入与外延工艺相结合;二是刻蚀与外延工艺相结合。

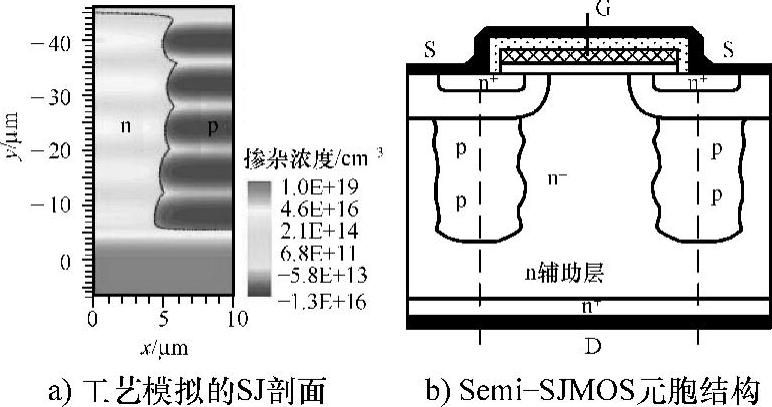

利用离子注入与外延工艺相结合制作SJMOS结构,如图4-26a所示。其工艺流程如下:首先在n+衬底上外延一定厚度的本征外延层,然后进行选择性的硼离子(B+)和磷离子(P+)注入;接着进行外延、再选择性注入B+、P+,如此反复,直到外延层厚度达到设计要求。之后,按VDMOS的工艺进行栅氧氧化和多晶硅栅淀积、p体区与n+源区的掺杂以及电极金属化。由于在外延高温过程中,注入的B+和P+分别向周围扩散,因此在多次外延和离子注入完成后,会形成如图4-26所示的柱区[35]。可见,柱区的纵向结面并非平面,这会使p柱区和n柱区电荷平衡受到影响。

图4-26 工艺模拟的SJ剖面结构与Semi-SJMOS元胞结构

由于SJMOS的击穿电压与SJ的柱区厚度呈线性关系。为了提高击穿电压,需制作较厚的超结柱区,这必然导致超结工艺成本增加、难度增大。若将超结变为半超结(Semi-SJ),形成如图4-26b所示的Semi-SJMOS结构,使耐压层由超结及其下方的n型辅助层两部分组成,于是在保证耐压的前提下,可以降低对柱区厚度的要求。故Semi-SJMOS是在器件性能和工艺难度之间的一种折中。

2.扩展深槽SJMOS结构

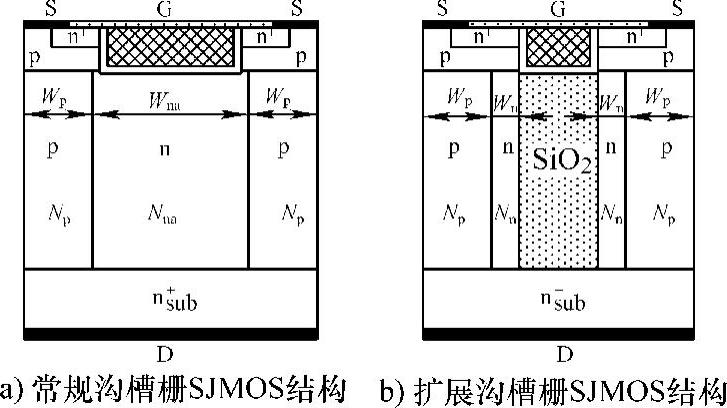

采用深槽刻蚀与填充工艺形成扩展沟槽栅SJMOS结构[36]如图4-27所示。与常规沟槽栅SJMOS结构相比,扩展沟槽栅SJMOS结构的p柱区与之完全相同,只是部分n柱区由氧化物填充的深槽替代,且深槽宽度与多晶硅栅宽度相等,n柱区位于沟槽两侧,其宽度远小于常规结构的n柱区宽度,即Wn<<Wna。

图4-27 扩展沟槽栅与常规的沟槽栅SJMOS结构比较

为了获得较高的击穿电压,也要求两柱区必须保持电荷平衡,即WnNn≈WnaNna≈WpNp。对常规沟槽栅SJMOS结构而言,在截止状态下,栅极和源极接地,在漏源之间加正向电压(UDS>0)。随UDS增加,多晶硅栅下的n柱区的表面会产生附加的正电荷,破坏n柱区和p柱区之间的电荷平衡,导致器件的击穿电压下降。在扩展沟槽栅SJMOS结构中,多晶硅栅下的n柱区被氧化物填充的深槽代替,不存在上述现象。因此,扩展沟槽栅SJMOS击穿特性能够得以改善。(https://www.xing528.com)

扩展沟槽栅SJMOS关键是n柱区的实现。为了精确控制n柱区的杂质剂量,可以利用小角度注入(Shallow Angle Implantation)来实现[37]。采用以下的工艺流程:首先在硅衬底上生长一层p外延层及p+外延层;然后在p+外延层上依次进行硼离子(B+)、磷离子(P+)注入并推进,分别形成p体区和n+源区;接着在外延层上利用反应离子刻蚀(RIE)沟槽至n+衬底,于是将外延层分成对称分布的两个p柱区;控制入射角和注入剂量,在沟槽侧壁以小角度注入磷离子(P+),以形成对称分布的两个n柱区,同时对p+外延层进行杂质补偿,完成对阈值电压的调整;之后,利用热氧化在沟槽侧壁形成栅氧化层,然后通过化学气相淀积(CVD)先在扩展沟槽区中填充氧化物,再在上部的沟槽区填充多晶硅而形成栅极;最后进行衬底减薄及电极制备等后道工艺。

由此可知,扩展沟槽栅SJMOS结构的p柱区为原始外延层,n柱区通过一次小角度离子注入即可形成,并且可以对注入剂量进行精确控制和灵活调整。与传统的离子注入和外延工艺相结合比较,可显著降低超结制作的工艺难度。

3.氧化层旁路MOSFET结构

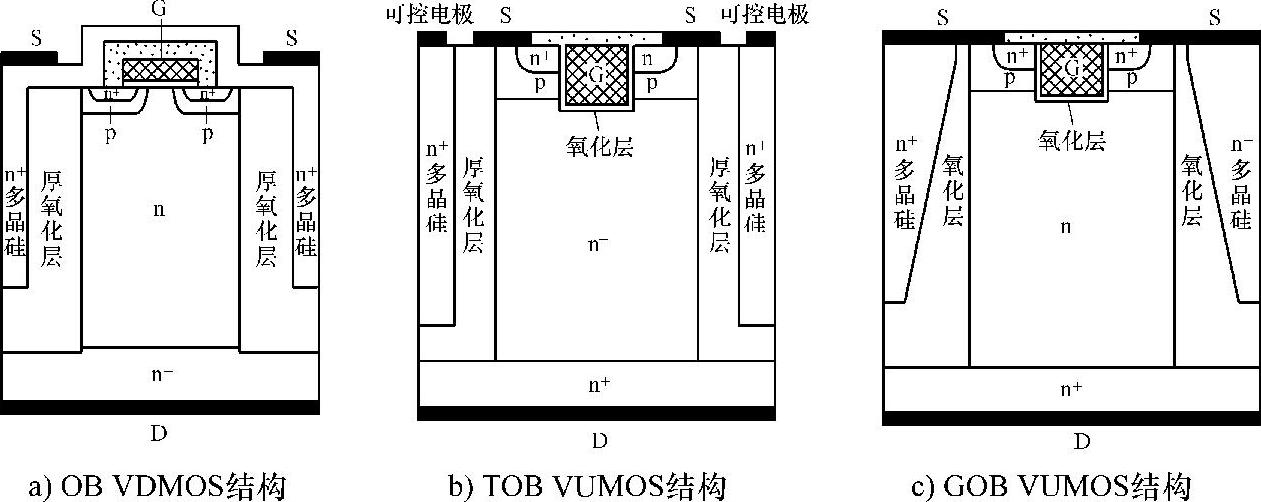

如图4-28a所示,氧化层旁路的VDMOS(Oxide-Bypassed VDMOS,OBVD-MOS)结构[38,39]是在VDMOS的n-漂移区通过刻蚀形成沟槽后,依次填充氧化层和重掺杂的多晶硅,并使之与源极金属电极相连而形成金属-厚氧化层(Metal-Thick-Oxide,MTO)电极。利用MTO上电场来加速漂移区横向耗尽,相对于SJ精确的电荷平衡控制而言,氧化层厚度的控制更容易实现。还可以对氧化层旁路(OB)结构进行改进,将源极与多晶硅的控制极分离,形成可调的氧化层旁路(Tunable Oxide-Bypassed,TOB)VUMOS结构,如图4-28b所示[40]。通过在其多晶硅表面的可控电极上施加偏压,可以补偿工艺变化对击穿电压的影响。从而摆脱了SJ固有的电荷精确控制的限制,使其击穿电压与特征导通电阻突破硅极限。为了使OB漂移区中的电场能够达到SJ器件那样的最佳电场,也可将OB漂移区改成渐变氧化层旁路(Gradient Oxide-Bypassed,GOB)VUMOS结构如图4-28c所示[41]。采用GOB结构,可使器件在中等电压范围内的性能达到理想SJ器件性能,同时有简单的制作工艺。其缺点是形成这种渐变的氧化层侧墙结构需要特殊的刻蚀剂。

基于上述的OBVDMOS和GOBVUMOS结构,还有一种具有阶梯槽形氧化层旁路的VDMOS结构[42]。它是可通过阶梯槽形氧化层来调制VDMOS高阻漂移区的电场强度分布,并增强了电荷补偿效应。这种结构使VDMOS在低于300V击穿电压下具有超低的导通电阻。与普通氧化旁路的OBVDMOS结构相比,阶梯槽形氧化层旁路MOSFET的击穿电压可提高20%以上,特征导通电阻降低40%~60%。

图4-28 氧化层旁路的MOSFET结构

4.浮岛MOSFET结构

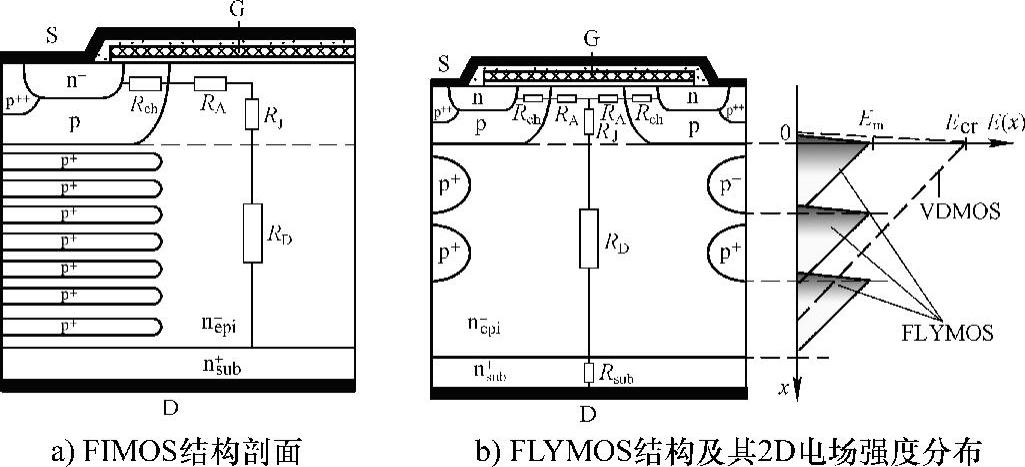

浮岛MOSFET结构如图4-29所示,它是在VDMOS结构的n-漂移区中引入p型浮岛(Floating Island,FI)[43],可以代替200V的SJMOS。通常有两种不同形状的浮岛,如图4-29a所示。FIMOS结构是在VDMOS的n-漂移区中通过外延与离子注入引入多个平行的p+埋层(称为浮岛),形成纵向交替出现的pn结[44]。如图4-29b所示,FLYMOSTM结构是通过离子注入在n-漂移区中引入两级p+埋层[45,46]。这两种浮岛结构均是利用电荷补偿原理,通过在n-漂移区中引入p浮岛,以改善导通电阻与击穿电压之间的矛盾关系。从图4-29b中可见,FLYMOS的峰值电场与VDMOS相比明显下降,特征导通电阻也降低约70%。

图4-29 FIMOS结构剖面与FLYMOS结构及其2D电场强度分布

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。