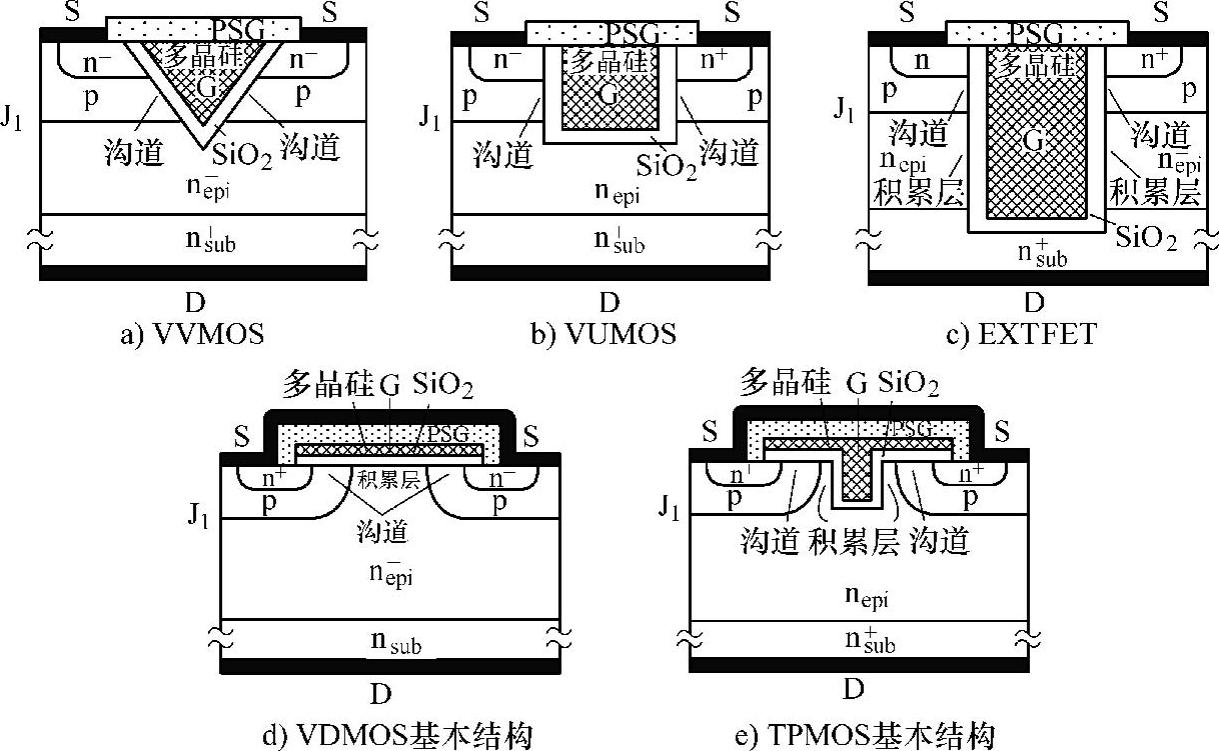

1.沟槽栅MOSFET结构

(1)VVMOS结构 如图4-2a所示,纵向V形槽MOSFET(Vertical V-groove MOSFET,简称VVMOS)结构是最早的沟槽栅MOSFET[2]。栅极是一个V形沟槽,栅、源极在表面,漏极在底部。当栅极加上正电压时,在p体区内沿V形沟槽侧壁的斜面形成n型导电沟道。因沟道在体内,占用芯片的表面积小,使芯片面积利用率提高,并且每个V形槽对应两个沟道,通过增加元胞数量,可提高电流容量。但是,由于V形槽底部存在电场尖峰和电流集中效应,使其击穿电压难以提高。所以,后来的沟槽结构主要针对沟槽形状进行改进。

图4-2 功率MOSFET元胞结构类型

(2)VUMOS结构 如图4-2b所示,将VVMOS的V形沟槽改成了U形沟槽,形成了纵向U形槽MOSFET(Vertical U-groove MOSFET,简称VUMOS)结构,解决了VVMOS槽底尖端放电问题,可提高击穿电压。当栅极加上正电压时,在p体区内沿沟槽侧壁形成导电沟道。由于沟道垂直,元胞可做得更小,于是在相同面积芯片上可制作出更多的元胞,有利于提高电流容量。但当击穿电压较高时,n-漂移区较厚,导致其导通电阻较大。制作VUMOS芯片时,通常采用如下的工艺流程:衬底外延片→p体区和n+源区依次掺杂→沟槽刻蚀→热生长栅氧化层→化学气相淀积多晶硅,以填充沟槽栅区→表面平坦化→光刻→淀积磷硅玻璃→光刻接触孔→正面电极制备→衬底减薄→背面三层金属化。

(3)EXTFET结构 如图4-2c所示,为了进一步降低VUMOS的导通电阻,可将VUMOS的U形沟槽向下刻蚀,穿透n-漂移区直至n+衬底,形成扩展沟槽栅MOSFET(Extended Trench MOSFET,简称为EXTFET)结构[3]。当栅极加上正电压时,在p体区内沿沟槽侧壁形成导电沟道,同时在n-漂移区内沿沟槽侧壁形成电子积累层,于是可获得超低的导通电阻。U形深槽可采用反应离子刻蚀(RIE)工艺形成,然后通过热氧化消除刻蚀损伤,再利用化学气相淀积(CVD)填充多晶硅槽形成栅极。沟槽的深宽比与工艺成本密切相关。深宽比较大时,沟道密度增大,但工艺难度和成本也随之增加,且U形深槽会导致击穿电压下降,工艺成本增加。所以,EXTFET结构只适合低电压、低功耗的应用场合。

2.纵向双扩散MOSFET结构(https://www.xing528.com)

如图4-2d所示,纵向双扩散MOSFET(Vertical Double Diffusion MOSFET,简称VDMOS)是采用双扩散工艺形成的一种平面栅结构。在外加正栅压时,在p体区表面形成导电沟道,同时在栅极下方的n-漂移区表面会形成电子积累层。与LDMOS相似,VDMOS的沟道长度也是由两次扩散结深决定的,不受光刻精度限制。但因其沟道平行于表面,使得元胞尺寸较大,元胞数目减少;并且,由于电流通路中存在结型场效应晶体管(Junction Field Effect Transistor,JFET)区(瓶颈处),其电阻RJ较大。特别是当击穿电压较高时,n-漂移区较厚,导致其导通电阻Ron很大。通常VDMOS的导通电阻Ron与击穿电压UBR之间的关系为Ron∝U2.4~2.5[1]BR。相比较而言,由于VUMOS中不存在JFET区(即RJ为零),故VU-MOS的导通电阻要比VDMOS小。

VDMOS芯片最初采用铝栅工艺制作,目前主要采用硅栅和自对准工艺制作。其典型的工艺流程如下[4]:衬底外延片→热生长栅氧化层→化学气相淀积多晶硅栅极→光刻→硼离子(B+)注入后高温推进形成p体区→光刻→磷离子(P+)注入后经高温推进形成n+源区→淀积磷硅玻璃→光刻接触孔→正面电极制备→衬底减薄→背面三层金属化。其中用硅栅来定义有源区的边界,在多晶硅栅的掩蔽下进行有源区的p体区和n+源区掺杂,不仅可形成较短的沟道,而且可有效地减小栅源交叠电容,改善频率特性。由于VDMOS的工艺简单、成本低,是目前功率MOSFET的主流结构。

3.沟槽-平面栅MOSFET结构

由于VDMOS结构中存在JFET区,使其击穿电压和导通电阻之间存在不可调和的矛盾。为了解决此问题,基于VDMOS结构,作者提出了一种沟槽-平面栅MOS-FET(Trench-Planar MOSFET,简称TPMOS)结构[5],如图4-2e所示。它是在VD-MOS多晶硅栅下两个p体区之间的n-漂移区中设置了一个浅沟槽,内部依次进行热氧化和多晶硅填充,并与平面栅极连为一体形成沟槽-平面栅极。该结构有三个优点:一是消除了VDMOS的JFET区,可显著减小器件的导通电阻;二是浅沟槽可将p体区结弯曲处的高电场转移到沟槽拐角处,在一定程度上缓解p体区结弯曲处的电场集中,改善器件的击穿特性,并有效地避免了栅极宽度对器件击穿电压的影响。三是导电沟道仍然在芯片表面,便于阈值电压调整,制作工艺也与VDMOS相兼容。

制作TPMOS的关键之处在于沟槽的定位与深度,通常要求沟槽侧壁位于p体区之外的n-漂移区,深度小于p体区结深[6,7]。如果沟槽较宽,使得沟槽拐角处于p体区的耗尽层内,这虽然可以提高击穿电压,但会增加寄生的栅漏电容,导致其开关特性和频率特性变差[8]。制作TPMOS时,只需要在元胞形成之前,先利用反应离子刻蚀(RIE)在n-外延层上形成U形浅沟槽,热氧化去除沟槽表面的损伤层后进行栅氧化层热生长;接着淀积多晶硅以填充沟槽,并进行表面平坦化处理。此后的工艺与VDMOS的完全相同。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。