【摘要】:表7-142 小模数蜗杆、蜗轮的误差项目、定义与代号(续)(续)图7-2例7-1图解 图7 - 2所示的电路是由3个JK触发器作为存储电路,同两个与非门、一个与门构成。各级触发器受同一时钟CP控制。表7-1例7-1电路的状态转移真值表(续)偏离状态能够在计数脉冲的作用下,自动转入有效序列的特性,称为自启动特性。表7-143 小模数圆柱蜗杆传动公差组图7-3例7-1电路的状态转移图画出该电路的波形图(时序图),如图7 - 4所示。

1. 目的

时序逻辑电路分析就是对给定的时序逻辑电路,找出其输入与输出的逻辑关系,或者描述其逻辑功能、评价其电路是否为最佳设计方案。

2. 方法

可用状态转移方程、电路输出函数表达式、状态转移真值表、状态转移图、工作波形图等分析时序逻辑电路。

3. 一般步骤

(1) 根据给定的时序逻辑电路,写出存储电路(如触发器)的激励(驱动)方程,即存储电路的输入信号的逻辑函数表达式。

(2) 写出存储电路的状态转移方程,并根据输出电路,写出输出函数表达式。若存储电路由触发器构成,可根据触发器的状态方程和驱动方程写出各个触发器的状态转移方程。

(3) 由状态转移方程和输出函数表达式,列出状态转移真值表,画出状态转移图。

(4) 画出波形图(时序图)。

例7 - 1 分析图7 - 2所示同步时序逻辑电路。

图7-2 例7-1图

解 图7 - 2所示的电路是由3个JK触发器作为存储电路,同两个与非门、一个与门构成。各级触发器受同一时钟CP控制。

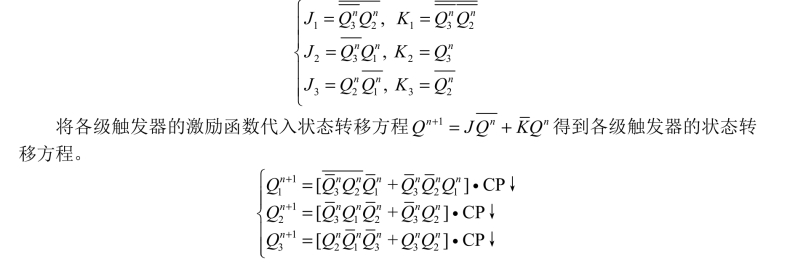

写出各级触发器的驱动方程(激励函数):(https://www.xing528.com)

输出方程为:

![]()

由状态转移方程、输出函数列出状态转移真值表,画出状态转移图。由于电路没有外加输入信号,因此存储电路的次态和输出只取决于电路的初态。

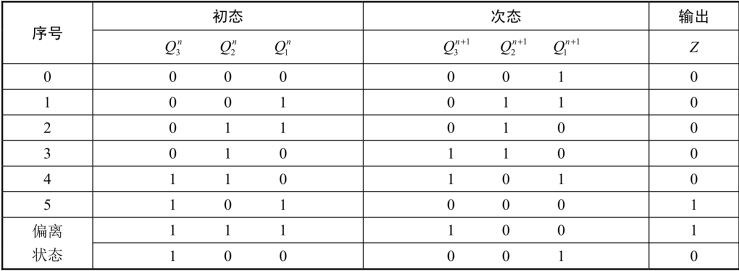

设各级触发器的初态为 =000,其状态转移真值表见表7 - 1。

=000,其状态转移真值表见表7 - 1。

表7-1 例7-1电路的状态转移真值表

偏离状态能够在计数脉冲的作用下,自动转入有效序列的特性,称为自启动特性。

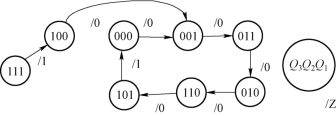

该电路的状态转移图如图7 - 3所示。

图7-3 例7-1电路的状态转移图

画出该电路的波形图(时序图),如图7 - 4所示。

图7-4 例7-1电路的波形图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。