1.CPLD

复杂可编程逻辑器件CPLD(Complex Programmable Logic Device)是从GAL的逻辑结构发展起来的,依然是由与阵列、或阵列、输入缓冲器和输出逻辑宏等单元组成。CPLD的与阵列比GAL大得多,但不是数量上的简单扩充,而是将整个逻辑划分为多个逻辑阵列块,每个逻辑阵列块比一个GAL的规模还大,各个逻辑阵列块之间通过片内总线实现逻辑互连。下面以Altera公司的MAX7000S系列器件为例,介绍CPLD的结构和工作原理。

MAX7000S系列器件的结构包含五个主要部分:逻辑阵列块、宏单元、扩展乘积项(共享和并联)、可编程连线阵列和I/O控制块。

1)逻辑阵列块(LAB)

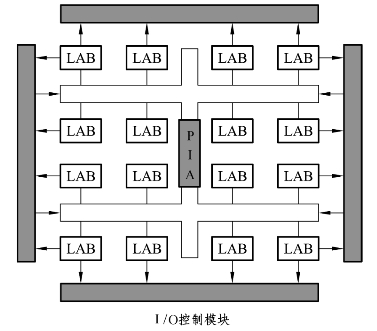

如图7.3.13所示是MAX7128S的基本结构,16个LAB通过可编程连线阵PIA(Programmable Interconnect Array)和全局总线实现逻辑互联。全局总线从所有的专用输入、I/O引脚和宏单元馈入信号。对于每个LAB的输入信号来自三方面:① 来自作为通用逻辑输入的PIA的36个信号;② 全局控制信号,用于寄存器辅助功能;③ 从I/O引脚到寄存器的直接输入通道。

2)宏单元

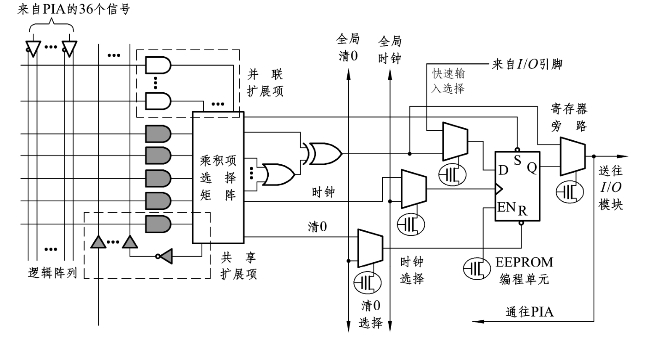

MAX7000的一个LAB由16个宏单元的阵列组成,如图7.3.14所示,宏单元由三个功能块组成:逻辑阵列、乘积项选择矩阵和可编程触发器,它们可单独地配置为时序逻辑和组合逻辑工作方式。其中逻辑阵列实现组合逻辑,可以给宏单元提供5个乘积项。乘积项选择矩阵分配这些乘积项作为到与门和异或门的主要逻辑输入,以实现组合逻辑函数;或者将这些乘积项作为清零(Reset)、置位(Set)、时钟(CP)信号送可编程触发器。可以单独将其设置为D,T,JK或SR触发器,也可将其旁路掉,实现组合逻辑工作方式。

图7.3.13 MAX7128S的结构

图7.3.14 MAX7000系列的宏单元结构

3)扩展乘积项

宏单元中的5个乘积项能够实现大多数逻辑函数,但更为复杂的逻辑函数需要附加乘积项。这种情况下,可以利用共享扩展乘积项和并联扩展乘积项(简称扩展项),这两种扩展项作为附加的乘积项直接送到本LAB的任意一个宏单元中。

(1)共享扩展项:共享扩展项由每个宏单元提供一个单独的乘积项,通过非门取反后反馈到逻辑阵列中,可被LAB内任何一个或全部宏单元使用,以实现复杂的逻辑函数。

(2)并联扩展项:并联扩展项是宏单元中一些没有被使用的乘积项,可以分配到邻近宏单元去实现复杂的逻辑函数。最多可以使用20个乘积项直接送往宏单元的或阵列,其中5个乘积项由本宏单元提供,另外15个并联扩展项是从同一LAB中的其他15个宏单元借来的。

4)可编程连线阵列PIA

所有的LAB通过在PIA上布线,以相互连接构成所需的逻辑。如图7.3.15所示,PIA是一种可编程通道,MAX7000S器件的专用输入、I/O引脚和宏单元输出都连接到PIA,而PIA可将这些信号送到整个器件的各个地方。

5)I/O控制块

如图7.3.16所示,I/O控制块允许每个I/O引脚单独被配置为输入、输出或双向工作方式。所有的I/O引脚一个三态缓冲器,它的控制信号来自一个多选一电路,可以选择电源、地或6个全局输出使能信号之一。6个全局输出使能信号来自两个输出使能信号(OE1,OE2)、I/O引脚或宏单元。

图7.3.15 PIA信号布线到LAB的方式

图7.3.16 MAX7218S的I/O模块

2.FPGA

现场可编程门阵列FPGA(Field Programmable Gate Array)是基于查找表LUT(Look Up Table)逻辑结构的大规模可编程逻辑器件,LUT是可编程的最小逻辑构成单元。下面以Altera公司的FLEX10K系列器件为例,介绍FPGA的结构和工作原理。(https://www.xing528.com)

FLEX10K主要由嵌入式阵列块、逻辑阵列块、快速通道和I/O单元四部分组成,其中,逻辑阵列块由多个逻辑单元构成。如图7.3.17所示是FLEX10K的内部结构图。

图7.3.17 FLEX10K的内部结构

1)查找表的逻辑原理

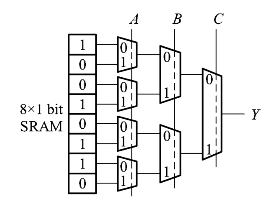

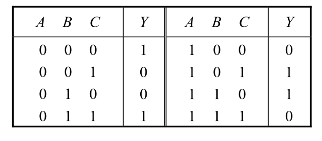

如图7.3.18所示是一个三变量输入的查找表,它由23×1 bit的SRAM和多个二选一电路组成的。从表7.3.1可以看出逻辑函数Y 的取值就是存储在SRAM中的值,Y=m0+m3+ m5+m6,即查找表中的SRAM存储的是逻辑函数标准式1。一个N输入的查找表需要2n×1 bit的SRAM,N不可能太大,否则LUT的利用率低,FLEX10K的LUT是一个四输入的查找表。对于输入多于4个的逻辑函数要用几个LUT结合起来实现。

图7.3.18 查找表的结构

表7.3.1 图7.3.17的真值表

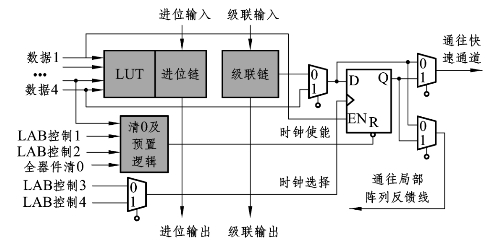

2)逻辑单元(LE)

如图7.3.19所示,LE是FLEX10K结构中的最小单元,它包括一个4输入的LUT、一个可编程触发器、一个进位链和一个级联链。进位链提供LE之间并行进位功能,级联链可以实现多扇入数的逻辑函数。可编程触发器可以单独设置为D,T,JK或SR触发器,也可将其旁路掉,实现组合逻辑工作方式。该触发器的时钟、清零和置位信号可由全局信号通用I/O引脚或任何内部逻辑驱动。

每个LE有两个输出分别可以驱动局部互连和快速通道(Fast Track)互连。这两个输出可以单独控制,即在一个LE中LUT驱动一个输出,触发器驱动另一个输出。这样可以在一个LE中完成两个不相干的功能,提高LE的资源利用率。

图7.3.19 LE的结构

FLEX10K的LE共有4种工作模式:正常模式、运算模式、加减计数器模式和可清零计数器模式。每种模式LE的7个可用输入信号被连接到不同的位置,以实现所要求的逻辑功能。这7个输入信号是来自LAB局部互连的4个数据输入,来自可编程触发器的反馈信号以及前一个LE的进位输入和级联输入。LE的另外三个输入为触发器提供清零、置位和时钟信号,触发器还有一个时钟使能信号由数据1提供,利于实现全同步设计。

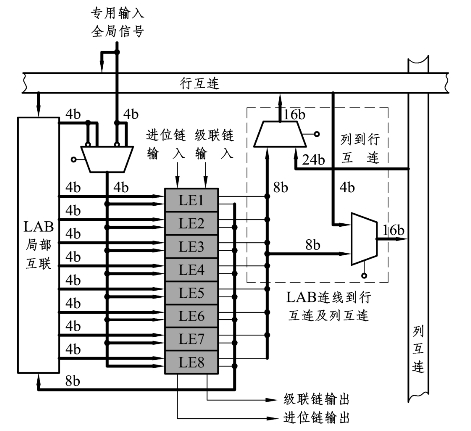

3)逻辑阵列LAB(Logic Array Block)

如图7.3.20所示是逻辑阵列LAB结构,每个LAB由8个LE、与LE相连的进位链和级联链、LAB控制信号与LAB局部互连线组成。

图7.3.20 LAB的结构

4)快速通道(Fast Track)

LE和I/O引脚之间的连接是通过快速通道连接的,快速通道遍布于整个器件,是一系列水平走向(行互连)和垂直走向(列互连)的连续式布线通道。

5)I/O单元与专用输入端口

I/O引脚是由一些I/O单元(IOE)驱动的,IOE位于快速通道的行和列的末端。IOE包含一个双向I/O缓冲器和一个可编程触发器。FLX10K还提供了6个专用输入引脚,这些引脚使用专用布线通道直接送达IOE触发器的控制端。

6)嵌入式阵列块EAB(Embedded Array Block)

嵌入式阵列块EAB是在输入、输出口上带有寄存器的RAM块。每个EAB提供的RAM为2 048 bit,根据需要可方便地将其配置为256×8 bit,521×4 bit,1 024×2 bit或2 048×1 bit。当EAB用来实现计数器、地址译码器、状态机、乘法器、微控制器以及DSP等复杂逻辑时,每个EAB可以贡献100~600的等效门。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。