许多时序逻辑电路都有这样一个特点:电路循环输出N个(可重复)状态,每个状态可由M位二进制数表示。本书将具有这一特点的时序逻辑电路称为循环时序电路。例如计数器、步进电机控制器、交通灯控制器、节日彩灯控制器等都属于循环时序电路。下面针对循环时序电路的设计介绍几种方法。

设计4路彩灯控制器

1.计数→译码→编码法

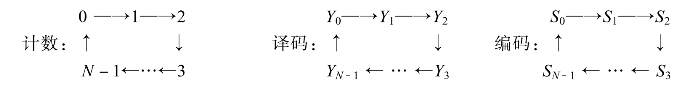

设电路循环输出N 个状态:S0,S1,S2,…,SN-1,每个状态用二进制数表示。若第i个时钟需产生状态Si(Si的代码为二进制数j)输出,只要将计数-译码器的第i个时钟的有效输出端Yi送编码器的第j输入端Ij,则第i个时钟到来时编码器必然输出二进制数j。此方法就是利用计数→译码→编码实现输入与输出之间的状态映射,即

【例 4.4.3】 某单位门前有“新年好”三路彩灯,要求动态显示“新”→“年”→“好”→熄灭→“新年好”→熄灭→“新”→“年”→……。请设计这样的控制电路。

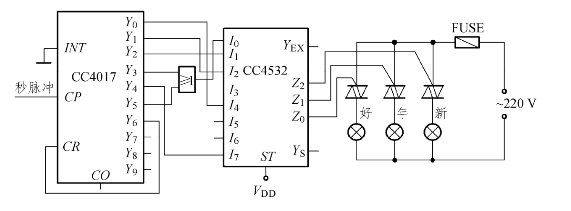

解:用3位二进制数控制3路彩灯的亮和灭,1使彩灯亮,0使彩灯灭。电路循环输出6个状态:100→010→001→000→111→000→100→010→…。电路由CC4017实现计数→译码,采用暂态复位法将CC4017设置成六进制计数-译码器,然后CC4532完成编码输出,如图4.4.7所示。CC4532是8~3优先编码器,其引出端有:信号输入端I7~I0(高电平有效),代码输出端Z2Z1Z0(二进制数的原码),片选输入端ST(高电平有效),选通输出端YS(当ST=1且无有效信号输入时YS为高电平,否则为低电平),扩展输出端YEX(当ST=1且有有效信号输入时YEX为高电平,否则为低电平)。

图4.4.7 例4.4.3的电路图(https://www.xing528.com)

【例4.4.4】 试用基于芯片级的方法设计三相六拍制的步进电机控制器。

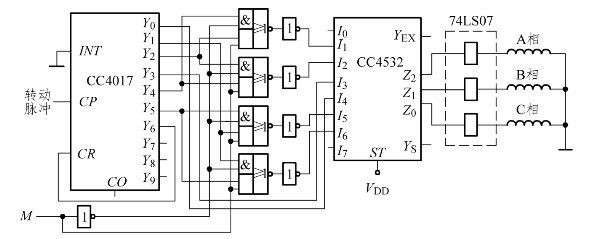

解:选取M为正反转控制信号,当M=0时步进电机正向转动,当M=1时步进电机反向转动。其电路如图4.4.8所示。

图4.4.8 例4.4.4的电路图

2.计数-访存输出法

将循环时序电路要输出的N个状态的二进制代码,从第0地址依次写入ROM芯片,用N进制加1计数器的输出作为ROM芯片的地址,当计数器循环计数时,ROM芯片按照计数频率依次输出N个状态代码。该方法的设计举例请见本书第7章例7.2.1。

3.计数-代码映射法

对于具有N个输出状态的循环时序电路,用N进制计数器为其计数,将计数器输出的二进制数直接映射为输出状态的代码。设计数器的输出为四位二进制数,那么电路要实现:0000映射为S0的代码,0001映射为S1的代码,0010映射为S2的代码……。这种方法不便于使用MSI芯片实现,但是用VHDL语言编程却是很容易的,然后用可编程逻辑器件实现。该方法的设计举例请参见第8章例8.3.10。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。