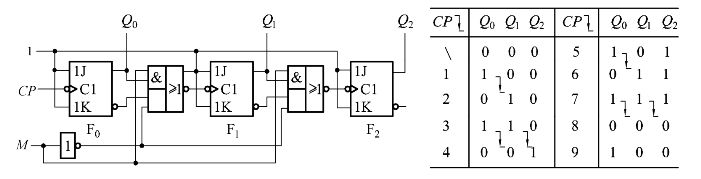

【摘要】:根据上述分析,异步加1计数器可以这样来实现:用下降沿触发的T触发器存储各位的状态,且T触发器的T端保持为1,用第i-1位触发器的输出Qi-1作为第i位触发器的时钟。图4.3.2八进制异步可逆计数器的电路图和状态表

1.异步加1计数器

设由n个T触发器构成的n位计数器的状态为Qn-1…QiQi-1…Q1Q0,考虑Qi-1对Qi的影响:若初态Qi-1=0,次态Qi-1=0,则Qi保持;若初态Qi-1=0,次态Qi-1=1,则Qi保持;若初态Qi-1=1,次态Qi-1=1,则Qi保持;若初态Qi-1=1,次态Qi-1=0,则Qi翻转,即Qi-1的下降沿导致Qi翻转。

根据上述分析,异步加1计数器可以这样来实现:用下降沿触发的T触发器存储各位的状态,且T触发器的T端保持为1,用第i-1位触发器的输出Qi-1作为第i位触发器的时钟。

2.异步减1计数器

设由n 个T触发器构成的n位计数器的状态为Qn-1…QiQi-1…Q1Q0,考虑Qi-1对Qi的影响:若初态Qi-1=1,次态Qi-1=1,则Qi保持;若初态Qi-1=1,次态Qi-1=0,则Qi保持;若初态Qi-1=0,次态Qi-1=0,则Qi保持;若初态Qi-1=0,次态Qi-1=1,则Qi翻转,即Qi-1的上升降沿导致Qi翻转。(https://www.xing528.com)

根据上述分析,异步减1计数器可以这样来实现:仍用下降沿触发的T触发器存储各位的状态,且T触发器的T端保持为1,用第i-1位触发器的输出 作为第i位触发器的 时钟。

作为第i位触发器的 时钟。

3.异步可逆计数器

将上述第1种情况和第2种情况结合,得到八进制异步可逆计数器的电路(见图4.3.2)和加1计数的状态表。电路中的M=0进行加1计数,M=1进行减1计数。注意表中一个状态行的各位状态不一定是同时产生的。

图4.3.2 八进制异步可逆计数器的电路图和状态表

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。