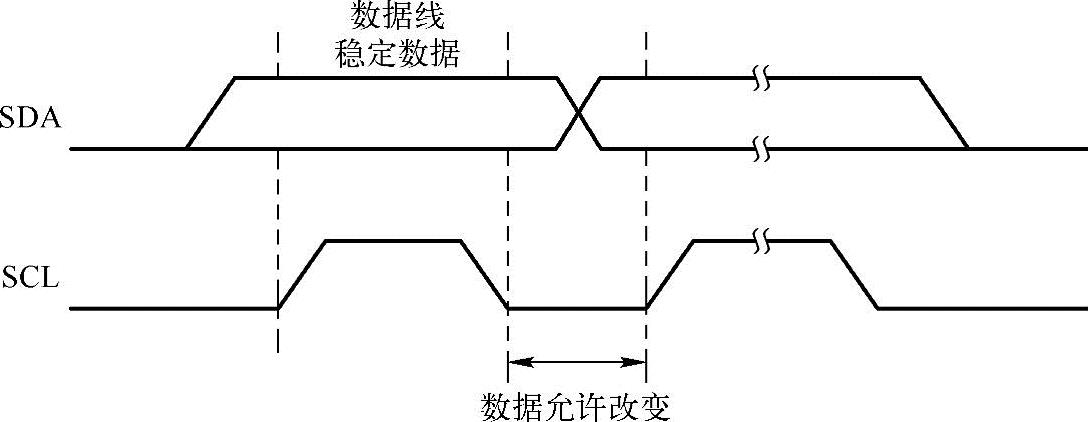

1.数据状态

图7-41描述了I2C总线传送数据时数据线SDA和时钟线SCL的电平状态。在时钟为高电平时SDA引脚上的数据必须稳定。只有在SCL上时钟信号变低时,数据线SDA上高或低状态才能改变。

图7-41 I2C总线的数据传输状态

2.输入和输出电平

主设备为每个数据传输产生一个时钟脉冲。由于连接到I2C总线的设备采用的技术标准不同,因此逻辑0(低电平)和逻辑1(高电平)是不固定的,与设备的VDD值有关。具体要看对应的28xDSP数据手册。

3.操作模式

I2C模块有四种基本操作模式用以支持数据传送,各模式的操作模式见表7-48。具体介绍如下:

1)如果I2C模块工作在主模式下,当向从模块发送数据时,I2C模块必须保持主发送器模式;接收从模块的数据时,则其必须变为主接收器模式。

2)如果I2C模块是从机,通常是当其识别来自主机的从地址时发送一个应答信号。如果主机将要发送数据给I2C模块,那么模块必须保持从接收器模式。如果主机要求I2C模块发送数据,那么模块必须变为从发送器模式。

表7-48 I2C模块的操作模式

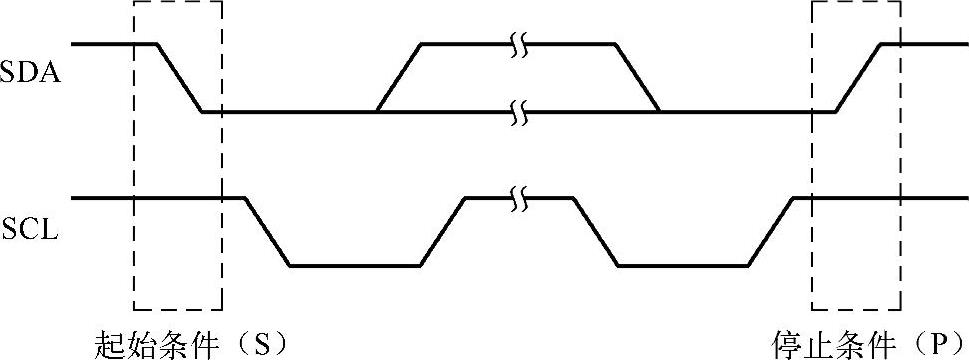

4.I2C模块的起始和停止条件

当I2C总线上的I2C模块被配置成主机时,可以由该模块产生起始(START)和停止(STOP)条件。如图7-42所示。当SCL为高电平,SDA数据线产生由高到低跳变时,表示起始条件产生。主机通过产生这样的条件来表明数据传送开始;当SCL为高电平,SDA数据线产生由低到高跳变时,表示停止条件产生。主机通过产生该条件表明数据传送停止结束。

图7-42 I2C模块的起始和停止条件

起始条件开始后且停止条件产生前,认为此时的I2C总线是处于忙状态的,此时I2CSTR的总线忙位BB=1;在停止条件产生后与下个起始条件产生前,这段期间认为I2C总线是处于空闲的,此时BB=0。

为使I2C模块使用起始条件开始数据的传送,I2CMDR的主机模式位(MST)和起始条件位(STT)都必须为1。为使I2C模块使用停止条件终止数据的传送,则停止条件位(STP)必须置1。当RM位和STT位都置1时,产生重复的起始条件。

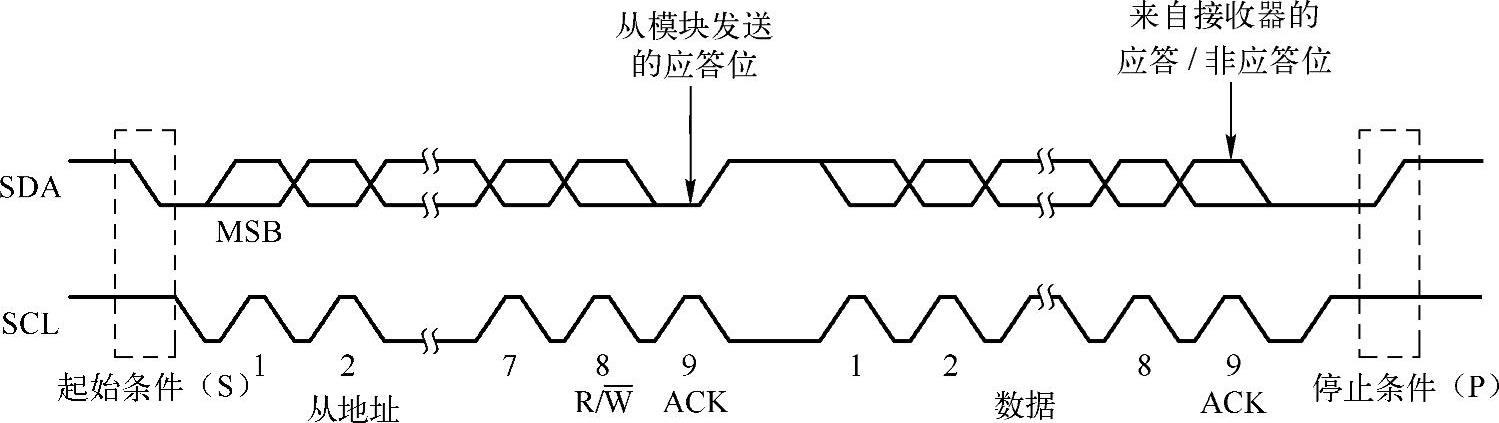

5.串行数据格式

图7-43为I2C总线传送数据的例子。I2C模块支持传输1~8位的数据值。图7-43中传送的数据是8位。SDA数据线上每一位的维持时间相当于SCL的一个脉冲。传送数据时,总是高有效位字节(MSB)开始传送。发送和接收数据的个数没有限制。

图7-43 I2C模块数据传输格式(8位数据的7位寻址结构)

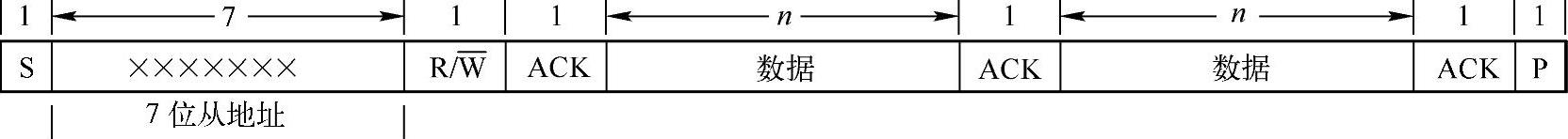

(1)7位地址格式

要选择7位地址格式,需向I2CMDR的扩展地址使能位(XA)写0,并且要确保自由数据格式关闭(即I2CMDR的FDF=0)。在如图7-44所示的7位地址格式中,起始位后的第一个字节包括7位的从机地址和1位读写选择位 。

。 位决定数据传送的方向,当

位决定数据传送的方向,当 时主机向所寻址的从机写(发送)数据;当

时主机向所寻址的从机写(发送)数据;当 时主机读(接收)来自从机的数据。

时主机读(接收)来自从机的数据。

每个字节传输完成后必须插入额外的一个时钟周期应答位(ACK)。如果在主机传送第一个字节后,从机产生应答位,则发送器就会发送n位数据。n是由I2CMDR的BC位来确定的1~8位的数。当数据发送完成后,接收器产生一个应答位ACK。

图7-44 I2C模块7位寻址格式(FDF=0,XA=0)(https://www.xing528.com)

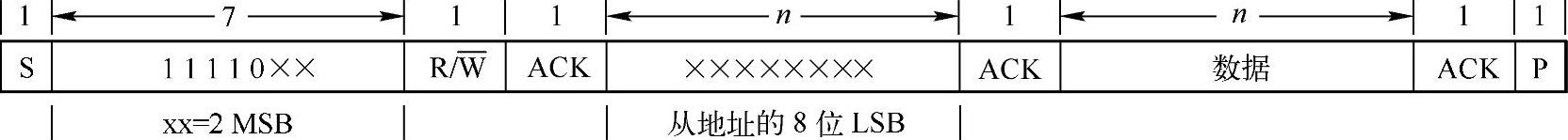

(2)10位地址格式

要选择10位地址格式,需向I2CMDR的扩展地址使能位(XA)写1,并且要确保自由数据格式关闭(即I2CMDR的FDF=0)。如图7-45所示的10位地址格式,其类似于7位地址格式,但主机通过两个单独字节的传送来发送从机地址。第一个字节包括11110b、10位从机地址的两个最高位MSBs以及一个读写选择位 (写)。第二个字节为10位从机地址剩下的8位地址。每发送完两个字节后从机必须发送一个应答信号。主机一旦向从机发送了第二个字节,就可以写数据,或者通过重复使用开始位(START)来改变数据传送方向。

(写)。第二个字节为10位从机地址剩下的8位地址。每发送完两个字节后从机必须发送一个应答信号。主机一旦向从机发送了第二个字节,就可以写数据,或者通过重复使用开始位(START)来改变数据传送方向。

图7-45 I2C模块10位寻址格式(FDF=0,XA=1)

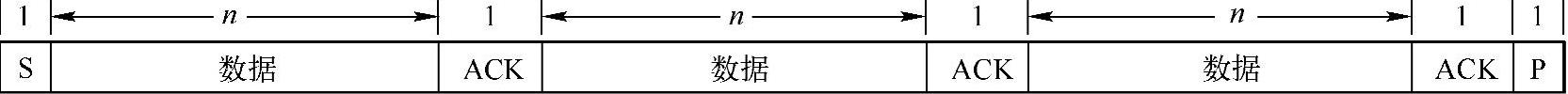

(3)自由数据格式

要选择自由数据格式,需向I2CMDR的自由数据格式位(FDF)写1。在loop-back自循环测试模式(I2CMDR的DLB=1)中不支持自由数据格式。自由数据格式见图7-46,起始位后的第一个字节是数据字节。每个数据字节后插入一个应答位,数据位的长度可以为1~8位。这种格式下不发送地址位和数据方向位。因此,发送器和接收器必须同时支持自由数据格式,并且在发送的整个过程中数据传送方向保持不变。

图7-46 I2C模块自由数据格式(FDF=1)

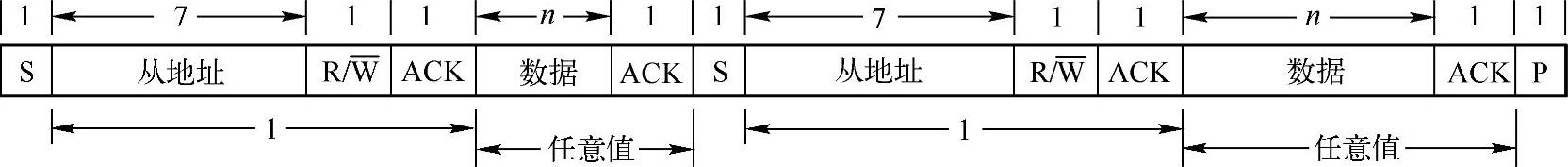

(4)使用重复起始位

每个数据字节传输结束后,主机可以再次驱动一个起始信号。使用该功能,主机可以与多个从机通信,而不需要通过驱动停止信号来放弃总线控制权。数据字节的长度可以为1~8,通过I2CMDR的BC位进行选择。在7位地址格式、10位地址格式以及自由数据格式下均可以使用重复的起始位。图7-47是7位地址格式下使用重复起始位的例子。

图7-47 重复起始位操作(7位寻址模式)

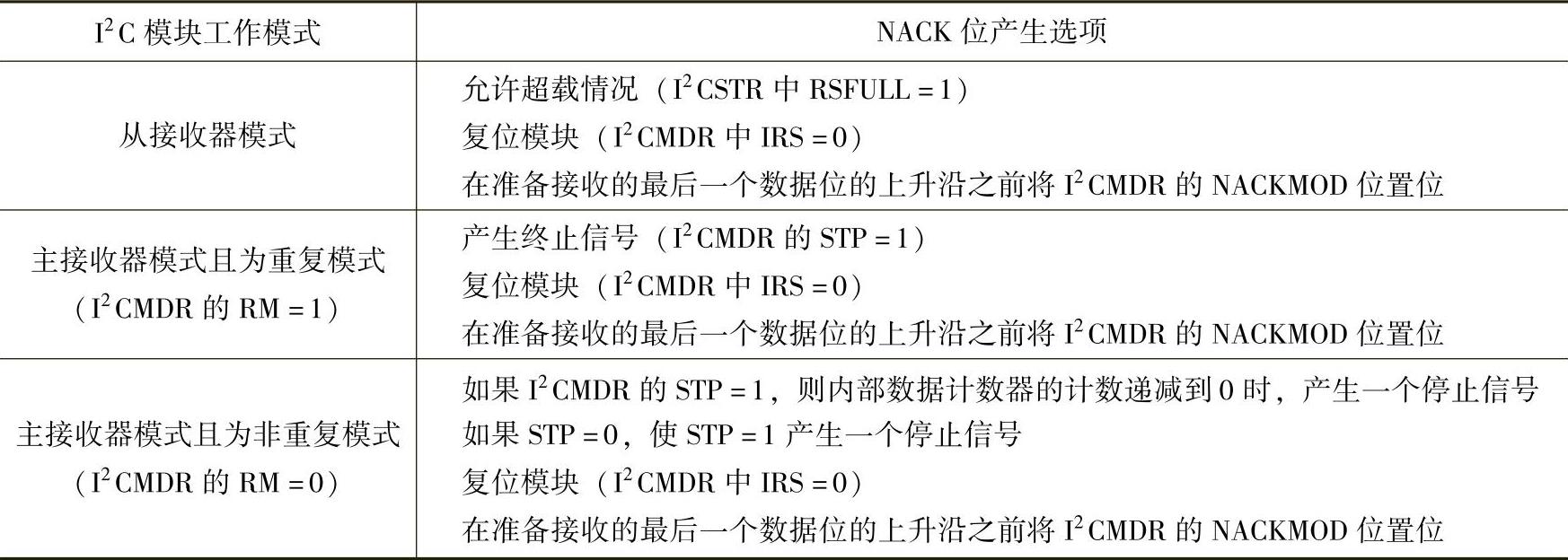

6.NACK位方式

当I2C模块为接收器时(主或从),可以响应或者忽略发送器发送的数据位。忽略任何新的数据位,I2C模块都必须在总线的应答周期期间发送一个非应答位。表7-49描述了不同工作模式下产生非应答位NACK的各种方法。

表7-49 产生NACK位的方法

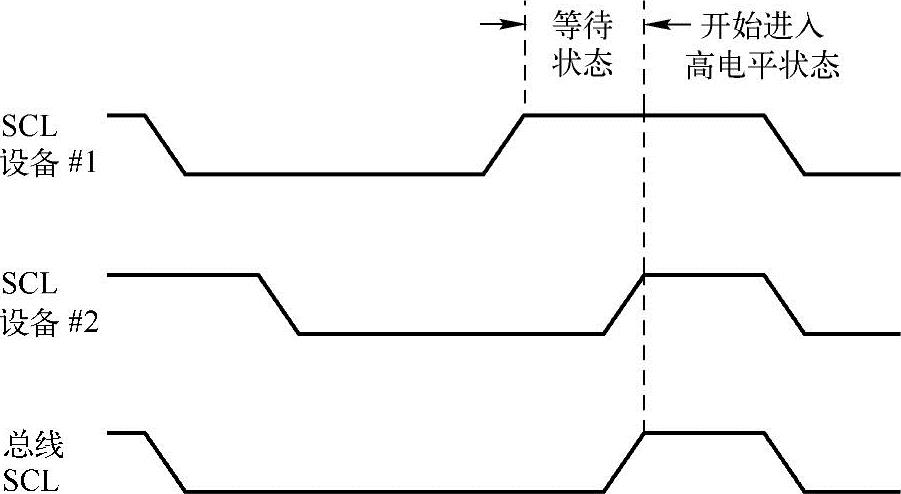

7.时钟同步

通常情况下,I2C只有一个主设备产生时钟信号SCL。但是,在仲裁程序中,存在两个或更多的主设备。因此,为使输出的数据能够匹配,必须保持时钟同步。图7-48给出了时钟同步时序图。SCL的“线与”特性即是指在SCL上首先产生低电平的设备将会控制其他设备。这个由高到低的跳变,强制其他设备的时钟发生器开始其低电平周期。并且只要有设备的时钟信号为低则SCL一直保持为低电平。必须等到SCL被释放后其他设备才能结束它们的低电平周期,开始其高电平周期。SCL上产生的同步信号中,低电平周期的长度由最慢的设备决定,高电平周期的长度由最快的设备决定。

图7-48 仲裁过程中两I2C模块时钟的同步

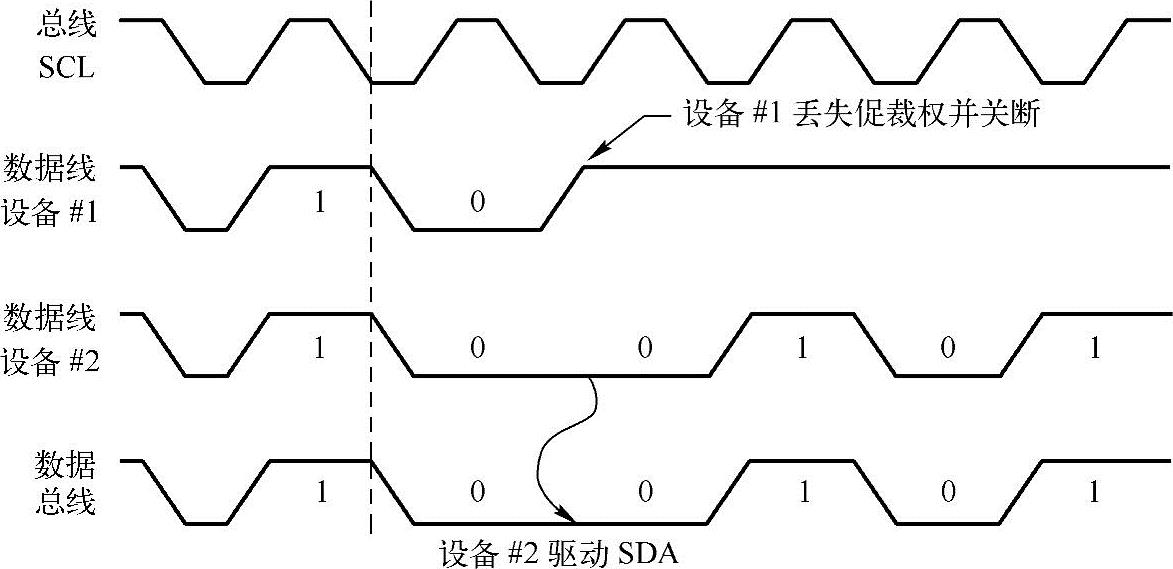

8.仲裁

如果同时有两个或更多主发送器试图在同一时刻、同一总线上发送数据,则需启动仲裁程序。仲裁机制将使用各竞争发送器数据线(SDA)上出现的数据进行仲裁。图7-49说明了两个设备之间的仲裁过程。第一个主发送器将SDA线置高时(被视为释放SDA),数据线就会被另一个置SDA为低的主发送器所控制。仲裁机制总是将优先权给那些发送的数据在二进制形式中值最小的设备。因此,当两个或更多的设备发送相同的首字节,仲裁机制会继续根据随后的字节进行仲裁。

图7-49 两个主发送器之间的仲裁过程

对于竞争失败的I2C主设备,其将切换到从接收器模式,将仲裁失败标志位(AL)置位,并且产生仲裁失败中断请求。

如果在串行数据发送中且仲裁程序仍然在进程时,发送一个重复的起始位或是停止位给SDA时,所涉及的主发送器必须在格式帧的相同位置发送一个重复的起始位或停止位。仲裁不允许在重复的起始位和数据位之间、停止位和数据位之间、重复的起始位和停止位之间产生。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。