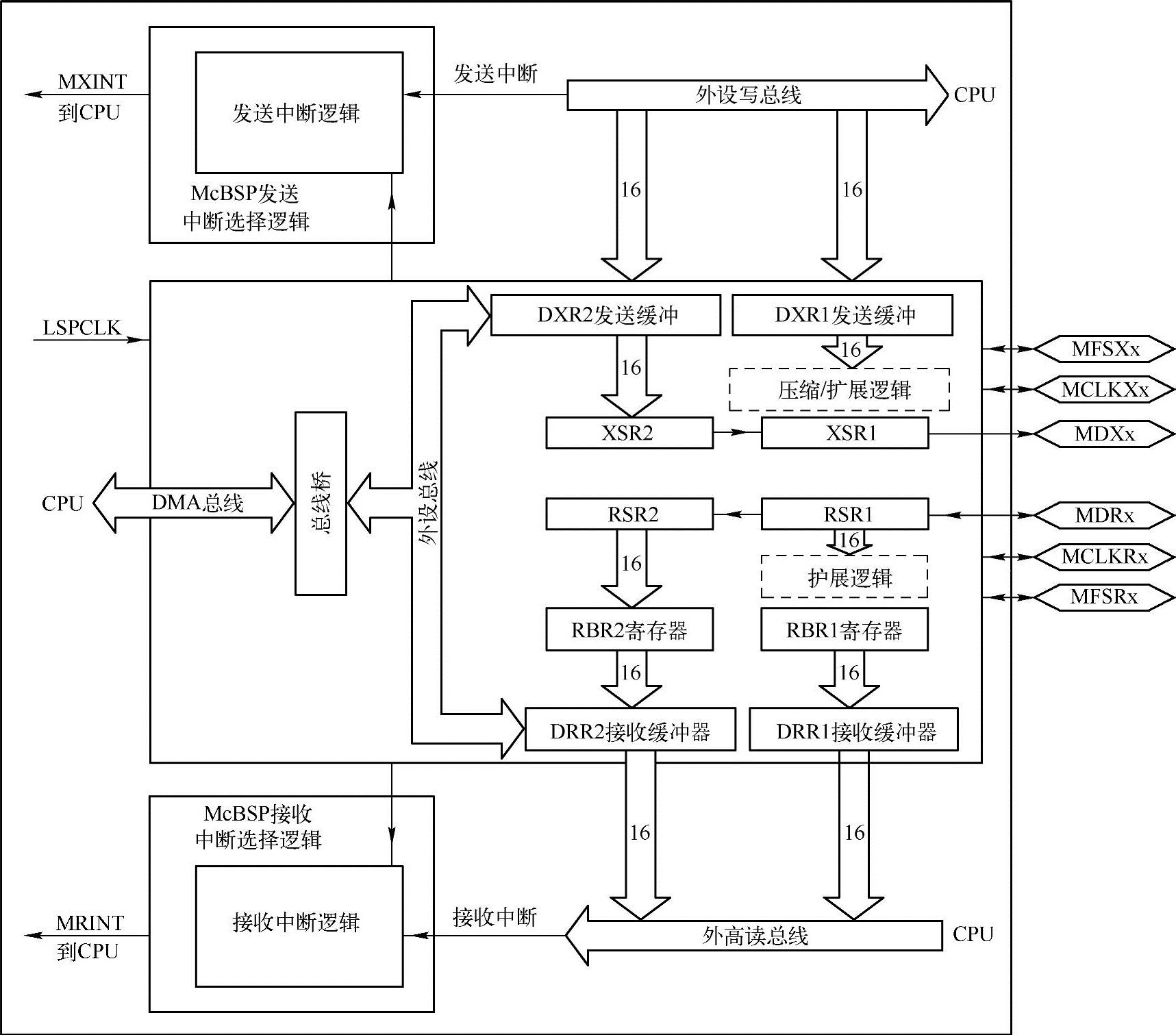

2833x系列器件提供了两个高速多通道缓冲串口(McBSP),可以与CODEC或系统其他器件直接相连。McBSP包含了与器件相连接的数据端口和控制端口,共6个引脚,如图7-14所示。

图7-14 McBSP模块结构图

McBSP通过数据发送引脚(DX)发送数据,通过接收引脚(RX)接收数据,时钟和帧同步信号通过引脚CLKX(发送时钟)、CLKR(接收时钟)、FSX(发送帧同步)、FSR(接收帧同步)进行传输。CPU和DMA可以通过内部的外设总线访问McBSP的16位宽寄存器。CPU或DMA控制器将要传送的数据写入到数据发送寄存器(DXR1,DXR2)。写入到DXRx的数据将通过发送移位寄存器(XSR1,XSR2)从DX引脚移出。同样,引脚DR上接收到的数据移入到接收移位寄存器(RSR1,RSR2),并复制到接收缓冲寄存器(RBR1,RBR2),然后RBRx的内容复制到可以被CPU或DMA控制器访问的数据接收寄存器(DRR1,DRR2)。这就允许内部和外部数据通信同时进行。

当串行字的长度为8位、12位、16位时,不需要用到DRR2、RBR2、RSR2、DXR2、XSR2寄存器;当串行数据长度大于16位时,则需要用到这些寄存器存放数据的高有效位。

帧同步和时钟信号的回送模式即是使用CLKX和FSX信号驱动CLKR和FSR信号。如果回送模式被使能,CLKR和FSR信号将从CLKX和FSX信号获得,而不是从CLKR和FSR引脚。

McBSP有如下特性:

●全双工通信方式。

●双缓冲发送数据和三缓冲接收数据,允许连续数据流操作。

●发送和接收具有独立时钟和帧同步的信号。

●具有向CPU传送中断请求和向DMA控制器传送DMA事件的功能。

●128个发送和接收通道。(https://www.xing528.com)

●多通道选择模式可以允许或禁止每一通道的传输。

●与工业标准的CODEC、模拟接口器件(AIC)及其他串行接口ADC模块和DAC模块直接连接。

●支持外部的时钟信号和帧同步信号。

●内有可编程的采样率发生器,用以发生和控制内部时钟信号及帧同步信号。

●帧同步信号和时钟信号的极性可编程。

●与T1/E1帧调节器、IOM-2兼容设备、AC97兼容设备、I2S兼容设备、SPI设备的直接连接。

●数据长度选择范围宽可以是8、12、16、20、24、32位。

●μ-律和A-律格式数据压缩扩展。

●发送或接收8位数据时,可以先传送最低有效位。

●有异常/错误状态标志位。

●不支持ABIS模式。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。