当ADC模块工作在排序器覆盖功能使能的连续转换模式时,DMA提供了与ADC模块排序器1中断(SEQ1INT)同步的硬件方法。在这种特定的模式下,ADC模块连续转换ADC模块排序通道,且不需在排序器转换结束后复位排序器指针。当接收到触发事件时,因为DMA不知道排序器指针指向的是哪个ADC模块结果寄存器,故DMA和ADC模块步调可能不一致。为此,当ADC模块配置成此模式时,每当从结果寄存器0(RESULT0)开始转换序列并有中断触发事件发生时,ADC模块为DMA提供同步信号。DMA将该信号视为打包进程或开始传送数据的同步信号。若DMA未进行此操作,则会发生重新同步,即:

●重新将WRAP_SIZE值装载到WRAP_COUNT寄存器中。

●将当前工作BEG_ADD寄存器值装载到当前工作ADDR寄存器中。

●将CONTROL寄存器的SYNCERR位置位。

若有需要,允许使用多个缓冲器存储数据,并使DMA和ADC模块重新同步。举例来说,假设排序器1每次转换4个ADC模块通道,因为排序器1最大转换长度是8,所以排序器每隔一个转换序列都会自身复位并且产生同步信号;再假定DMA将第一次4个通道的转换结果放置在缓冲器A,第二次4个通道的转换结果放置在缓冲器B。若DMA操作超载,中断触发事件丢失,DMA和ADC模块将失去同步。这种情况下,DMA将CONTROL寄存器中的SYNCERR位置位,并且执行上述的重新同步操作,使DMA和ADC模块回到同步状态。通过MODE寄存器中的SYNCSEL位,同步特性可配置工作在源地址或目的地址指针。(https://www.xing528.com)

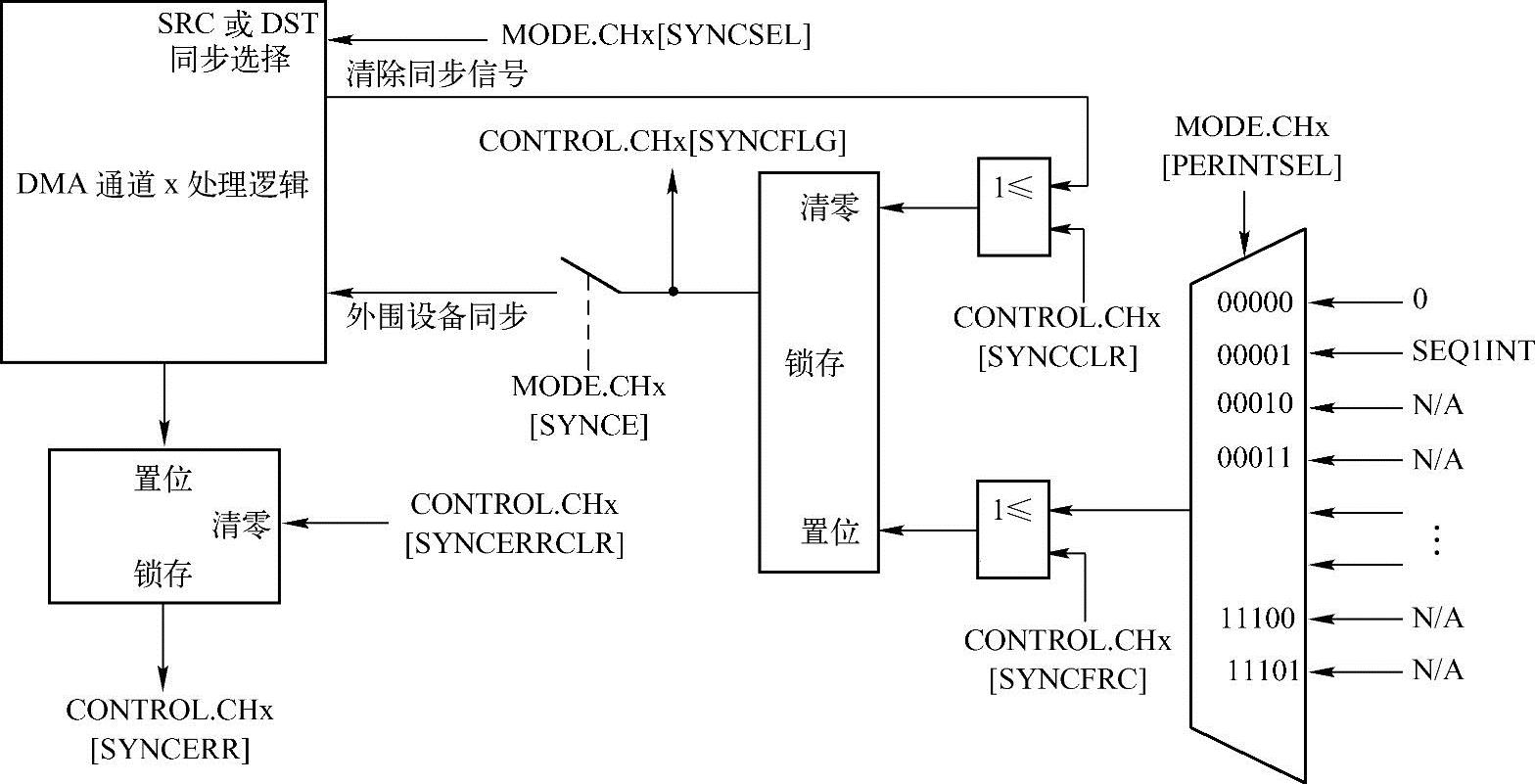

如图5-22所示,同步信号源由MODE寄存器中的PERINTSEL位选择。若对选定的源和通道使能了同步特性(SYNC),则在RUN位被置位后接收到第一个SYNC信号时,才开始所选定通道的传送。在第一个SYNC事件发生前,所有的外设中断触发事件都将被忽略。

图5-22 ADC模块同步输入框图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。