1.GPIO翻转例程

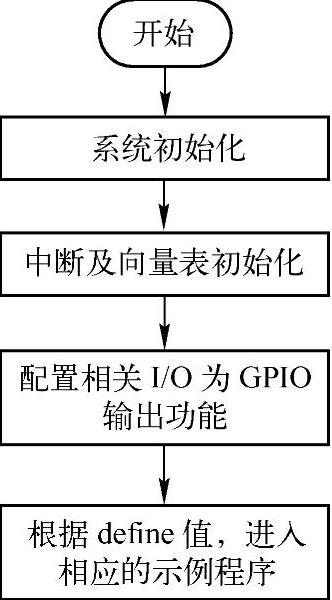

该程序源代码来源于TI官网V131中的gpio_toggle例程,主要演示改变GPIO输出电平状态的3种方法,即分别通过直接修改GPxDAT的值、通过修改GPxSET/GPxCLEAR的值和通过GPxTOGGLE来实现GPIO口输出状态的改变。程序流程图如图5-3所示。

图5-3GPIO例程(GPIO翻转)主程序流程图

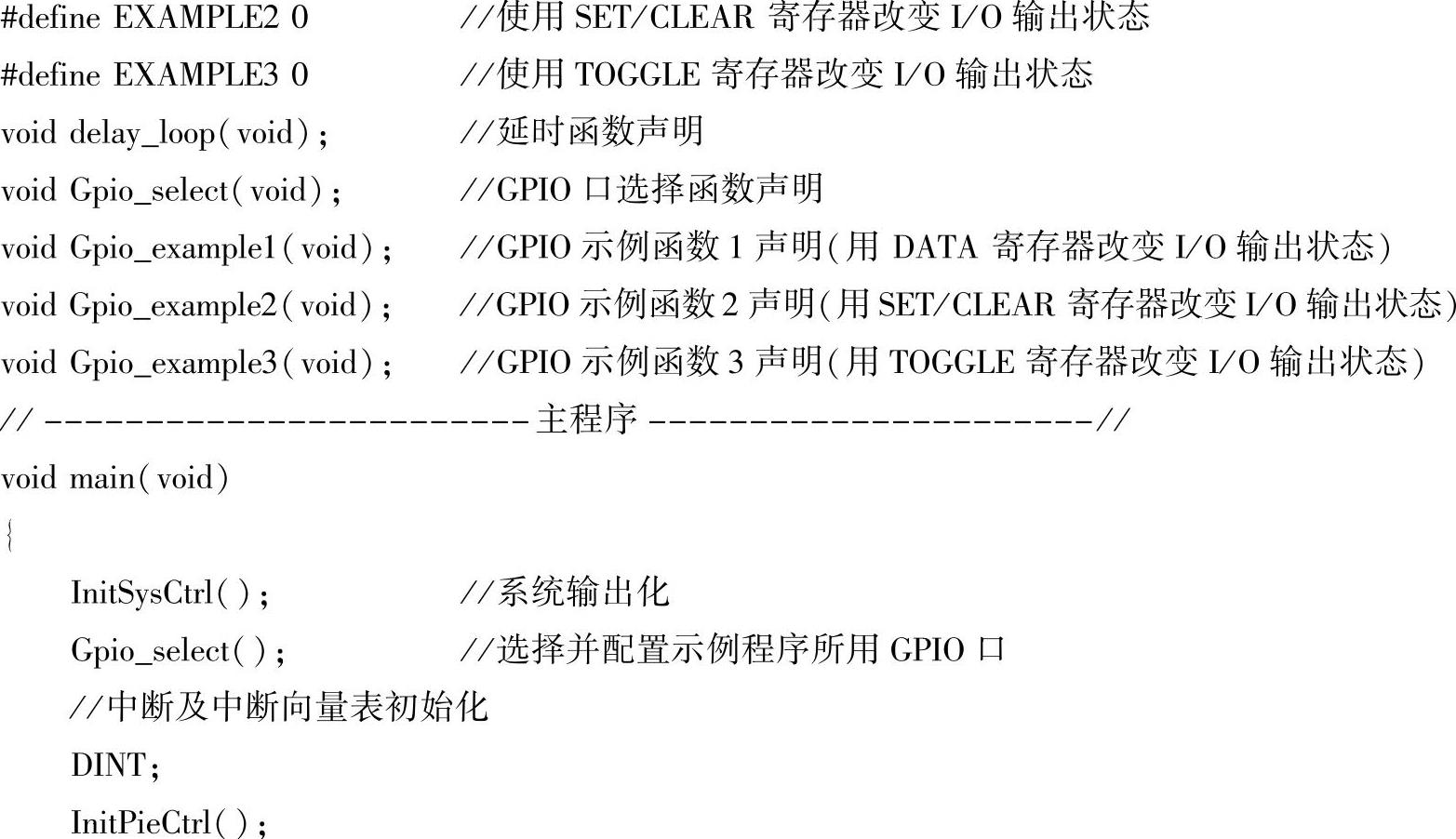

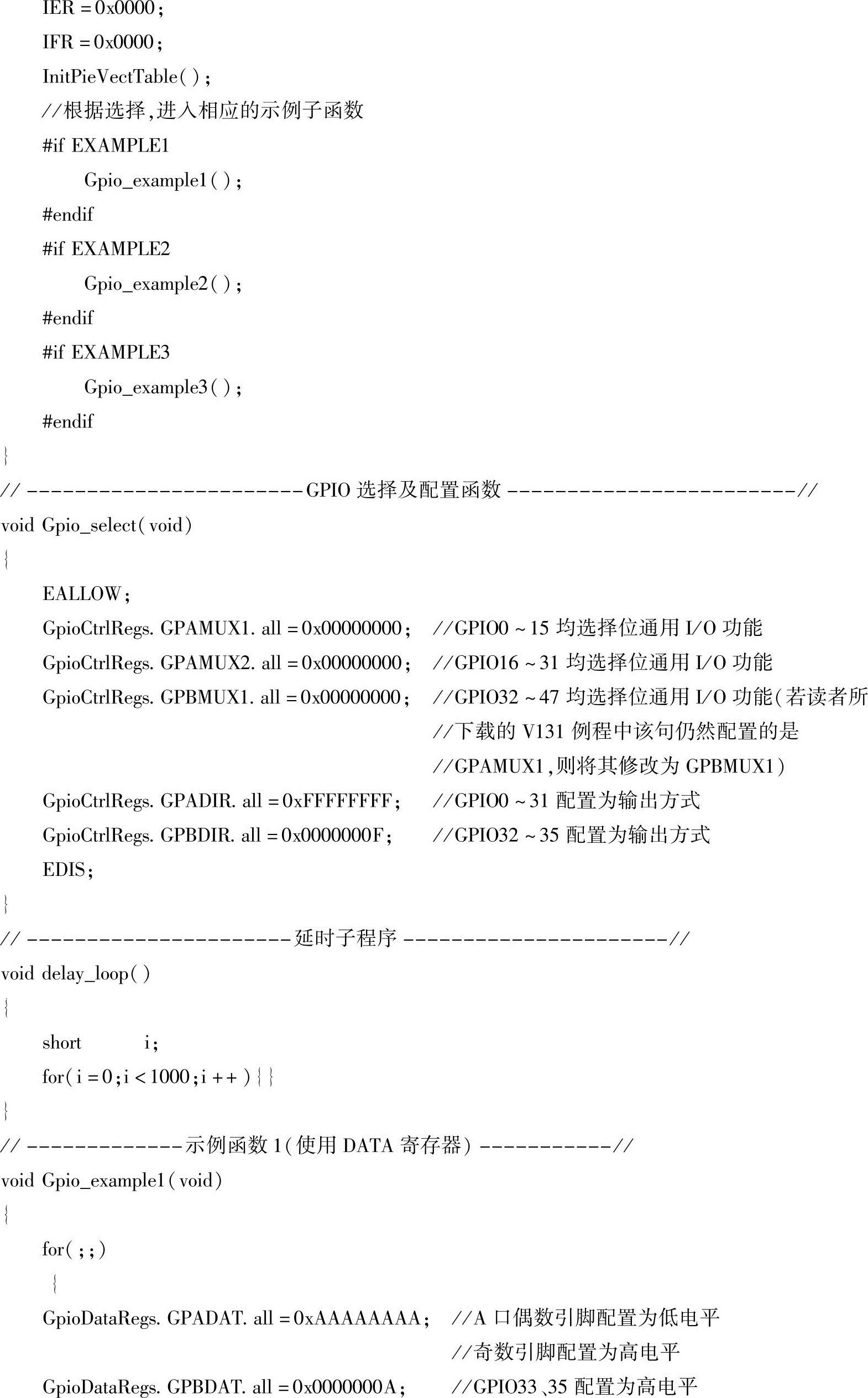

源程序代码及解读如下:

这里需要注意的是,虽然通过修改GPxDAT的内容可以设定GPIO的输出电平,但是一般采用通过GPxSET/GPxCLEAR或GPxTOGGLE来设置GPIO输出电平。(https://www.xing528.com)

2.GPIO外部引脚中断

工程实践中,常需要采用外部ADC模块对信号进行采样转换,这就涉及DSP对ADC模块采样中断的响应处理。ADC模块一般都包含RDY引脚,在A-D模块转换完成前,其输出高电平;当A-D转换完成后,其输出低电平;当A-D转换结果读取后,该引脚又变为高电平。将该引脚连接至DSP的外设中断输入引脚,通过合理配置,便可以及时响应ADC模块中断。

本程序功能描述:在DSP板上模拟对外部ADC模块采样中断的响应,使用GPIO3来模拟ADC的RDY引脚;使用GPIO5作为外设中断1的输入引脚,即将GPIO3与GPIO5相连;使用CPU timer0产生的1ms周期中断来模拟触发ADC模块周期性转换。在CPU timer0中断服务函数内,将GPIO3置为低电平,模拟A-D转换完成后RDY引脚的状态变化;之后DSP将响应GPIO5的外部中断,模拟响应RDY引脚触发的中断,在该中断服务函数内,将GPIO3置为高电平,模拟A-D转换结果读取后RDY引脚的状态变化。程序流程图如图5-4所示。

图5-4 GPIO例程(外部引脚中断)主程序流程图

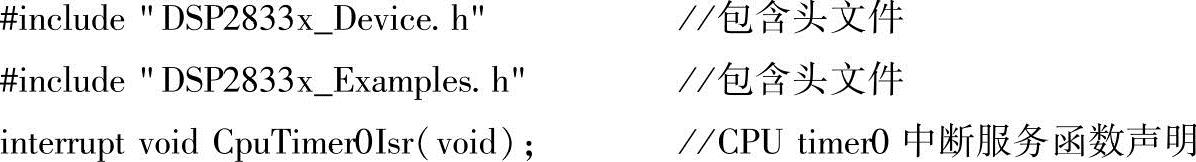

源程序如下:

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。