28x系列CPU支持一个不可屏蔽中断(NMI)和16个具有优先级可屏蔽的CPU级中断请求(INT1~INT14、RTOSINT及DLOGINT)。28x器件有许多片内外设,每个外设在相应事件发生时都可以产生一个或多个中断。但CPU无法在CPU级处理这么多的外设中断请求,因此用PIE控制器仲裁来自外设和外部引脚的中断请求。

PIE向量表用来存储系统中每个中断服务程序(ISR)的入口地址,每个中断源(包括复用和非复用中断)都有一个中断向量。在设备初始化时就要设置好中断向量表,在具体操作中可以根据需要对其进行修改。

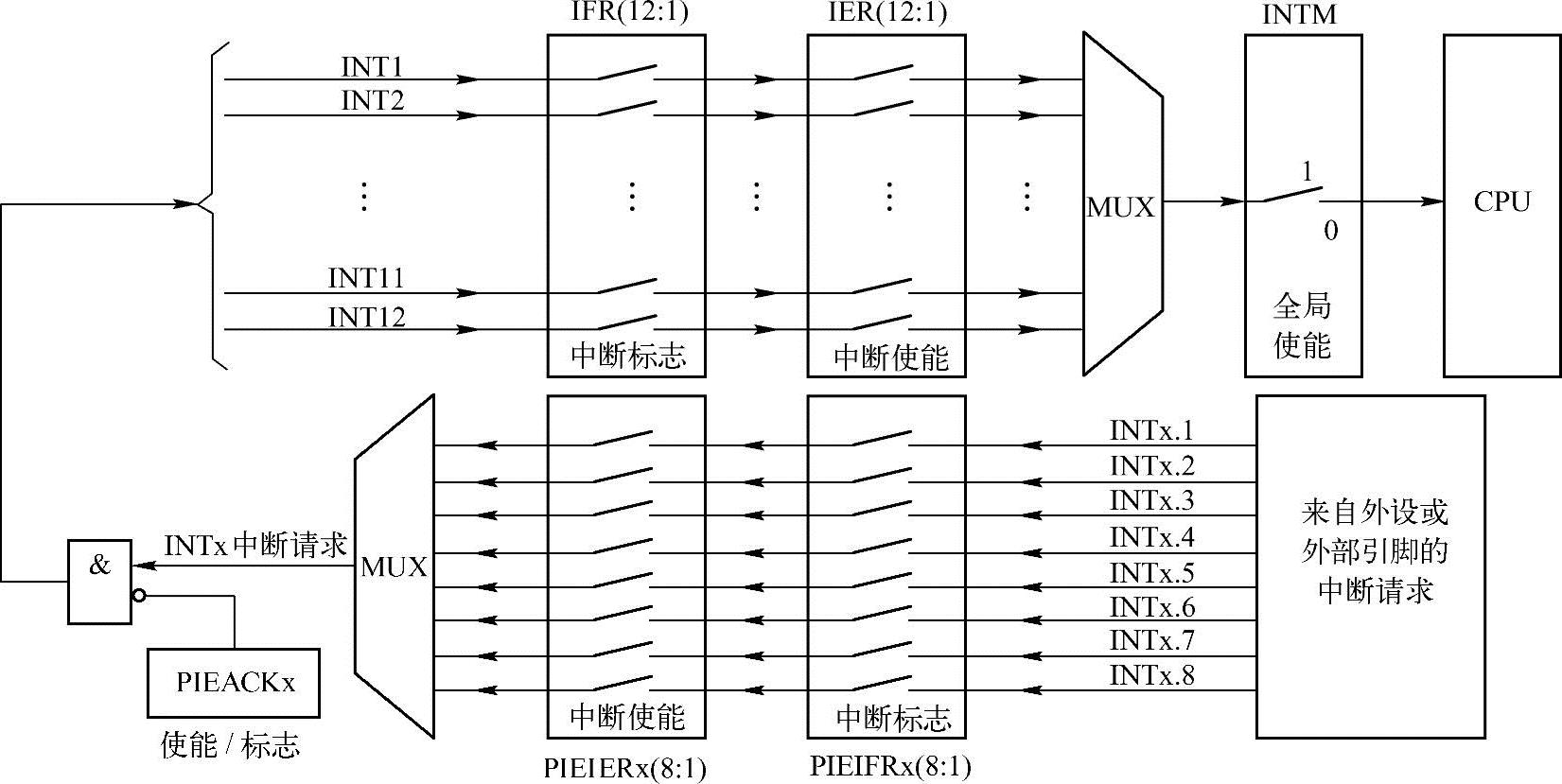

图4-9描述了所有复用PIE中断的操作时序。未复用的中断源直接连到CPU。

图4-9 利用PIE模块复用中断示意图

由图可见,中断系统包括外设级、PIE级和CPU级三个层次。

(1)外设级

外设中,触发中断的事件发生时,会将寄存器中相应的中断标志位(IF)置位。在外设级,如果该中断的使能位(IE)被置位,则外设会向PIE模块产生中断请求;如果该中断没有被使能,则IF将保持置位状态直至被软件清零;如果该中断在稍后被使能并且IF处于置位状态,外设仍然向PIE模块产生中断请求。需要注意的是,中断标志位需要手动清零。

(2)PIE级

PIE模块使来自外设或外部引脚的8个中断复用一个CPU级中断信号。PIE模块将所有的中断源分成12组:(PIE分组为1~12)。在同一PIE分组将共用一个CPU中断,例如PIE分组1中的中断共用CPU中断1(INT1),PIE分组12中的中断共用CPU中断12(INT12)。直接连接到CPU级中断的中断源则不需要与其他中断源复用中断。对于不需要复用的中断,PIE模块直接将中断请求送至CPU。

对于共用同一个CPU中断的中断组,在PIE模块都有一个相应的标志寄存器PIEIFRx和使能寄存器PIEIERx(x为1~12)。这些寄存器的每一位都对应着一个中断分组中的某一个中断,因此PIEIFRx.y和PIEIERx.y就对应着第x(x=1~12)个中断分组中的第y(y=1~8)个中断。另外,每一个中断分组都对应着一个中断应答位PIEACKx(x=1~12)。

一旦外设向PIE发送了中断请求,PIE相应的中断标志位(PIEIFRx.y)就会被置位;如果PIE中断使能位(PIEIERx.y)也被置位,则PIE就会检查相应的PIEACKx位来判断CPU是否准备好响应该组的中断。如果PIEACKx被置位,则PIE将等待直到该位被清零,然后发送中断请求至INTx。(https://www.xing528.com)

(3)CPU级

中断请求信号送至CPU后,与INTx相对应的CPU级中断标志位将被置位。该标志位锁存至IFR,如果CPU中断使能寄存器(IER)、调试中断使能寄存器(DBGIER)或全局中断屏蔽寄存器(INTM)的相应位被使能,那么CPU将会响应该中断。

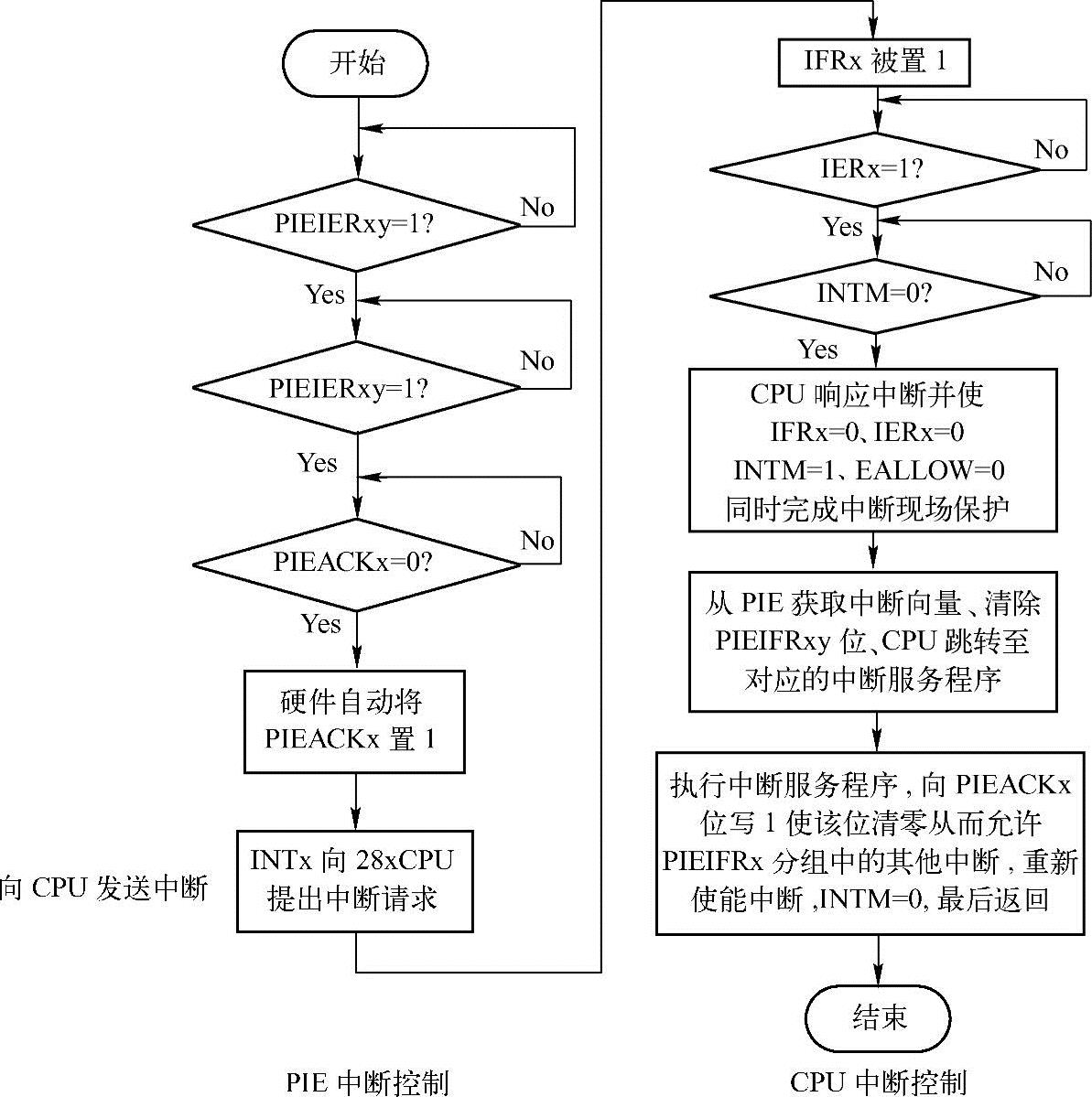

图4-10为典型的PIE/CPU中断响应流程图。需要注意的是,在CPU响应中断后,IERx会被自动清零,INTM会被自动置位,阻止其他中断;在中断服务程序执行完毕后,需要应答PIEACKx,以允许该PIE分组的其他中断;在中断返回时,IERx、INTM会自动回至原始值,即IERx=1、INTM=0,以重新使能中断。

图4-10 典型的PIE/CPU中断响应流程图

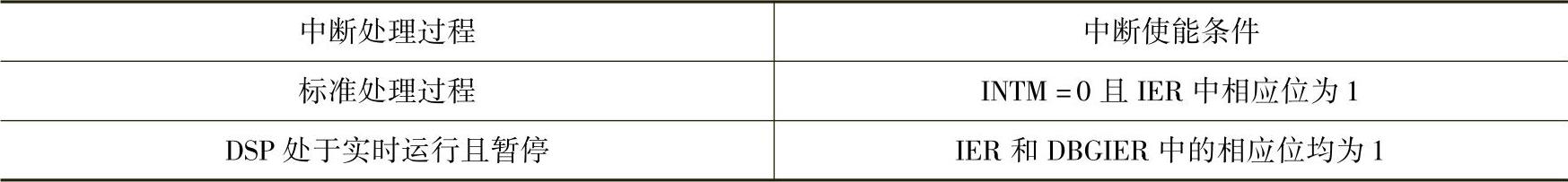

在CPU级使能可屏蔽中断的条件取决于CPU采用何种中断处理过程,具体见表4-19。一般常用的是标准中断处理过程,此时不需要用到DBGIER寄存器;当28x器件工作在实时仿真模式并且CPU停止时,需要用到另外一种中断处理过程。在这种特定的情况下,需要用到DBGIER寄存器并且INTM位将被忽略;当DSP工作在实时仿真模式下且CPU正在运行时,仍然采取标准的中断处理过程。

表4-19 中断使能

在CPU响应中断的准备阶段,寄存器IFR和IER的相应位被清零,EALLOW和LOOP也被清零,INTM和DBGM被置位,刷新流水线,保存中断返回地址和现场信息。中断服务程序(ISR)的向量表将从PIE模块获得。如果中断请求来自复用的中断源,PIE模块通过对PIEIERx和PIEIFRx寄存器内容解码来判断响应哪一个中断。

需要执行的中断服务程序的入口地址将直接从PIE模块的中断向量表中获得。PIE模块中,96个中断都各自对应一个32位的向量。当获取中断向量后,PIE模块的中断标志位(PIEIFRx)将自动清零。在执行完中断服务程序后,PIE分组的中断应答位需要手动清零,以使PIE能响应下一个同一PIE分组的中断。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。