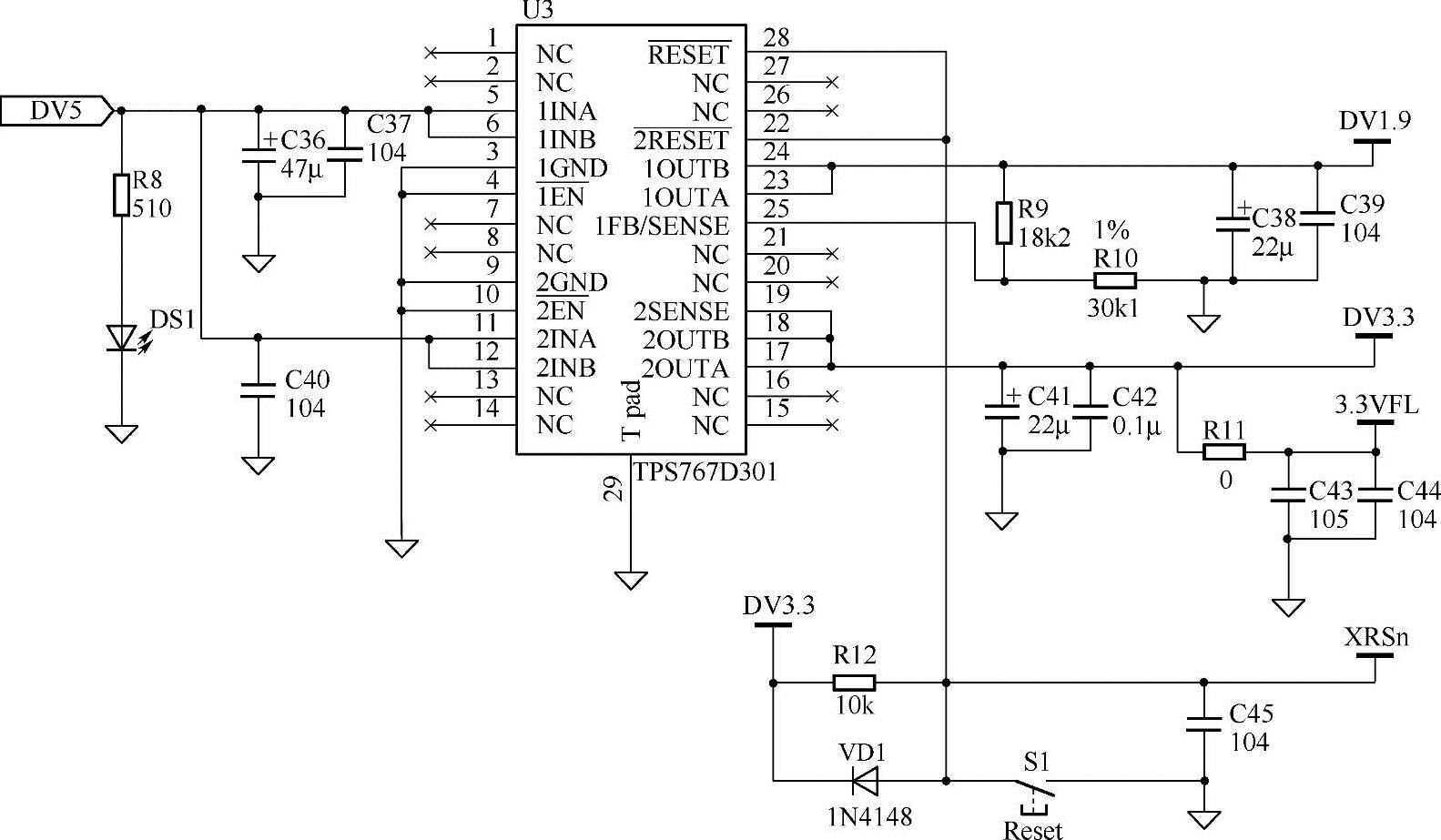

TMS320F2833x芯片的内核供电电压为1.9V@150MHz/1.8V@100MHz,I/O端口供电电压为3.3V。根据电源的获取途径,可以采用LDO的形式,也可以采用DC/DC+LDO的结构,一种典型的电源电路就是采用具有双路电压输出功能的LDO芯片TPS767D301,来得到3.3V和1.9V/1.8V电压,如图2-8所示(这里为F28335供电,输出的内核电压为1.9V)。TPS767D301主要为C2000 DSP的应用而设计,其中一路可调节的LDO是通过外部电阻分压来获得输出电压1.9V/1.8V,输出电压满足:

其中,VREF为芯片内部参考电压。

另外一路固定输出的LDO直接输出3.3V。F2833x芯片的1.9V/1.8V和3.3V可同时上电,因此这里直接将双路LDO的输入使能引脚接地,同时使能。TPS767D301带复位功能,当输出电压降为正常值的95%时(DSP正常工作时的最小电源电压),复位引脚

输出低电平,另外电压恢复正常后,延时200ms复位引脚才跳为高电平,将该引脚接至DSP的复位引脚XRS,能保证DSP上电、掉电、欠电压时可靠复位。

输出低电平,另外电压恢复正常后,延时200ms复位引脚才跳为高电平,将该引脚接至DSP的复位引脚XRS,能保证DSP上电、掉电、欠电压时可靠复位。

图2-8 电源与复位(https://www.xing528.com)

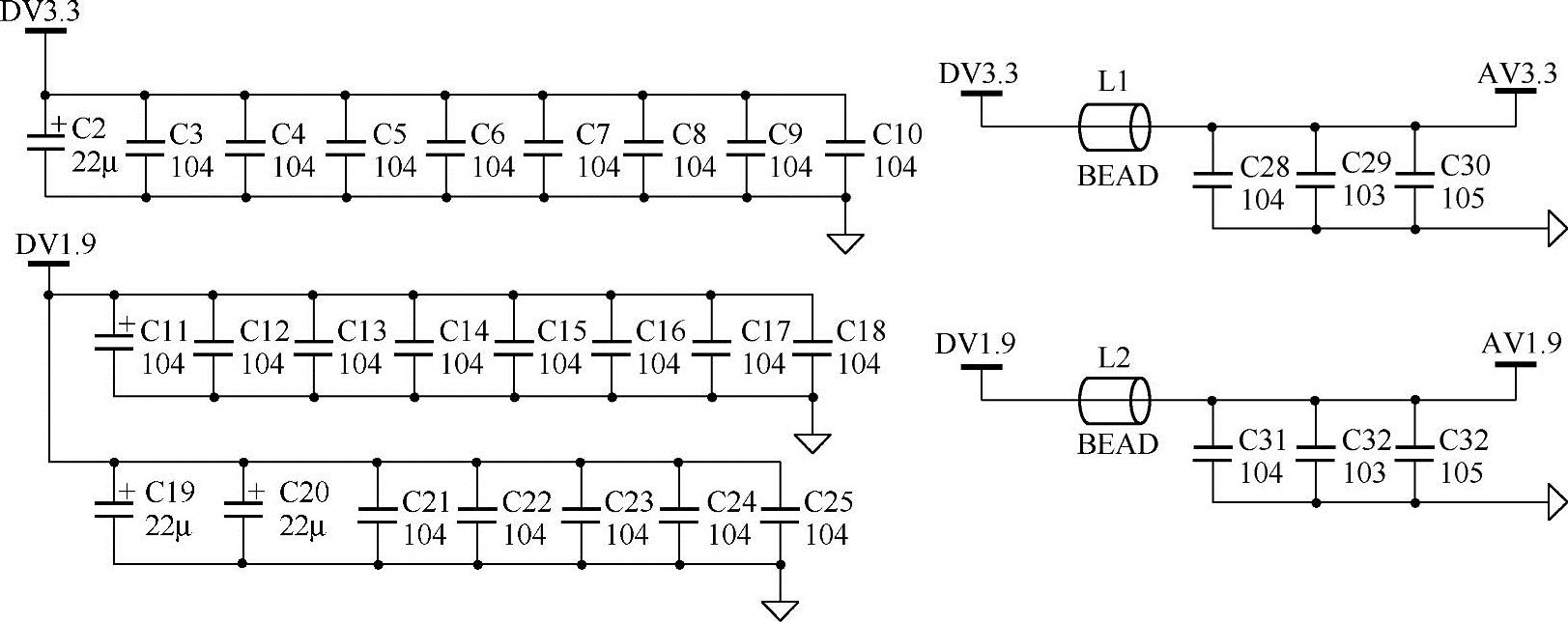

数字电源DV3.3/DV1.9经磁珠隔离,得到模拟电源AV3.3/AV1.9。数字电源DV3.3/DV1.9及模拟电源AV3.3/AV1.9经过电容退耦后,直接接至DSP相应的电源引脚,如图2-9所示。电源退耦电容一般就近放在DSP的每个电源引脚旁,用于抑制DSP工作时引起的“地弹”噪声,确保电源稳定。

图2-9 电源与退耦电容

除LDO自带的复位功能外,图2-8还加入了手动按键复位电路,由上拉电阻(R12)、续流二极管(VD1)、电容(C45)构成。续流二极管可在系统掉电时将电阻R12短路,给电容C45提供快速放电回路,另外还可起到钳位保护和ESD防护的作用。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。