1.C28xCPU+FPU

F2833x(C28x+FPU)是TMS320C2000系列数字信号控制器平台的一员,基于控制器的C28x+FPU与TI已存在的C28xDSCs具有相同的32位定点处理结构,但也包含了单精度(32位)IEEE754浮点单元(FPU)。其支持C/C++,使用户能够使用高级语言来开发系统控制软件,也能够使用C/C++语言来开发数学算法。该设备在数字信号处理能力与微处理器的系统控制能力方面均十分有效,其高效性避免了许多系统对第二个处理器的需求。32×32位MAC、64位处理能力使控制器能高效地处理更高级的数值解析问题。除此之外,带有关键寄存器内容自动保存功能的快速中断响应,使得设备能够快速处理多个异步事件。该设备带有8级深保护流水线,该流水线可使设备高速执行指令,而无需使用昂贵的高速存储器。

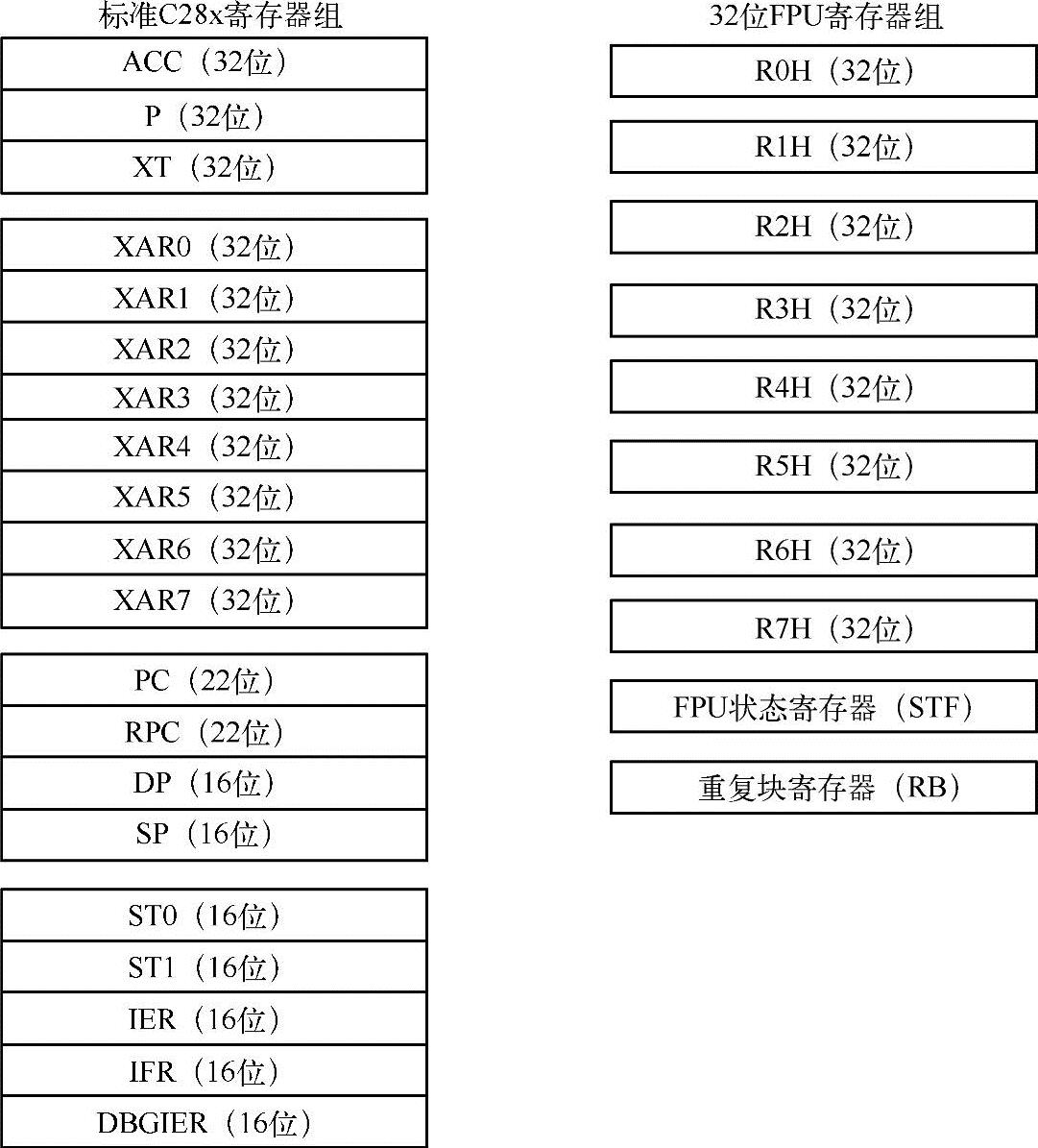

CPU主要的寄存器如图2-6所示。

图2-6 CPU主要寄存器

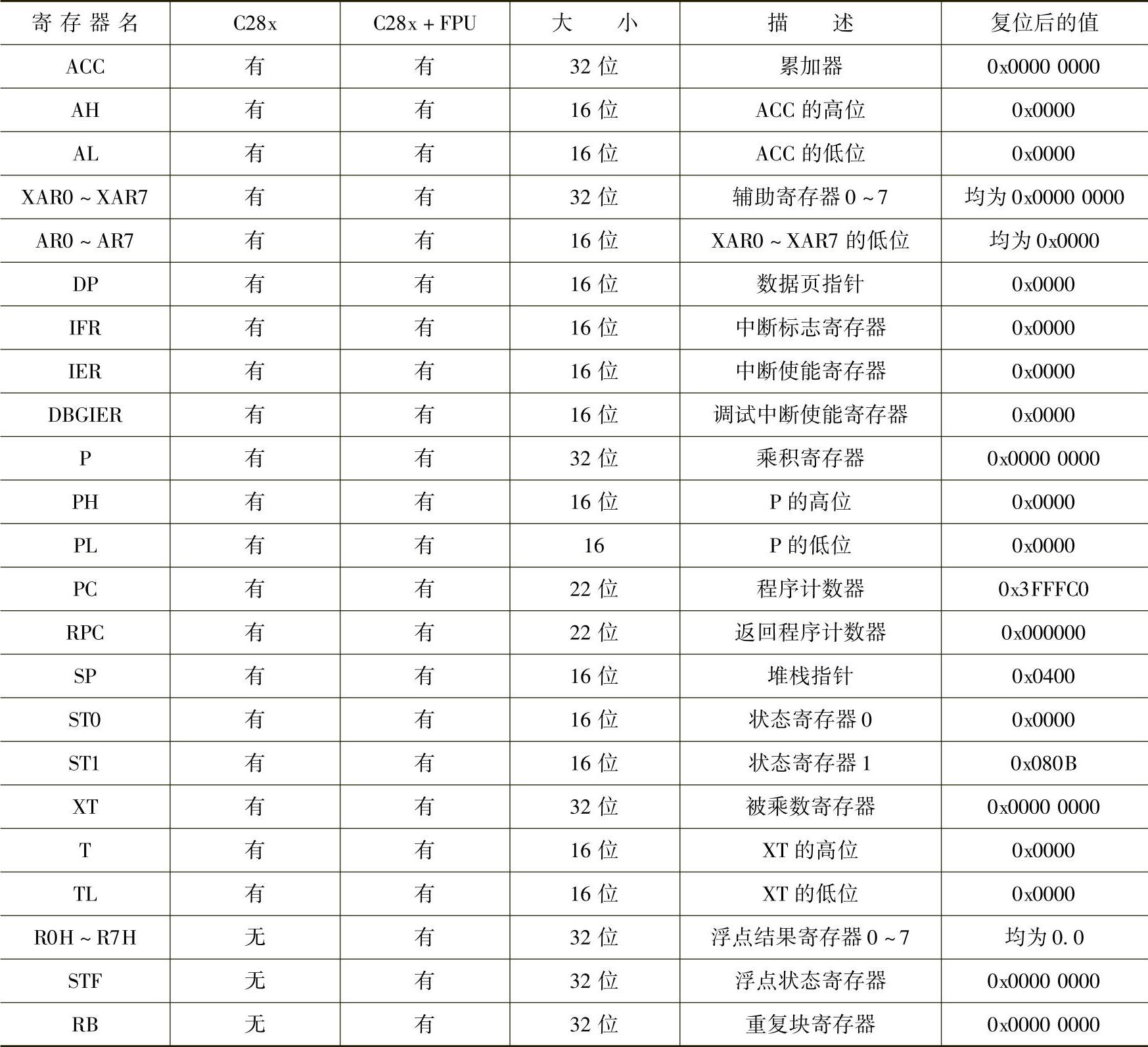

各寄存器的说明见表2-6。

表2-6 CPU寄存器说明

2.存储器总线(哈佛总线结构)

多种总线用来在存储器、外设和CPU之间移动数据。C28x存储总线结构包含一个程序读总线、数据读总线和数据写总线。程序读总线由22位地址线和32位数据线组成。数据读、写总线由32位地址线和32位数据线组成。32位数据线使单周期进行32位操作成为可能。这种通常被称为哈佛总线的多总线结构,可使C28x在一个单周期内完成取指令、读、写数据。在外设和存储器同时访问存储器总线时,将优先考虑存储器访问。

3.外设总线

为了能在不同的TIDSC设备之间移植外设,F2833x采用了外设总线标准。外设总线桥可以复用不同总线,将存储器总线整合为包含16位地址线和16或32位数据线以及相关控制信号的单总线。F2833x支持3种版本的外设总线:仅支持16位访问的版本(称作外设帧2);支持16/32位访问的版本(称作外设帧1);支持DMA访问和16/32位访问的版本(称作外设帧3)。

4.实时JTAG仿真分析

F2833x采用标准的IEEE 1149.1 JTAG接口。此外,设备支持实时操作模式,即在处理器运行、执行代码、服务中断时,存储器、外设和寄存器中的内容可以被修改。在使能了实时中断后,用户可以单步运行无实时性要求的代码,这样并不影响对中断的响应。F2833x也可以在硬件的CPU内实现实时模式,这是2833x/2823x设备一个特有的性能。此外,提供了特别的硬件分析,例如允许设置硬件断点或数据/地址观测点,以及当匹配事件发生时,产生多个供用户选择的断点事件。

5.外部接口XINTF

该异步接口包括20位地址线,32位数据线和3个片选线。片选线被映射到3个外部区域,分别为0、6和7。每个区域都可以独立配置各自的等待状态数、选通信号建立和保持时间,并且可以配置是否使用外部扩展等待状态数。这些可编程的等待状态、片选和可编程的选通时序可以实现与外部存储器及外设间的无缝连接。

6.Flash

F28335包含256K×16位的Flash存储器,分成了8个32K×16位的扇区;F28334包含128K×16位的Flash存储器,分成了8个16K×16位的扇区;F28332包含64K×16位的Flash存储器,分成了4个16K×16位的扇区。F2833x还包含1K×16位的OTP存储器,地址范围为0x380400~0x3807FF内。用户可以单独对Flash中任意一扇区进行擦写、编程和验证,而不更改其他扇区。但是不能用Flash或OTP中的某扇区来执行擦写/编写其他扇区的程序。Flash/OTP被映射到程序和数据空间,可以用来执行代码或存取数据。需要注意的是,空间0x33FFF0~0x33FFF5是保留给数据变量的,不能包含程序代码。Flash和OTP的等待状态数可根据实际应用配置。这使得应用程序在较低频率下运行时,可以配置Flash使用较少的等待状态数。通过使能Flash选项寄存器中的流水线模式,可以提高性能。

7.M0、M1 SARAM

F2833x包含两个单口RAM存储器,每块大小为1K×16位。复位时,堆栈指针指向M1块的开始处。像其他存储器块一样,M0和M1块可被映射到程序和数据空间。因此,用户可以使用M0和M1来执行代码或存放数据变量,而存储区域的分配是在链接文件中完成的。

8.L0~L7 SARAM

F28335/F28334包含32K×16位的单口RAM,并被分成8块(L0~L7,每块4K);F28332包含24K×16位的单口RAM,并被分成6块(L0~L5,每块4K);每块都可以独立访问,且都被映射到程序和数据空间。其中,L4~L7可以被DMA访问。

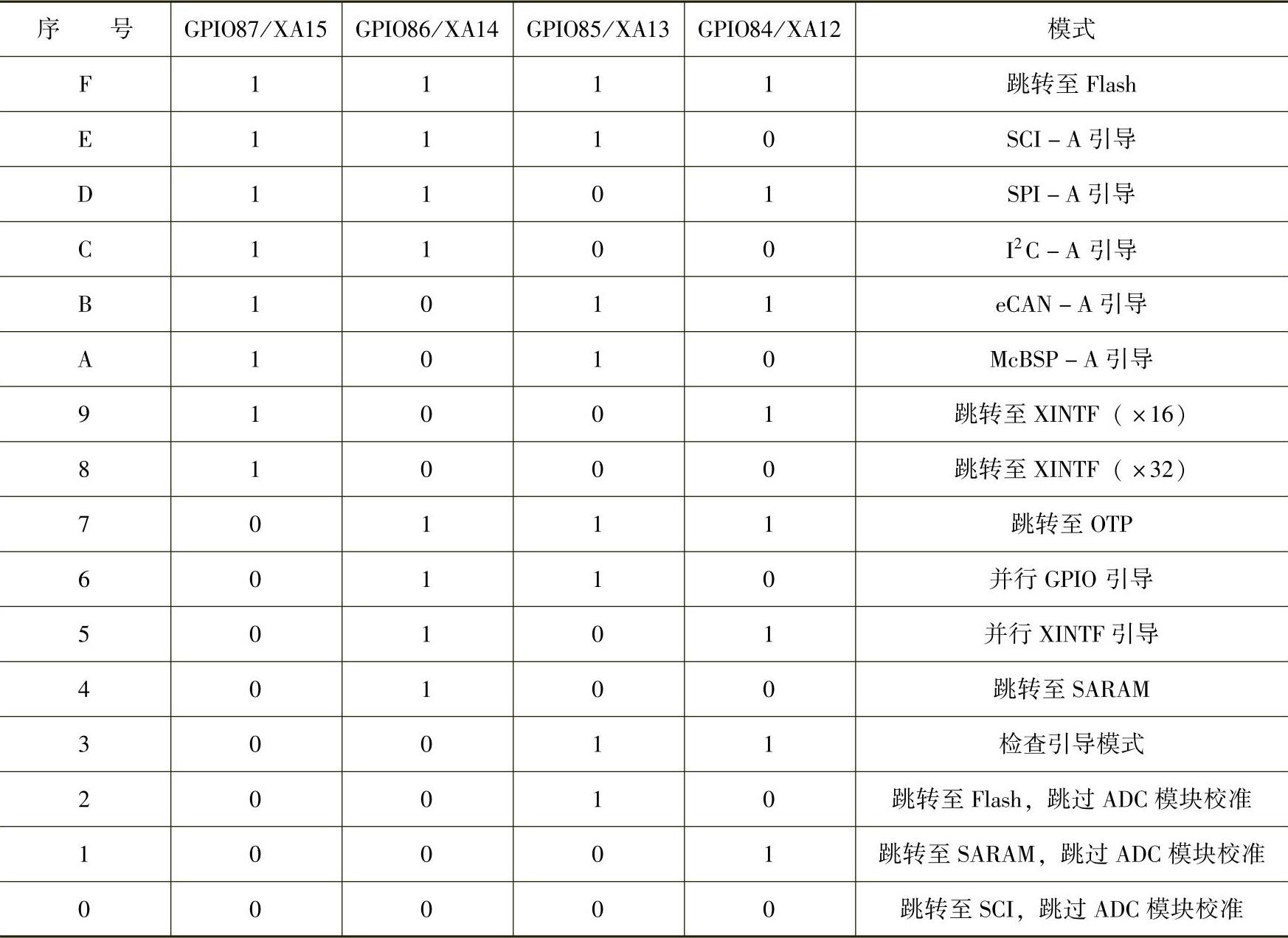

9.Boot ROM

Boot ROM是出厂时的引导程序。在上电时,引导模式信号提供给boot-loader软件,用以决定使用何种引导模式。用户可以选择通常的引导模式或者从外部连接下载新程序,抑或选择内部的Flash/ROM引导程序。Boot ROM还包含有标准的表,比如SIN/COS波形表。具体的引导模式选择见表2-7。

表2-7 引导模式选择

需要注意的是,模式0、1、2仅为TI测试用,跳过ADC模块校准可能会导致ADC模块非正常工作。

10.安全性

F2833x提供高级别的保密性,以保护用户程序不被反编译。安全功能提供了128位的密码(硬件设定16个等待周期)用于用户的Flash程序保护。代码安全模块(CSM)用来保护Flash/OTP和L0/L1/L2/L3 SARAM上的代码,安全功能将阻止未授权的用户使用JTAG口查看存储器的内容,或从外部存储器执行代码,亦或试图使用不期望的软件导出存储器内容。在对安全模块进行访问时,用户需要正确输入与存储在Flash密码区域相匹配的128位密匙值。

除了CSM,仿真代码安全逻辑(ECSL)模块用来阻止未授权用户跳过安全码。当仿真器被连接上时,任何对Flash、用户OTP、L0、L1、L2和L3存储器的代码或数据访问都将会触发ECSL,并断开仿真连接。为使在CSM保护下对安全码进行仿真,用户必须写入正确的值到KEY寄存器的低64位,该值应与存储在Flash内低64位的密码相匹配。要注意的是对Flash内128位密码的读取仍然必须执行。如果密码的低64位都为1(未编程),那么KEY值不需要相匹配。

当调试在Flash设置了密码的设备时,仿真器会用一些时间来控制CPU。在此期间,CPU将开始运行,并执行一条访问ECSL保护区域的指令。如果执行了此指令,ECSL将触发并且引起仿真连接断开。解决该问题的两个方法是:

●使用复位中等待的仿真模式,这将使器件保持在复位模式直至被仿真器控制。仿真器需要支持这种模式。

●选择“检查引导模式”的启动方式,这将使器件持续处于检查启动模式控制引脚的状态。用户可以选择这种模式,并且在仿真器连接到设备后,通过修改PC指针指向

另一地址,或者通过修改启动模式选择引脚的状态,而退出该引导模式。

128位密码(0x33FFF8~0x33FFFF)不能够全部编程为0,否则将永久锁住芯片。

11.外设中断扩展(PIE)

F2833x外设中断扩展单元(PIE)支持多达96个中断,其中有58个是用于外设的。96个中断以8个为一组进行分组,每组都连接到CPU中断线上(INT1~INT12)。每个中断所对应的中断向量表存储在RAM模块中,并且用户可以根据需要对其进行修改。CPU响应中断时,会自动获取中断向量。中断的优先级可以通过硬件和软件进行控制,并且每个中断也能独立使能或禁止。

12.外部中断(XIN1~XINT7,XNMI)

F2833x支持8个可屏蔽的外部中断(XINT1~XINT7,XNMI)。XNMI可以被连接到CPU的INT13或NMI中断上。每个中断可以选择为下降沿触发、上升沿触发或下降沿及上升沿触发,也可以使能或禁止(包括XNMI)。XINT1、XINT2和XNMI也包含一个16位的增计数器,当检测到有效边沿时计数器复位至0。该计数器可以用来准确记录中断时间。与281x系列器件不同,并没有为外部中断限定引脚,例如,XINT1、XINT2和XNMI中断可以接收来自GPIO0~GPIO31引脚的输入,XINT3~XINT7中断可以接收来自GPIO32~GPIO63引脚的输入。

13.振荡器和PLL

F2833x可以由外部振荡器或连接在片上的晶振电路提供时钟。而片上的PLL可以实现高达10倍的倍频。PLL倍频系数可通过软件修改,并且PLL模块可以被设置成旁路模式。

14.看门狗

F2833x包含一个看门狗定时器。用户软件必须定时复位看门狗计数器。否则,看门狗将对处理器产生复位信号。看门狗模块也可以被禁用。

15.外设时钟

每个外设的时钟都可以独立地使能/禁止,所以当某一外设不使用时,可以禁止其时钟,以减少系统功耗。此外,串行口(除了I2C和eCAN)和ADC模块的时钟可以通过对CPU时钟进行编程分频得到。

16.低功耗模式

F2833x为全静态CMOS器件,支持3种低功耗模式:(https://www.xing528.com)

●空闲模式(IDLE)。将CPU置于低功耗模式,外设时钟有选择地被关闭,只有在IDLE模式下需要工作的外设才继续工作。一个有效的外设使能中断或看门狗定时器可将处理器从IDLE模式唤醒。

●等待模式(STANDBY)。关闭CPU和外设的时钟。该模式只留下振荡器和PLL工作。外部中断事件将唤醒处理器和外设。检测到中断事件后,在下一个有效周期将开始执行指令。

●暂停模式(HALT)。关闭内部的振荡器,该模式基本关闭了整个芯片,使设备处于尽可能低的功率消耗模式。复位或外部信号可以将器件从该模式唤醒。

17.外设帧0、1、2、3(PFn)

F2833x把外设分成4部分,外设的映射如下:

(1)PF0

PIE:PIE中断使能、控制寄存器及PIE向量表。

Flash:Flash等待状态寄存器。

XINTF:外部接口寄存器。

DMA:DMA寄存器。

定时器:CPU定时器0、1、2寄存器。

CSM:代码安全模块密匙寄存器。

ADC:ADC模块结果寄存器(双映射)。

(2)PF1

eCAN:eCAN邮箱和控制寄存器。

GPIO:GPIO复用配置和控制寄存器。

ePWM:增强型脉宽调制模块和寄存器(双映射)。

eCAP:增强型捕获模块和寄存器。

eQEP:增强型正交编码器脉冲模块和寄存器。

(3)PF2

SYS:系统控制寄存器。

SCI:串行通信接口(SCI)控制和RX/TX寄存器。

SPI:串行外设接口(SPI)控制和RX/TX寄存器。

ADC:ADC模块状态、控制和结果寄存器。

I2C:内部集成电路模块(I2C)和寄存器。

XINT:外部中断寄存器。

(4)PF3

McBSP:多通道缓冲串行端口寄存器。

ePWM:增强型脉宽调制模块和寄存器(双映射)。

18.GPIO

大多外设信号与通用输入/输出(GPIO)信号复用。若引脚未作为外设信号或外设功能使用,则用户可将该引脚作为通用I/O使用。复位时,GPIO引脚被配置成输入。每个引脚都可以独立配置为GPIO模式或者是外设信号模式。对于特定的输入,用户也可以选择输入限定周期的个数,以便滤除噪声。GPIO信号也可以将器件从低功耗模式中唤醒。

19.32位CPU定时器(0、1、2)

CPU定时器0、1、2是可预置时间周期的32位定时器,其具有16位的时钟分频。定时器有一个32位的减计数寄存器,计数器按照分频器设置的CPU时钟递减计数。当计数器计到0时会产生中断,并自动地重载32位的周期值。CPU定时器2被保留用于实时操作系统或BIOS应用,它与CPU的INT14相连。如果未使用DSP/BIOS,CPU定时器2可作为普通定时器使用。CPU定时器1作为普通定时器使用,并连接到CPU的INT13。CPU定时器0也用作通用功能,并连接到CPU的PIE模块。

20.控制外设

F2833x包含以下用于嵌入式控制和通讯的外部设备:

●ePWM。增强型PWM外设,支持独立的/互补的PWM输出、前导/结束边沿可调节的死区输出、锁存/逐周期触发机制。一些PWM引脚支持HRPWM功能。支持DMA。

●eCAP。增强型捕获外设,使用32位的时基,有多达4个可编程事件,支持连续/单次捕获模式。这一外设也可以配置产生辅助的PWM信号。

●eQEP。增强型QEP外设,使用32位的位置计数器。它支持使用捕获单元的低速测量和使用32位单位定时器的高速测量。该外设有一个看门狗定时器,用来检测电动机停转和输入错误逻辑(以识别QEP信号是否存在同时发生边沿跳变的情况)。

●ADC。ADC模块是一个12位、单端、包含16通道的转换模块。它为同步采样提供两个采样保持单元。支持DMA。

21.串行端口

F2833x包含以下串行通信外设:

●eCAN。这是CAN外设的增强版本。它支持32个邮箱、消息的时间标记功能以及CAN2.0B标准。

●McBSP。多通道缓冲串行口(McBSP)连接到E1/T1线上,用来与调制解调中的编码器或音频DAC设备通信。支持DMA。可配置为SPI功能。

●SPI。SPI是高速同步串行I/O口,可以使数据流(数据长度1~16位)按可编程的传输速率移入或移出器件。SPI通常用于DSC和外设或另一处理器之间通信。SPI支持主/从形式的多机通信。在2833x/2823x系列DSP上,SPI包含16级深的接收和发送FIFO。

●SCI。串行通信接口(SCI)是一个两线制异步串行接口,通常被称为UART。SCI包含16级深的接收和发送FIFO。

●I2C。I2C模块提供了DSC与其他兼容I2C总线2.1版本器件的通信接口。通过I2C模块,外部器件和DSC间数据的发送/接收可达到8位。在2833x/2823x系列DSP上,I2C包含16级深的接收和发送FIFO。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。