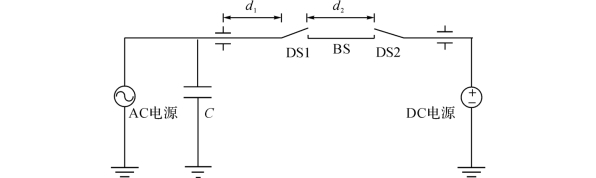

GB1985-2004《高压交流隔离开关和接地开关》和IEC标准60129中提出了用于考核隔离开关性能的试验回路,如图7-39所示[28]。

图7-39 GB1985和IEC标准规定的隔离开关试验回路

图7-39中,AC电源为电源侧交流电源,DC电源为负载侧直流电源,主要用于给负载侧短母线BS充电以产生残压,C为电源侧回路的集中电容,DS1为试验中被试隔离开关,DS2为辅助隔离开关,主要用于控制对负载侧空载短母线BS充电,d1表示电源侧GIS套管与隔离开关DS1之间的长度,d2表示被试隔离开关与辅助隔离开关之间的长度。

试验时,首先合上DS2,直流电源DC通过DS2对短母线BS充电,带电后的短母线BS可用来模拟隔离开关分闸操作后具有残压的短母线,然后通过合分操作DS1产生VFTO用于试验研究。

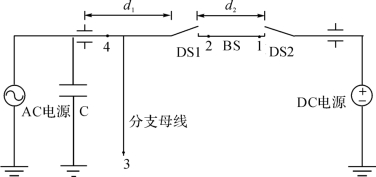

VFTO的试验回路应能够尽量广泛地代表大多数接线方式,并且能够模拟出可能产生较大VFTO幅值的情形。根据对特高压变电站的仿真研究结果,并结合图7-39,我国提出了带有分支母线的试验回路,如图7-40所示[28]。

(https://www.xing528.com)

(https://www.xing528.com)

图7-40 我国的特高压VFTO试验回路

图中,数字1~4表示VFTO的测量点。

图中的试验回路与图7-39相比,在电源侧多加装了一条分支母线,当操作隔离开关DS1时,产生的VFTO波在分支母线末端发生全反射,此时可能会产生较为严重的VFTO。因此,相比于图7-39中所示的试验回路,采用图7-40中的试验回路可能会产生更为严重的VFTO。

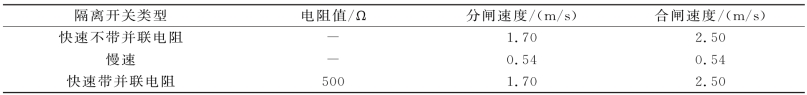

另外,隔离开关有快速隔离开关和慢速隔离开关两种类型:一种是快速隔离开关,由河南平高电气股份有限公司(简称平高)生产,该隔离开关可加装并联电阻;一种是慢速隔离开关,由西安西电开关电气有限公司(简称西电)生产。两种隔离开关的技术参数如表7-13所示[29]。

表7-13 两种隔离开关技术参数

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。