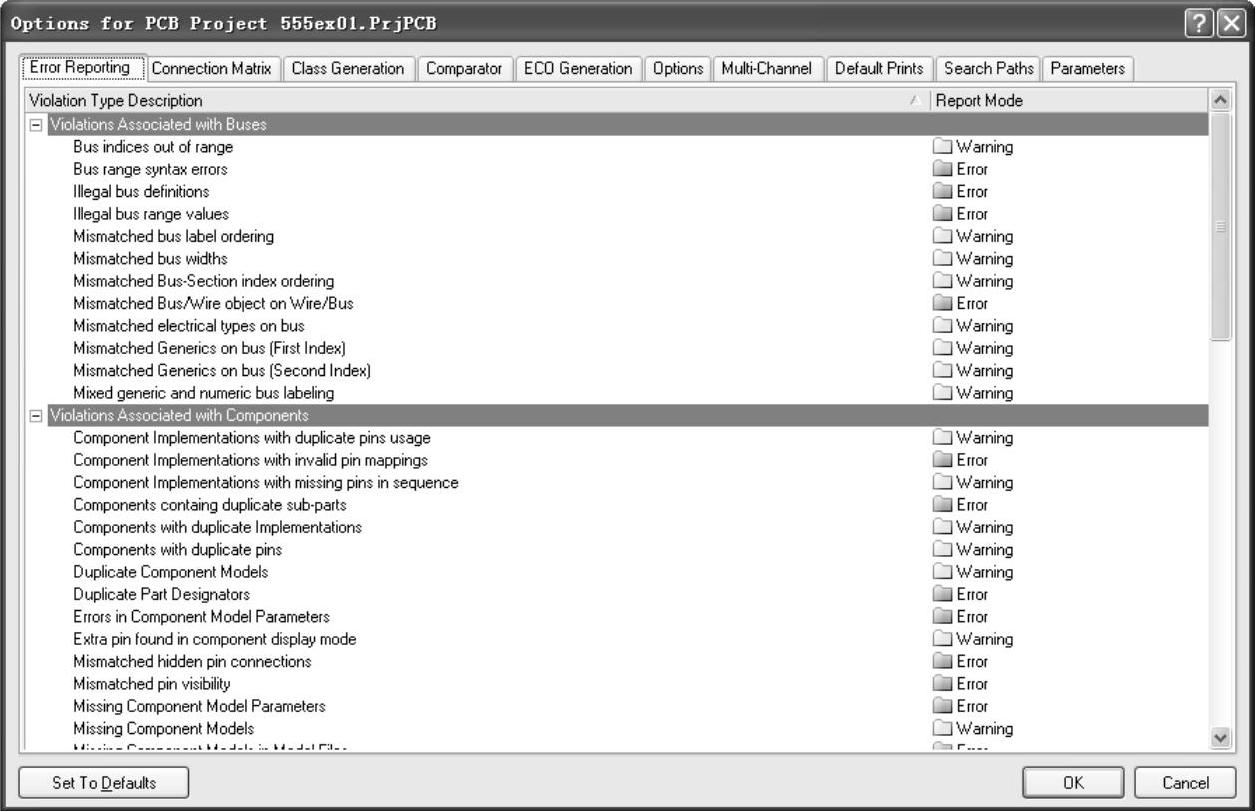

在对原理图进行ERC之前应进行ERC规则设置。对ERC规则进行的设置在“Options for PCB Project”对话框中实现,选择“Project”→“Project Options”命令,将弹出如图5-9所示的对话框。该对话框主要包括10个选项卡,其中涉及电路原理图检查的有Error Reporting(错误报告)和Connection Matrix(连接矩阵)两个选项卡。下面对这两个选项卡中的相应设置进行简要介绍。

图5-9 “Error Reporting”选项卡

1.Error Reporting选项卡

该选项卡主要用于设置电路原理图电气规则的测试项目。其中包含6种错误类型。下面就这些错误类型中常见的几种类型加以说明。

(1)Violations Associated with Buses类

● Bus indices out of range:总线分支索引超出范围。总线分支的索引超出总线的索引范

围时就违反了该规则。

● Bus range syntax errors:总线范围的语法错误。如果总线的命名违反总线的命名规

则,则违反了该规则。

● Illegal bus definitions:定义总线非法。如果总线没有通过总线入口就直接与元器件引

脚相连,则违反了该规则。

● Illegal bus range values:总线范围值非法。总线范围值应与它所连接的分支数相等,

如果不相等,则违反了该规则。

● Mismatched bus lable ordering:总线分支的网络标号排列错误。通常总线分支的网络

标号是按升序或降序排列的,否则就违反了该规则。

● Mismatched bus widths:总线的宽度错误。总线的范围值应与它连接的分支数相等,

否则就违反了该规则。

● Mismatched bus section index ordering:总线范围值表达错误。

● Mismatched electrical types on bus:总线上电气类型错误。

● Mismatched Generics on bus(First Index):总线范围值的首位错误。

● Mismatched Generics on bus(Second Index):总线范围值的末位错误。

● Mismatched generic and numeric bus labeling:总线命名错误。如,采用了数字与符号

的混合编号。

(2)Violations Associated with Components类

● Component Implementations with duplicate pins usage:元器件引脚在原理图中重复使用。

● Component Implementations with Invalid pins mappings:元器件引脚和PCB封装不符。

● Component Implementations with missing pins in sequence:元器件引脚中出现序号丢失。

● Component contaning duplicate sub-parts:元器件中出现了重复的子部分。

● Component with duplicate Implementations:元器件被重复利用。

● Component with duplicate Implementations:元器件有重复的引脚。

● Duplicate Component Models:一个元器件定义有多个模型。

● Duplicate Pat Designator:元器件中出现标号重复现象。

● Sheet symbol with duplicate entries:电路方块图中出现重复端口。

● Unused sub-part in component:元器件中的某个部分未被使用。

(3)Violations Associated with Documents类

● Duplicate Sheet Numbers:重复的原理图序号。

● Duplicate Sheet symbol Names:层次原理图中使用了重复的电路方块图。(https://www.xing528.com)

● Missing child sheet for sheet symbol:电路方块图没有与之对应的子电路图。

● Port not linked to parent sheet symbol:子原理图的端口未与母原理图中电路方块图的

端口相对应。

● Sheet Entry not linked to child sheet:电路方块图的端口未与子原理图的端口相对应。

(4)Violations Associated with Nets类

● Adding hidden net to sheet:原理图中出现隐藏网格。

● Duplicate Nets:原理图中出现重名网格。

● Global Power-Object scope changes:总体电源符号错误。

● Net parameters with no name:网络属性中没有名称。

● Net parameters with no value:网络属性中没有赋值。

● Nets containing floating input pins:网络中包含悬空的引脚。

● Nets containing multiple similar objects:网络中包含多个类似对象。

● Nets with no driving source:网络中没有驱动电源。

● Sheet containing duplicate ports:原理图中包含重复的端口。

● Unconnected objects in net:网络中出现元器件未连接对象。

● Unconnected wires:原理图中出现未连接的导线。

(5)Violations Associated with Others类

● Objects not completely within sheet boundaries:原理图中的元器件超出了图纸的边框。

● Off-grid object(0.05grid):原理图中的元器件未能处于格点位置。

(6)Violations Associated with Parameters类

● Same parameters containing different types:相同参数出现在不同的模型中。

● Same parameters containing different values:相同参数出现不同的取值。

(7)“Report Mode”栏

在“Report Mode”栏中包含4种错误等级。

● No Report:检查出错误不报告(用绿色标志)。

● Warning:检查出错误以警告形式报告(用黄色标志)。

● Error:检查出错误以错误形式报告(用橙色标志)。

● Fatal Error:检查出错误以严重错误形式报告(用红色标志)。

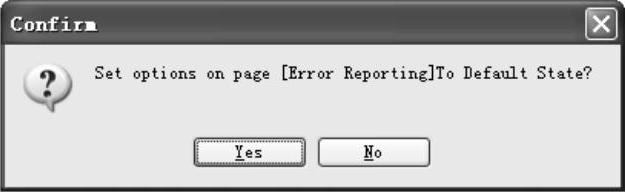

电路原理图ERC设置一般采用系统默认值,单击 按钮,将弹出如图5-10所示的对话框,再单击

按钮,将弹出如图5-10所示的对话框,再单击 按钮,可将ERC设置为默认值。

按钮,可将ERC设置为默认值。

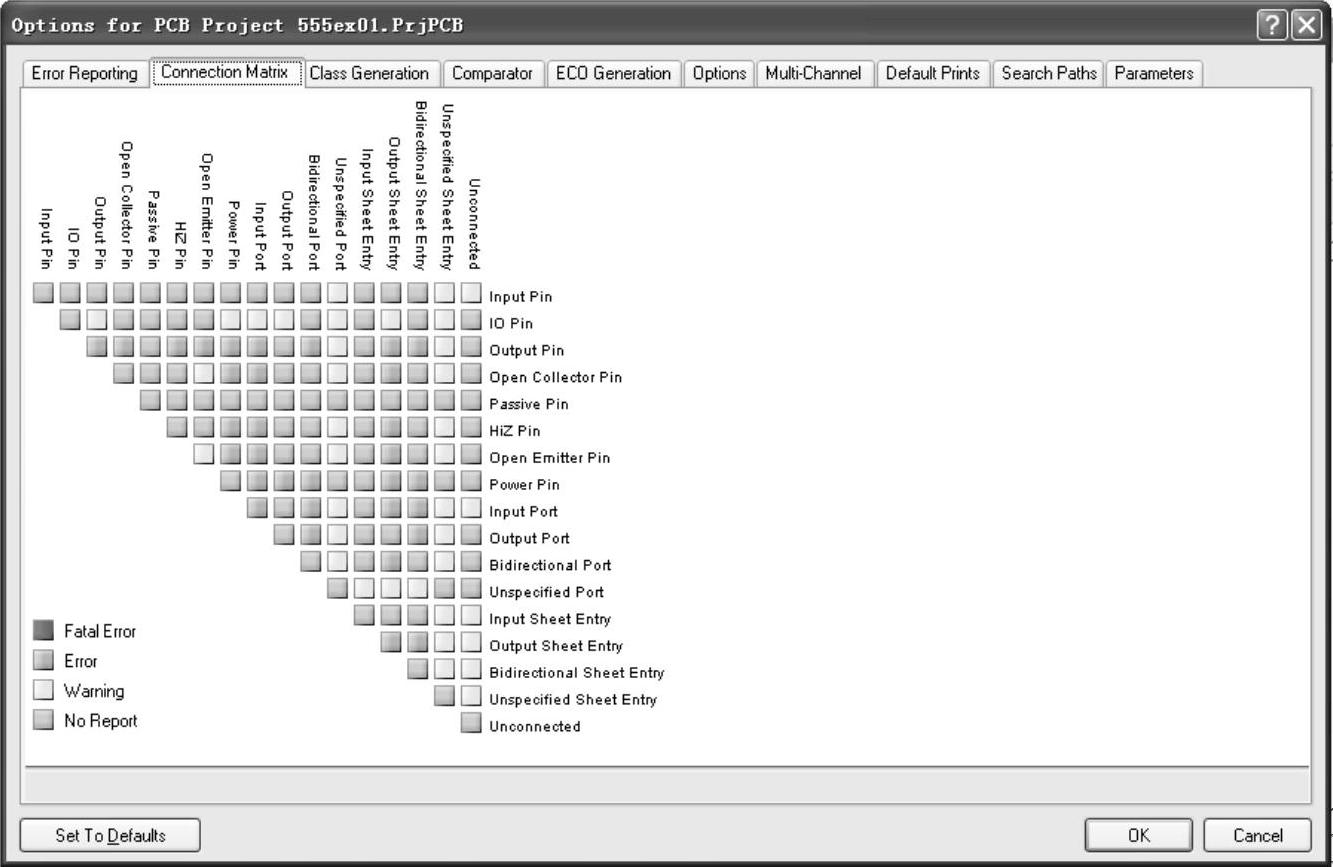

2.Connection Matrix(连接矩阵)选项卡

该选项卡主要用于检测各种引脚、I/O端口、电路方块图的出/入端口的连接是否已构成了Warning(警告)或Error(错误)等级别的电气冲突,如图5-11所示。

图5-10 是否设置为默认值对话框

图5-11 “Connection Matrix”选项卡

在该矩阵的行、列中都列出了电路图中所有端口与引脚的类型,每一行与列的交点就是该电气节点的状态。通过查看小方块的颜色可以得知电气节点的状态。在该选项卡中,用户通过改变的颜色可以进行各种错误等级的设置,单击即可改变色块的颜色,各颜色代表的错误等级在左下角标出。对于大多数原理图设计保持默认设置即可,但对于特殊原理图的设计,用户则需要进行必要的改动。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。