1.三个钮子开关控制一个灯的逻辑

要求是,有三处安装有钮子开关。任何一处均可改变灯的状态。如灯亮,可使其灭;反之,可使其亮。

(1)设计真值表。设3个开关分别用A、B及C表示。灯用L表示。每个开关都有两个状态,即下扳、上扳。下扳时用变量本身,即用A、B或C表示。上扳时用变量的非,即用A、B及C表示。

这3个变量各有两个取值,其可能的组合有8种。把这8种分成两组,奇数个下扳的一组,有4个;偶数个下扳的另一组,也有4个。显然,任何一个开关状态的改变,都将组合从一组改变到另一组。如果用其中一个组合使灯亮,另一个组合使灯灭,即可实现所要求的控制了。

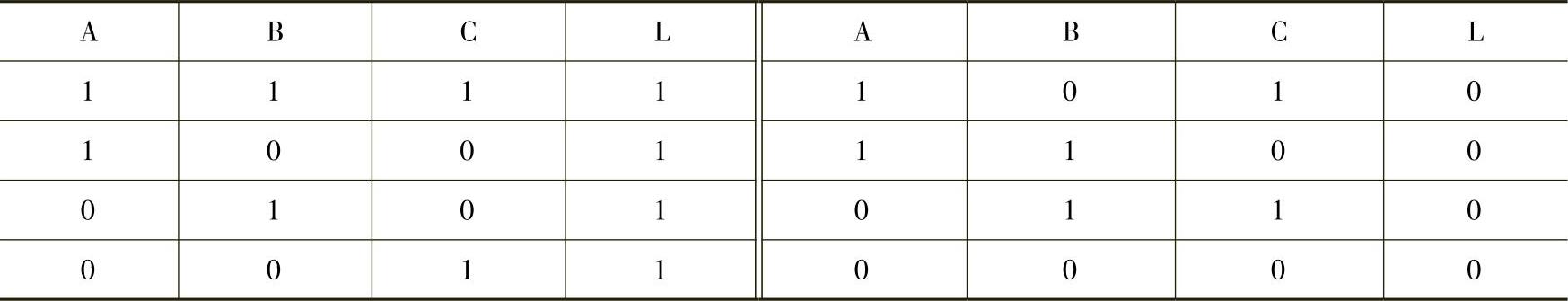

对此分析,可用真值表表示。见表3-4。

表3-4 一灯多控制真值表

提示:这里A=0意味着 ,B=0意味着

,B=0意味着 ,C=0意味着

,C=0意味着 。故在表中,变量非均不必列出。

。故在表中,变量非均不必列出。

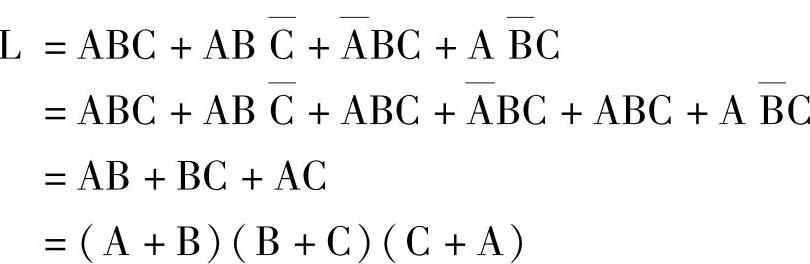

(2)列写表达式。

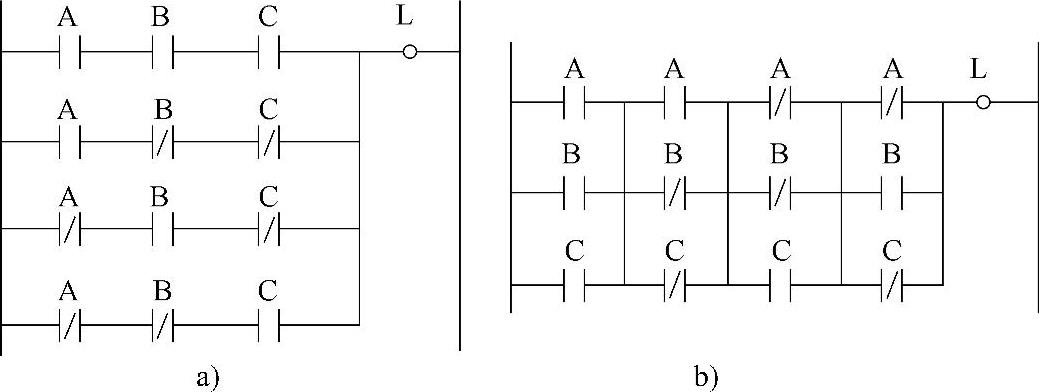

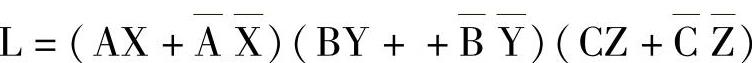

图3-21 三个钮子开关控制一个灯电路

a)合取范式 b)析取范式

当然还应对这个表达式进行化简。不过由于使用PLC,触点多少问题不大,可直接依据此表达式,画出的梯形图,如图3-21所示。图3-21a为其合取范式,即先串、后并。图3-21b为其析取范式,即先并、后串并。

这里仅用3个开关管理一个灯。如果多了,如几十、几百,就太复杂了。为此可用后面将要介绍的高级逻辑设计方法设计。

2.多开关表决逻辑

本例用3个开关,2个赞成,表示通过。

(1)设计真值表。3个开关分别用A、B及C表示。表决结果用灯L表示。每个开关都有两个状态,即下扳(赞成)、上扳(不赞成)。下扳时用变量本身,即A、B或C表示。上扳时用变量的非,即A 、

、 及

及 表示。这3个变量各有两个取值,下扳的是两个及两个以上的有4种。把这4种组合使灯亮,其它组合使灯灭,即可实现所要求的控制了。

表示。这3个变量各有两个取值,下扳的是两个及两个以上的有4种。把这4种组合使灯亮,其它组合使灯灭,即可实现所要求的控制了。

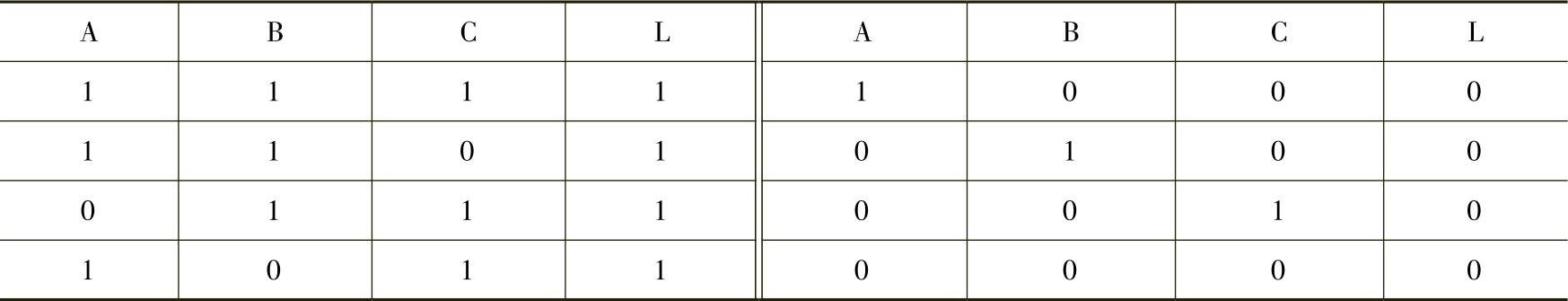

对此分析,可用真值表表示,见表3-5。

表3-5 表决控制真值表

提示:这里A=0意味着 ,B=0意味着

,B=0意味着 ,C=0意味着

,C=0意味着 。故在表中,变量非均不必列出。

。故在表中,变量非均不必列出。

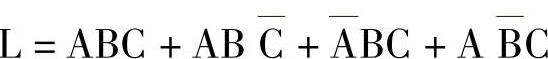

(2)列写表达式。

经化简则为

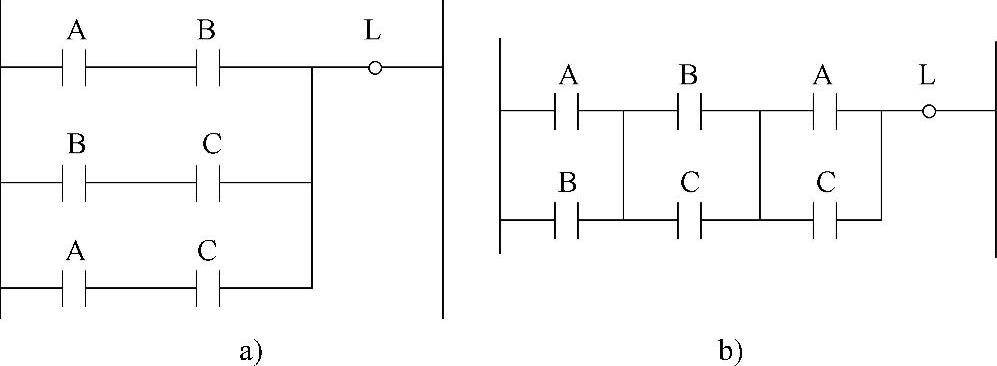

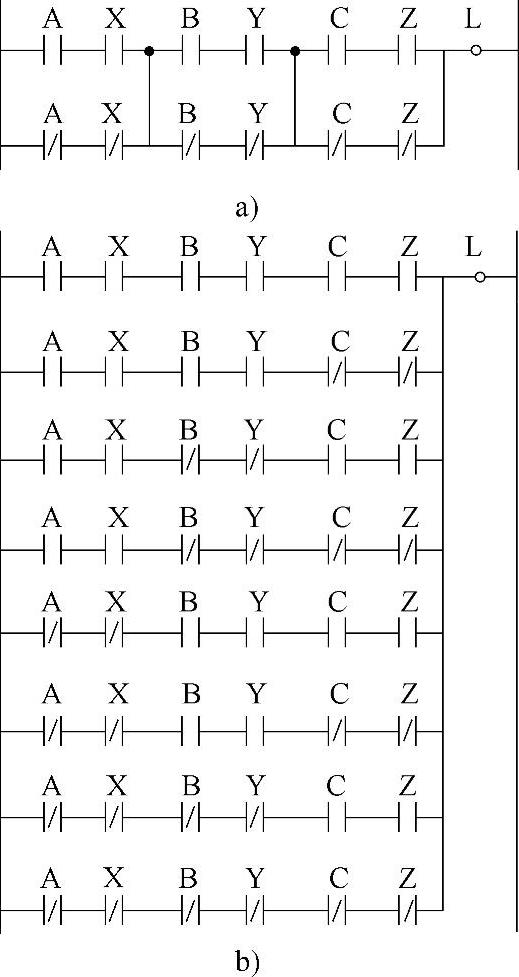

当然还应对这个表达式进行化简。不过由于使用PLC,触点多少问题不大,可直接依据此表达式,画出的梯形图,如图3-22所示。图3-22a为其合取范式。图3-22b为其析取范式。这个电路在以上讨论等效输出时也见过。只是那里用了直接地址。

图3-22 三个开关表决电路

a)合取范式 b)析取范式

这里仅用3个开关表决。如果多了,如几十、几百,就太复杂了。为此可用后面将要介绍的高级逻辑设计方法设计。

3.比较逻辑

比较甲、乙两组开关上扳、或下扳是否一致。这里假设每组有3个开关。

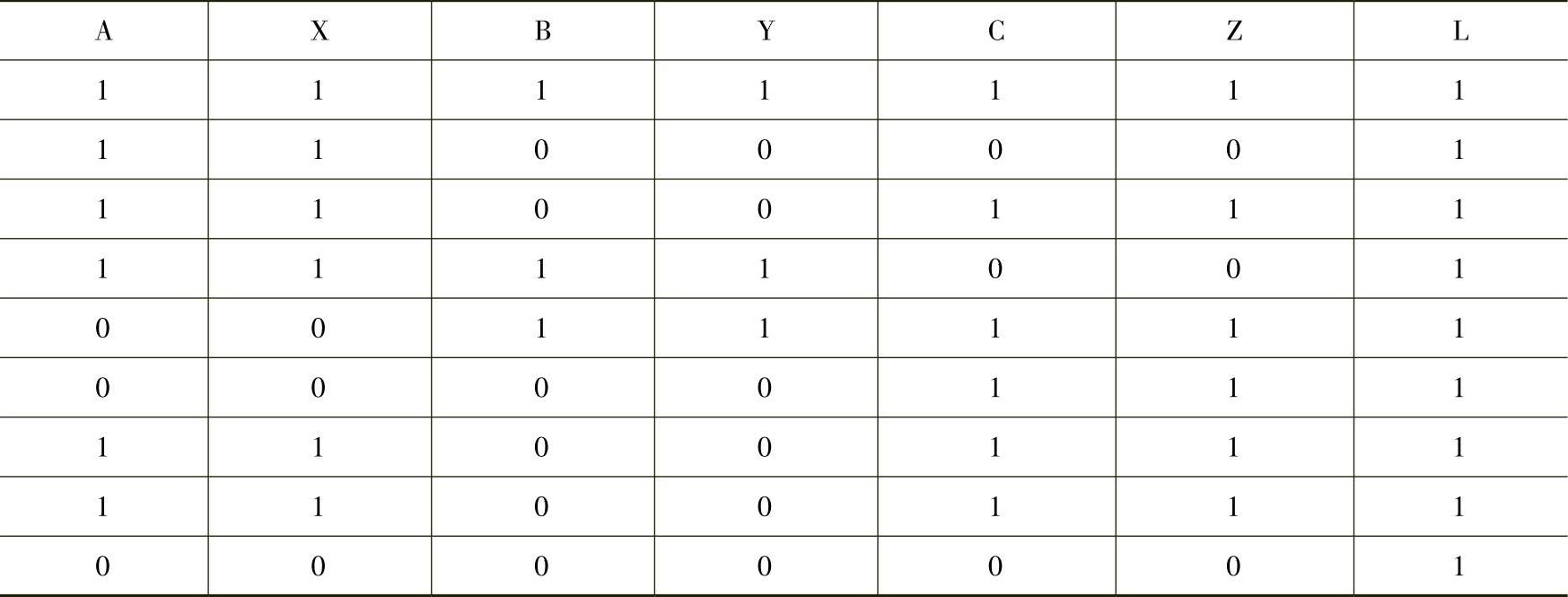

(1)设计真值表。甲组的3个开关分别用A、B及C表示,乙组与甲组对应的3个开关分别用X、Y及Z表示。比较相同结果用灯L表示。每个开关也都有两个状态,即下扳、上扳。下扳时用变量本身表示。上扳时用变量的非表示。

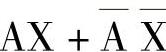

这3个变量各有两个取值。以A与X为例,如比较一致,要不都是上扳,要不都是下扳。即: 。

。

而只有3对比较都一致,才说明这两组开关一致。以上分析见表3-6。(https://www.xing528.com)

表3-6 比较控制真值表

提示:这里A=0意味着 ,B=0意味着

,B=0意味着 ,C=0意味着

,C=0意味着 。X、Y、Z也类似。故在表中,变量非均不必列出。

。X、Y、Z也类似。故在表中,变量非均不必列出。

(2)列写表达式。

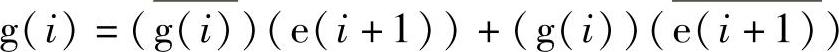

当然还应对这个表达式进行化简。不过由于使用PLC,触点多少问题不大,可直接依据此表达式,画出的梯形图,如图3-23所示。图3-23a为其析取范式。图3-23b为其合取范式。这里变量声明略。

这里仅用两组3个开关比较。如果多了,如几十、几百,就太复杂了。为此可用字节、字或双字比较指令了。

图3-23 3开关比较逻辑

a)析取范式 b)合取范式

4.格兰码到二进制码译码

格兰码为单位码,不少绝对值计数的旋转编码器用它编码。但格兰码没有“权值”,无法用作大小比较。但它与二进制码有对应关系,其关系真值表见表3-7(5位)。以此关系,可把它译成二进制码。

从表3-7可知,二进制码的本位的值为:格兰码的本位值与二进制码高一位值的异或,即:

这里e(i)为第i位二进制值;

g(i)为第i位格兰码值;

表3-7 二进制码与格兰码对照真值表

e(i+1)为第i+1位二进制值。

而最高位两者相等。

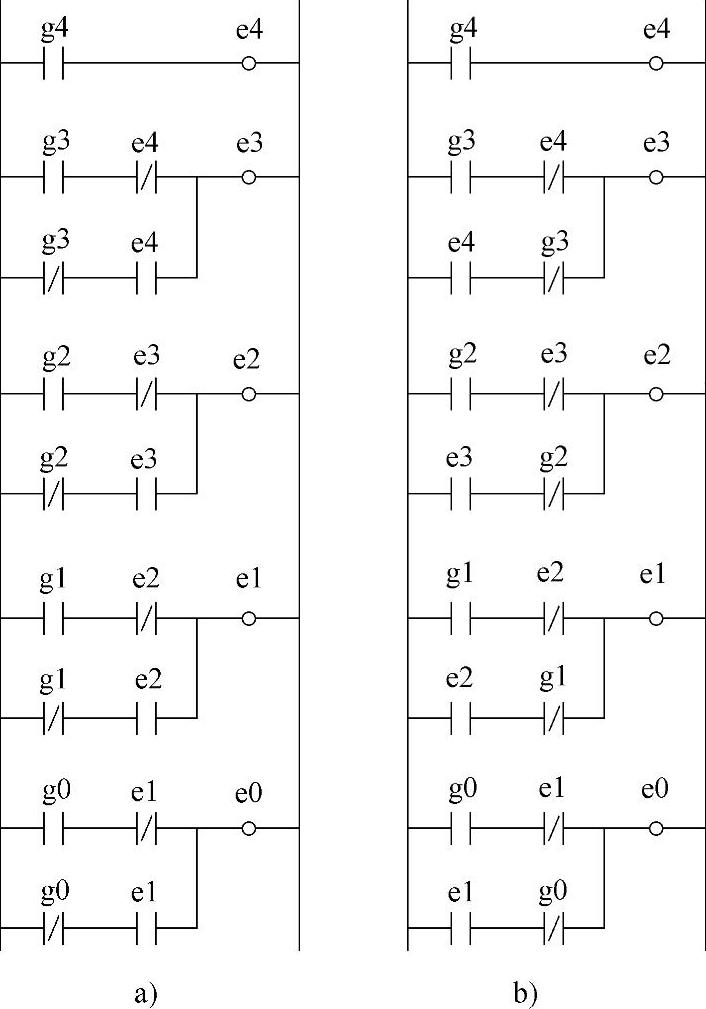

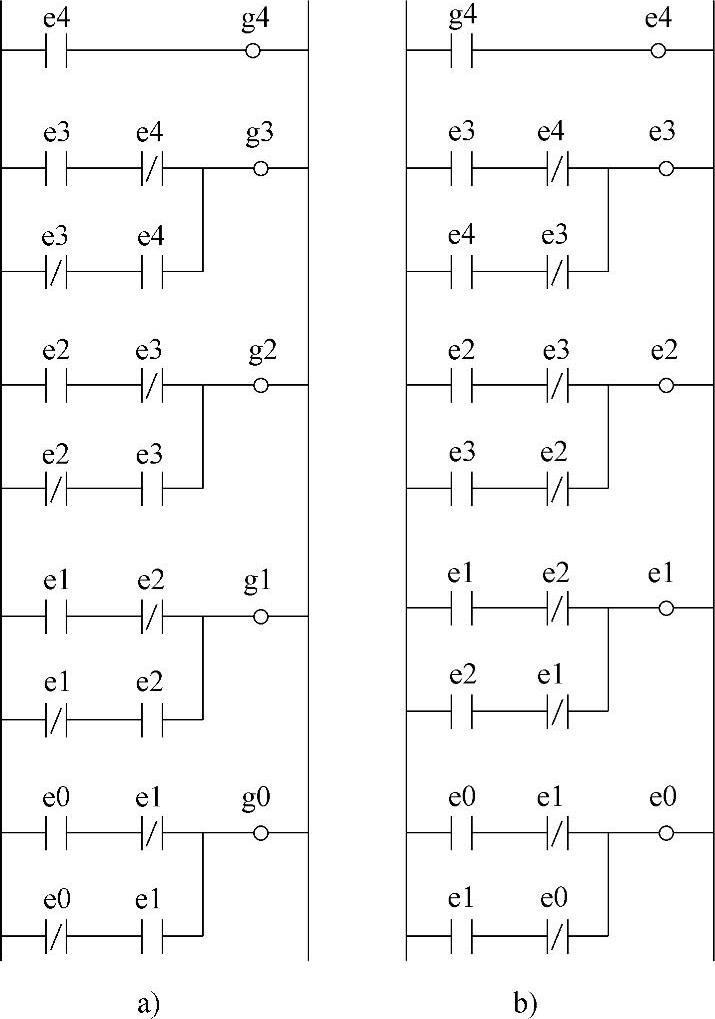

图3-24即为此译码程序。图3-24a为其合取范式。图3-24b为其析取范式。该图g0(低位)到g4(高位)为格兰码,e0(低位)到e4(高位)二进制码。

5.二进制码到格兰码译码

从表7-5中可知,格兰码本位的值为二进制码的高一位值与二进制码的本位值的异或,即:

这里e(i)为第i位二进制值;

e(i+1)为第i+1位二进制值;

g(i)为第i位格兰码值。

而最高位两者相等。

如图3-25所示的为二进制到格兰码的译码程序,图3-25a为其合取范式,图3-25b为其析取范式。该图g0(低位)到g4(高位)为格兰码,e0(低位)到e4(高位)为二进制码。

图3-24 格兰码到二进制译码程序

a)合取范式 b)析取范式

图3-25 二进制到格兰码译码程序

a)合取范式 b)析取范式

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。