1.硬件电路的总体结构和工作流程

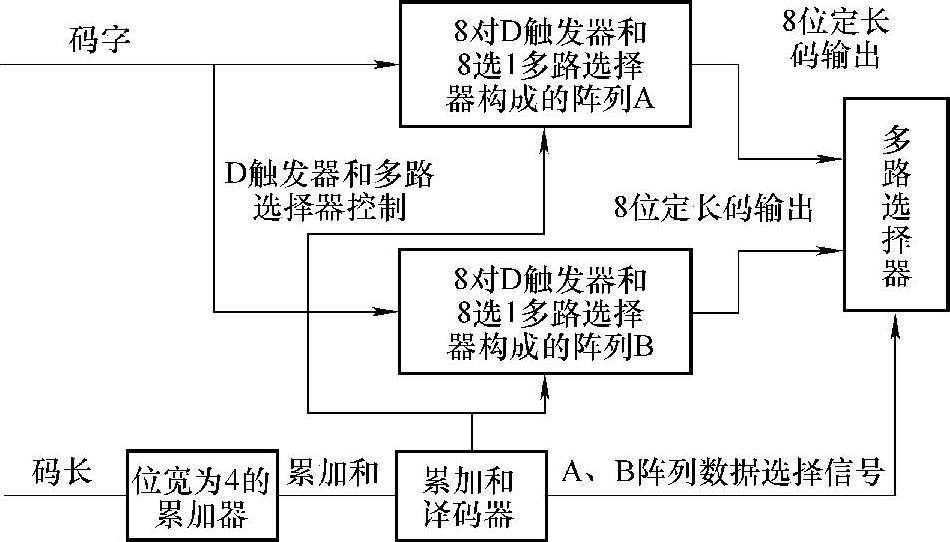

霍夫曼编码压缩方式下硬件电路的结构如图8-27所示。图中的粗箭头代表数据信号,细箭头代表控制、状态标志及地址信号。

图8-27 硬件电路结构

XILINX公司FPGA中的双端口RAM可以同时进行读写操作,但同时写入或读取同一地址会发生错误。其结构图如图8-28所示。

控制单元负责所有的RAM读写操作及各单元的协同,其功能由相应的状态机实现。系统工作时,双端口RAM作为乒乓式缓冲,数据首先存储于RAM的上半区,存满后,在数据存入下半区的同时,由于上下半区RAM的端口是独立的,控制单元开始读取上半区中的数据到差分计算单元和动态范围计算单元。控制器按行顺序读取RAM并设置读取计数器,每读完一行后行使首列数据读取信号有效。差分计算单元内设置3个寄存器,分别保存行首值、前值和现值。差分单元复位后,输出首行数据的首值和其后的各个差分值,在首列数据读取信号有效时,输出为两个相邻首列值的差分。得到的差分数据存于RAM3中。在输出差分值的同时,差分计算单元还判断差分值是否大于差分重要性阈值,如果有大于阈值的差分值,就设置差分重要信号有效。动态范围计算单元内也设置3个寄存器,分别保存每行数据的最大值、最小值和动态范围,当首列数据读取信号有效时,复位3个寄存器为零。动态范围重要性的判断流程与差分重要性的判断流程一致。当RAM3存满后,控制器开始读取RAM3中的数据,并使能霍夫曼编码单元和变长码凑整存储单元,这两个单元是电路的核心部分。

图8-28 FPGA中的双端口RAM

2.霍夫曼编码单元和变长码凑整存储单元(https://www.xing528.com)

霍夫曼编码单元的功能是根据输入差分值的范围,输出对应的编码。编码分为两个部分:幅度码和附加码。每读取一次数据,编码单元需要完成两次输出操作。由于霍夫曼编码单元输出为非定长码,因此需要从8位输出的数据中去处冗余的部分,把有效码字拼接成定长码字输出,才能最终达到压缩的效果。采用变长的拼接电路结构完成这一功能,如图8-29所示。

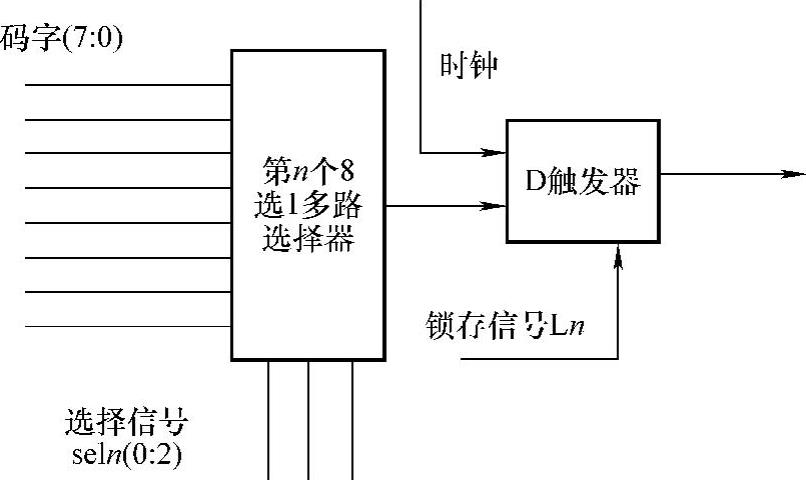

电路中累加器对码长求和,其输出由累加和译码器译码,生成D触发器与8选1多路选择器的锁存信号Ln和选择信号Seln(0∶2)。当累加结果大于或等于8时,多路选择输出阵列A或B中的定长字。D触发器与8选1多路选择器对的结构如图8-30所示。阵列A和B各由8对图8-30所示的D触发器与8选1多路选择器对构成,D触发器暂存码字某一特定位。累加和译码器模块对累加器的输出进行译码,其输出接到阵列A和B中16个8选1多路选择器的选择信号端、D触发器的锁存信号端以及多路选择器的选择信号端。多路选择器模块由8个2选1的多路选择器构成。当累加器中的码长和大于或等于8时,该多路选择器输出阵列A或B中的定长字。

图8-29 变长码拼接电路结构

图8-30 D触发器与8选1多路选择器对的结构

电路工作原理为:时钟发生有效跳变,累加器读入码长,并与原有数据累加。若累加器第4位由“0”跳变为“1”,则多路选择器将在下个周期输出阵列A的定长字;由“1”跳变为“0”,则输出阵列B的定长字;若没有跳变,不产生输出,阵列A、B读入码字。累加器中原有数据由累加和译码器译码,产生阵列A、B中相应D触发器的锁存信号Ln和8选1多路选择器的选择信号Seln(0∶2),这两个信号把码字的全部8位存入D触发器,为下一个周期做好数据准备。

对4位累加器的输出进行解释的累加和译码器,是整个电路的控制核心。它有4位输入,64位输出,其中16位输出L0~L16,控制D触发器的锁存;其他48位Sel0(0∶2)~Sel15(0∶2)控制16个8选1多路选择器。其功能的实现方法如下:当累加器为C时,说明阵列A或B的前C位D[7∶7-C+1]已是有效码字,当连接下个码字时,这些位的锁存信号为无效态,其他位允许锁存;此时第C+1个8选1多路选择器输出当前码字最高位,存储在第C+1个D触发器中,第C+2个8选1多路选择器输出码字次高位,存储在第C+2个D触发器中,余下以此类推,全部码字存储在8个D触发器内。当累加器大于或等于8时(即最高位由0到1跳变),此时A内已经拼接凑整了一个8位定长字,多路选择器输出该值。当累加器再次小于8时,此时B内已经拼接凑整一个8位定长字,多路选择器输出该值。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。