数字通信系统都需要位同步。实现位同步的方法也有插入导频法和直接法两种。

1.插入导频法

位同步信号一般从解调后(还未取样判决)的基带信号中提取。但许多数字基带信号(如全占空矩形)中无位同步分量,为了在接收端获取位同步信号,可在发送的数字基带信号中插入导频信号。

1)方法:在数字基带信号中插入导频信号后一并发送,接收端用窄带滤波器滤出此导频信号,并对其做适当的变换即可得位定时信号。

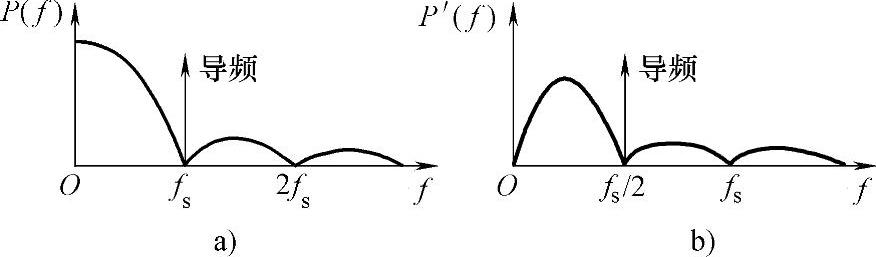

2)要求:在数字基带信号功率谱的零点处插入。例如,对于全占空矩形的单/双极性码及AMI码等信号,可以在第一个零点fs处插入导频信号。对于一些经过相关编码的数字基带信号,可在fs/2处插入导频信号,如图8-4所示。

图8-4 插入导频示意图

a)全占空码功率谱(单边) b)相关编码后的功率谱(单边)

3)特点:优点是设备简单,缺点是需要占用一定的信道带宽和发送功率。

2.直接法

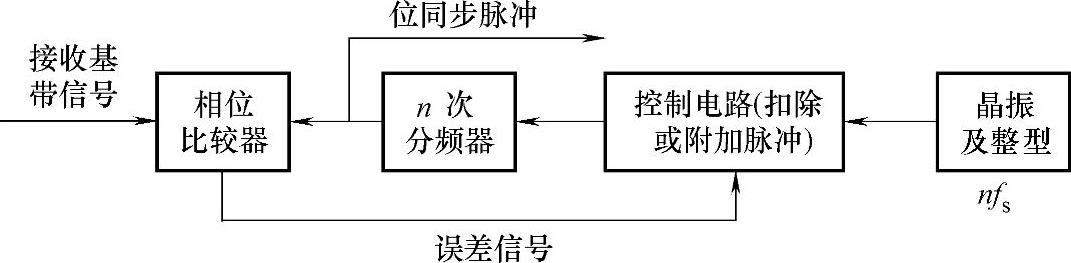

直接法是位同步的主要实现方法。它借助于位同步电路从接收到的基带信号中直接提取位同步信号。一种广泛应用的直接法是数字锁相环法,原理框图如图8-5所示。

图8-5 数字锁相环提取位同步信号原理图

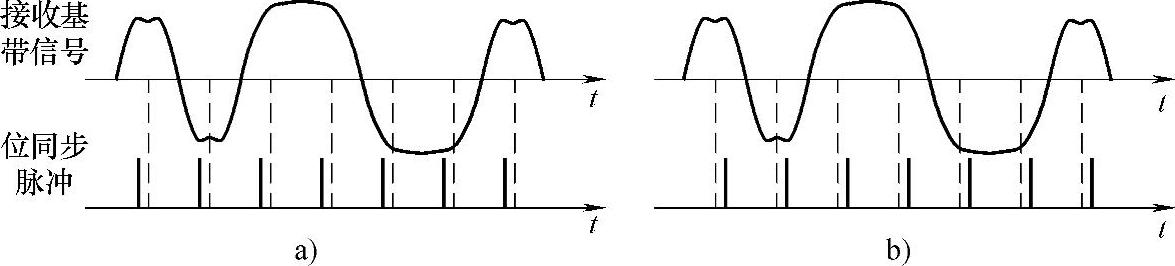

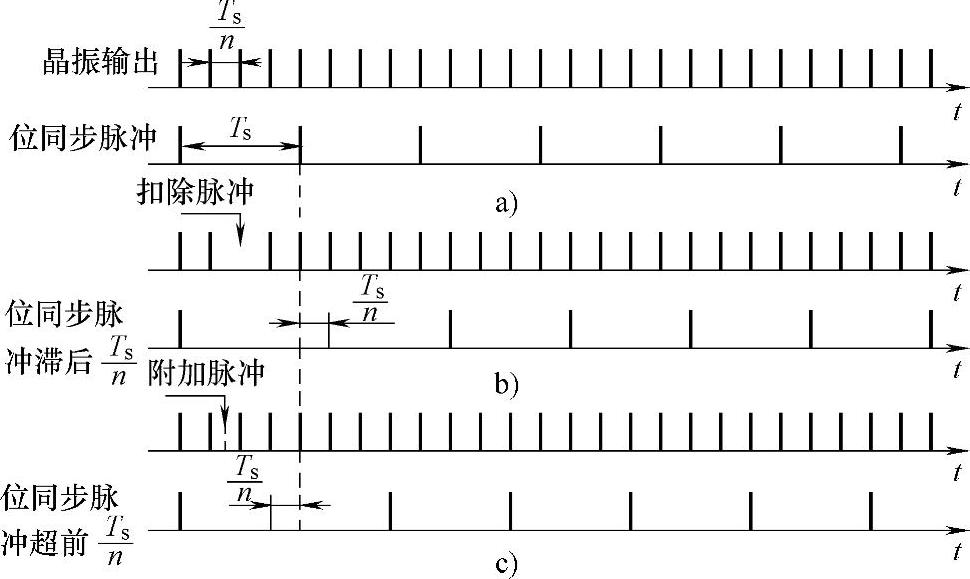

图8-5中,晶振产生频率为nfs的脉冲序列,经控制电路和n次分频器后产生一个频率为fs的位同步脉冲,其重复频率与发送码元速率相同。相位比较器用于比较位同步脉冲与接收基带信号的相位:①若位同步脉冲的位置超前于码元的最佳取样时刻,如图8-6a所示,则相位比较器送出的误差信号使控制电路从晶振送来的脉冲序列中扣除一个脉冲,使n次分频器输出的位同步脉冲向后调整Ts/n,如图8-7b所示。②若位同步脉冲的位置落后于最佳取样时刻,如图8-6b所示,则误差信号使控制电路在经过它的脉冲序列中附加一个脉冲,n次分频器输出的位同步脉冲向前调整Ts/n,如图8-7c所示。

图8-6 位同步脉冲与基带信号的相对位置

图8-7 位同步脉冲序列相位调整示意图(n=4)

可见,通过相位比较器和控制电路就可调整位同步脉冲的位置。重复进行相位的比较和脉冲的扣除或附加,最终使位同步脉冲对准接收码元的最佳取样时刻,即位同步脉冲与接收基带信号同相。(https://www.xing528.com)

需要说明的是,在图8-5所示的数字锁相环中,相位比较器是个关键部件,没有相位比较器的比较结果,控制电路既不会扣除脉冲也不会附加脉冲,也就意味着无法调整位同步脉冲的相位。而相位比较器是根据接收基带信号的过零点和位同步脉冲的位置来确定误差信号的,当发送长连“0”或长连“1”时,接收基带信号在很长时间内无过零点,相位比较器无法进行比较,致使位定时脉冲在长时间内得不到调整而发生漂移甚至失步。这也就是用HDB3来代替AMI码的原因。

3.位同步系统的性能指标

衡量位同步系统的主要性能指标有位定时误差、位同步建立时间、位同步保持时间和同步带宽。

(1)位定时误差

位定时误差是指建立同步后可能存在的最大误差。此误差是由位同步脉冲的跳跃式调整引起的,等于数字锁相环调整的步长,即

用相位表示为 或

或

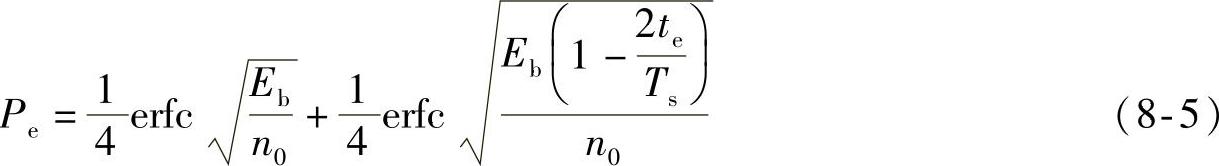

位定时误差导致取样时刻偏离最佳点,使取样值的幅度减小,系统的误码率上升。例如,当位定时误差为te时,2PSK的误码率上升为

欲减小te,应增大n。

(2)位同步建立时间

位同步建立时间是指重建位同步所需的最长时间,它等于位同步脉冲调整Ts/2所需的时间。由于位同步脉冲每次只能调整Ts/n的时间,且调整一次平均需要2Ts,故位同步建立时间为

欲减小ts,应减小n。可见,位定时误差和位同步建立时间对n的要求是矛盾的。

(3)位同步保持时间

位同步保持时间是指当锁相环失去调整后(输入信号中断或接收基带信号中出现长连“0”或长连“1”)位同步脉冲还能保持同步的时间。所谓“保持同步”是指位同步脉冲与最佳取样时刻的误差小于系统所允许的最大误差(超过所允许的最大误差时为失步)。可见,位同步保持时间与收、发晶振的稳定度和系统所允许的最大位同步误差有关。位同步保持时间越长越好。

(4)同步带宽

同步带宽是指同步系统能够调整到同步状态所允许的收、发两端晶振的最大频差。换句话说,如果收、发两端晶振的最大频差大于同步带宽的话,同步系统将无法建立同步,因为这种情况下,位同步脉冲的调整速度跟不上它与接收基带信号之间时间误差的变化。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。