位逻辑指令按照一定的控制要求进行逻辑组合,可构成基本的逻辑控制的“与”逻辑、“或”逻辑、“异或”逻辑及其组合逻辑。“与”逻辑、“或”逻辑、“异或”逻辑及其组合逻辑是基本的逻辑控制形式。位逻辑指令使用“0”或“1”两个布尔操作数(BOOL),对逻辑信号状态进行逻辑操作,逻辑操作的结果送入存储器状态字的逻辑操作结果(RLO)位。RLO用以赋值、置位、复位操作数的操作。“0”或“1”称为二进制数或位,用于表示信号状态,是构成二进制逻辑的基础。对于触点和线圈而言,“1”表示已闭合、激活或已励磁,“0”表示断开、未激活或未励磁。

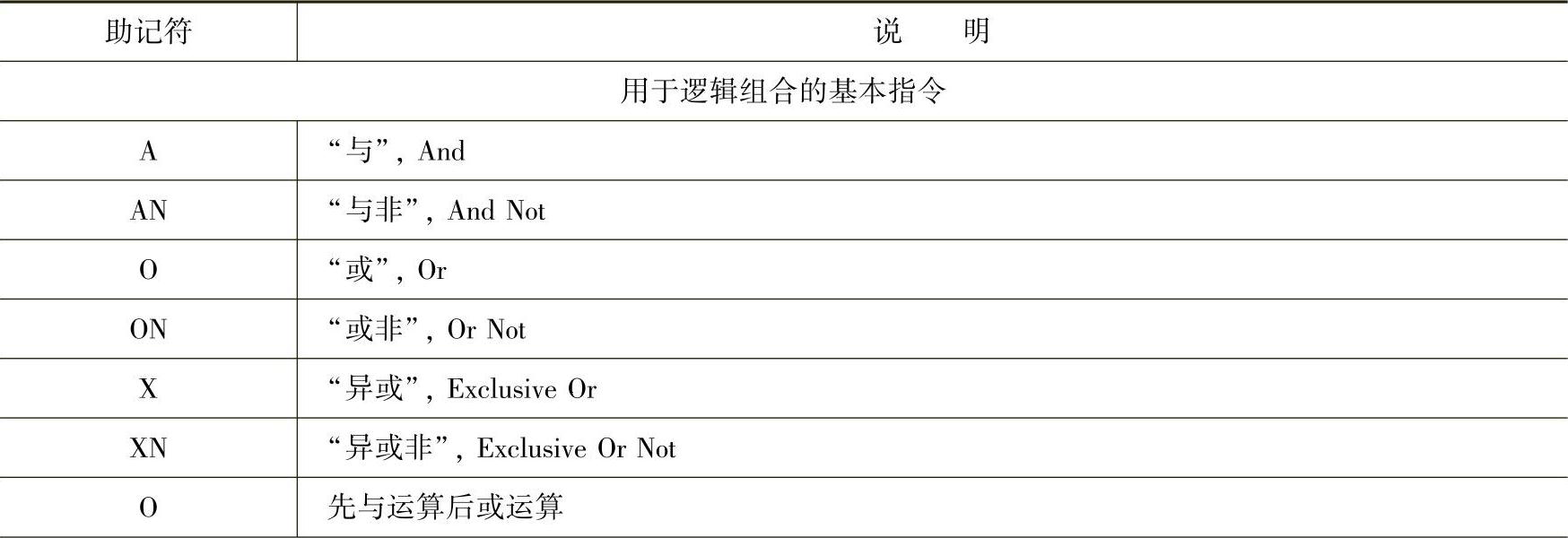

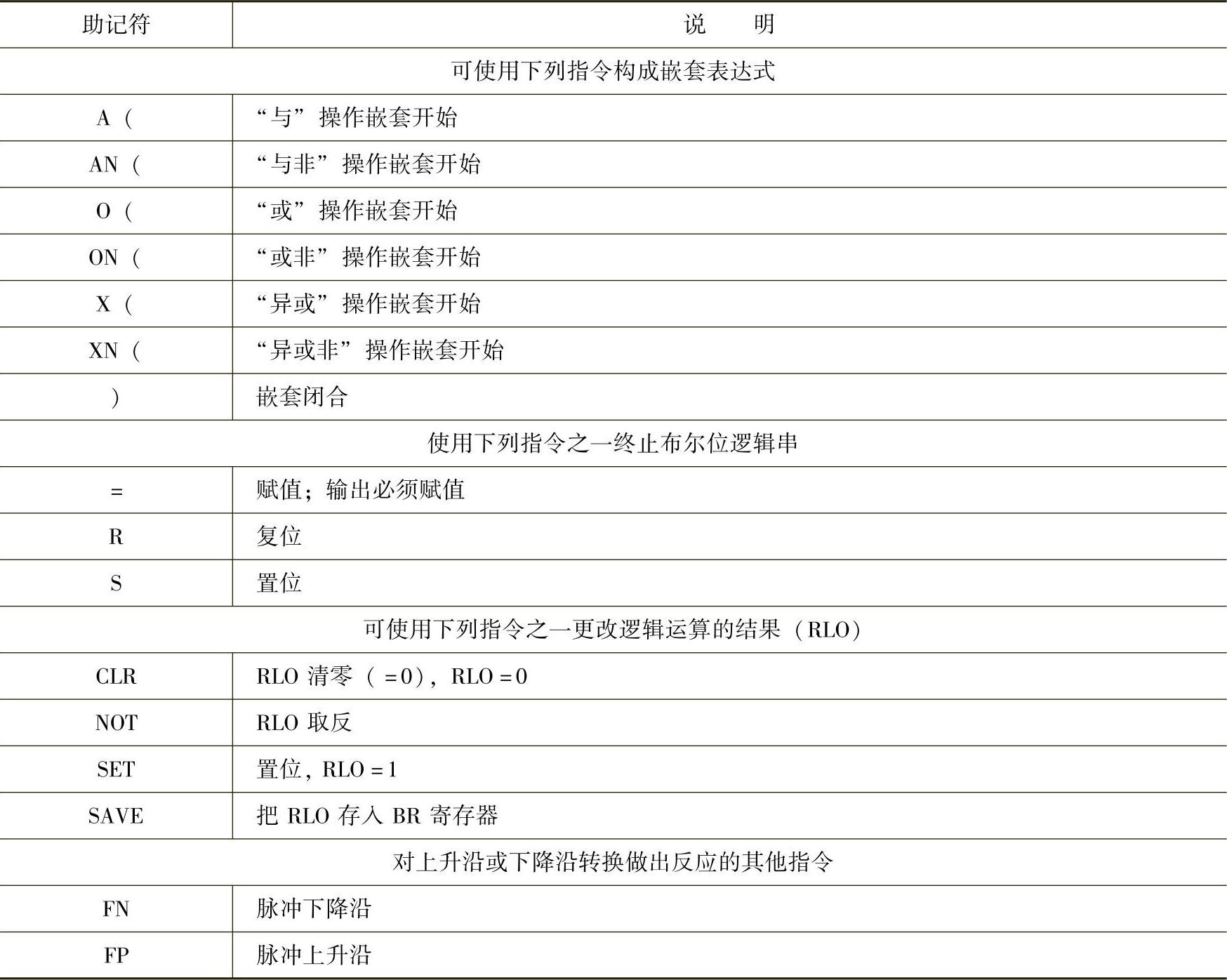

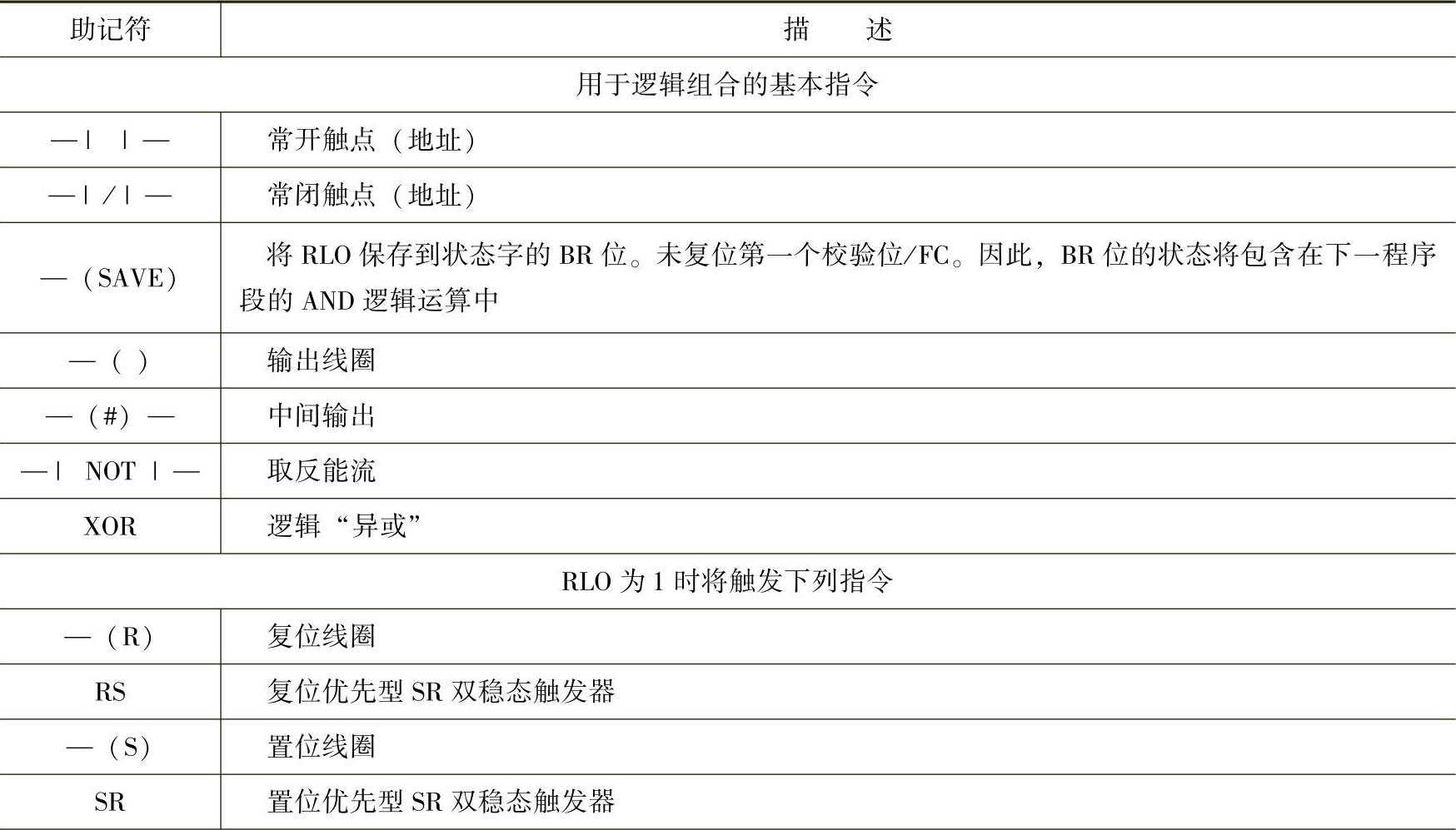

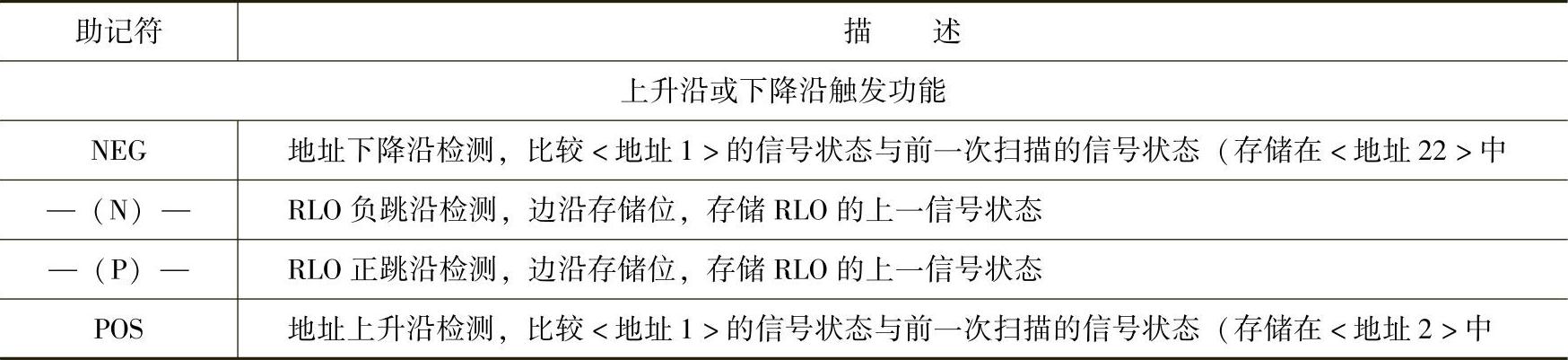

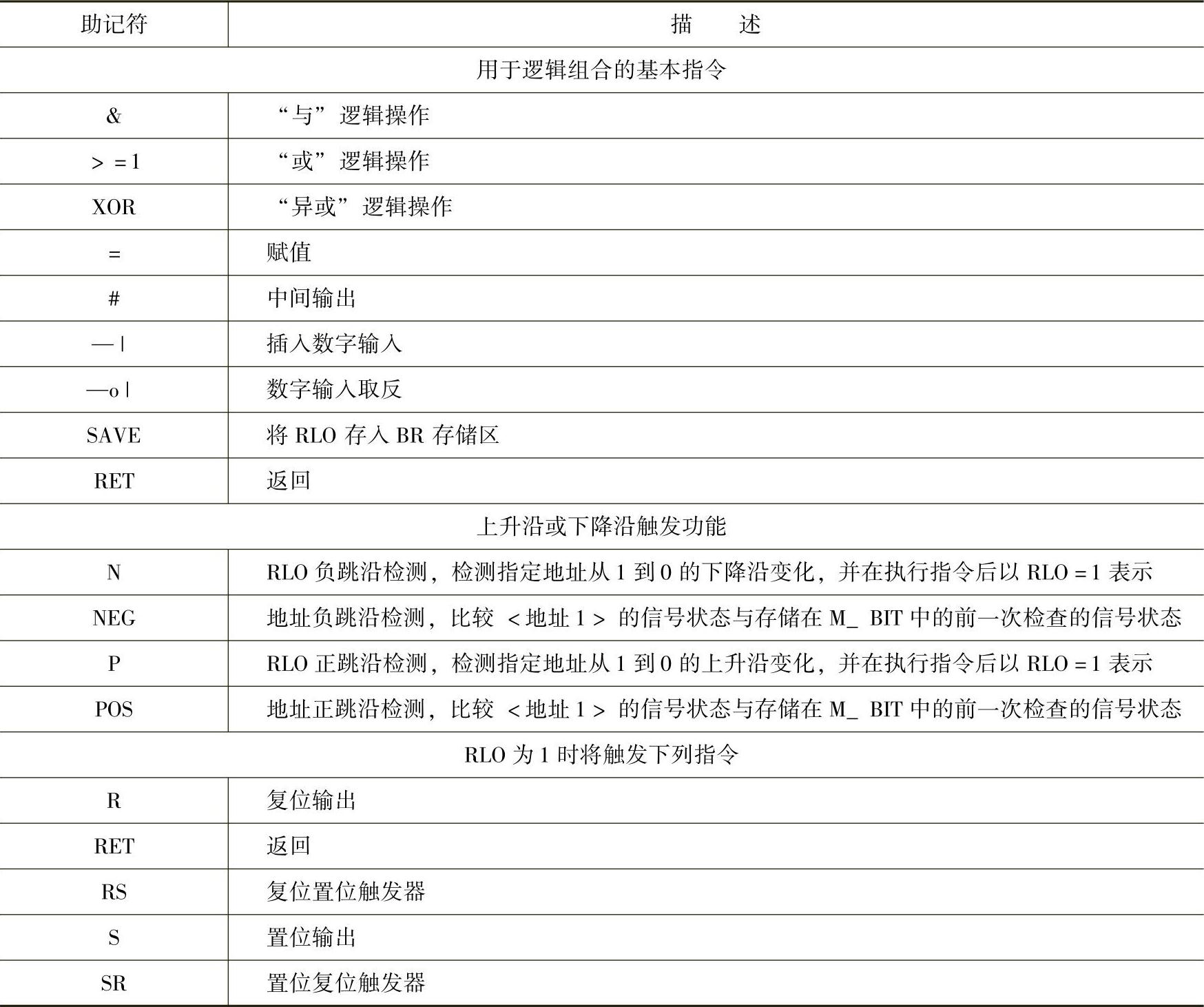

位逻辑指令的运算规则是“先与后或”操作,或者“先或后与”操作,用括号将需先运算的部分括起来,运算规则是“先括号内,后括号外”。这也是电路块的串并联连接规则。具有两个节点及以上的电路称为电路块。语句表STL表示的位逻辑基本指令见表6-2。梯形图LAD表示的位逻辑基本指令见表6-3。功能图FBD表示的位逻辑基本指令见表6-4。

表6-2 语句表STL表示的位逻辑基本指令

(续)

表6-3 梯形图LAD表示的位逻辑基本指令

(续)

表6-4 功能图FBD表示的位逻辑基本指令

1.逻辑“与”、“或”操作

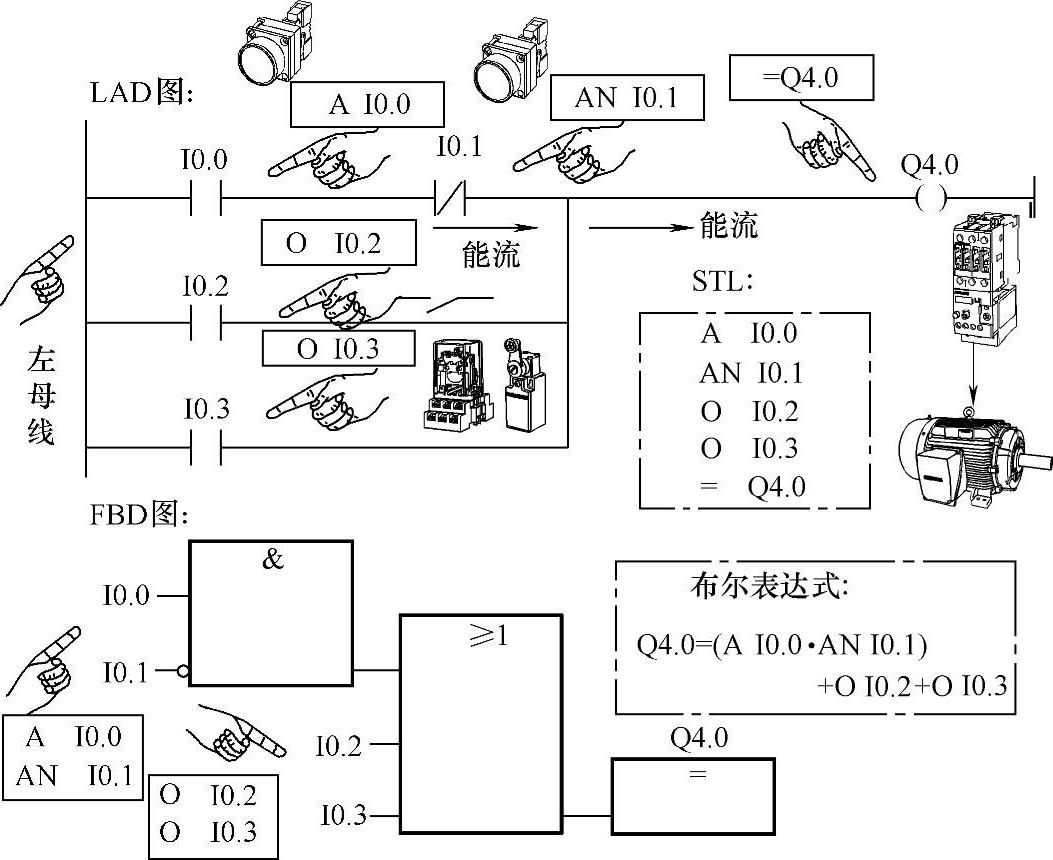

逻辑“与”在梯形图里是用串联的触点回路表示的,被扫描的操作数则表示为触点符号,操作数标在触点上方。如果接点是常开触点(动合触点),则对“1”扫描相应操作数。在PLC中,若操作数是“1”,则常开触点“动作”,即认为是“闭合”的;若操作数是“0”,则常开触点“不动作”,即触点仍然打开。如果触点是常闭触点(动断触点),则对“0”扫描相应操作数;若操作数是“1”,则常闭触点“动作”,即触点“断开”;若操作数是“0”,则常闭触点“不动作”,即触点仍保持闭合。如果串联回路里的所有触点皆闭合,则该回路能流流通,构成回路。即,逻辑“与”,当所有的输入信号都为“1”,则输出为“1”;只要输入信号有一个不为“1”,则输出为“0”。逻辑“或”,只要有一个输入信号为“1”,则输出为“1”;所有输入信号都为“0”,输出才为“0”。

逻辑“或”在梯形图里是用并联的触点回路表示的,被扫描的操作数标在触点上方。在触点并联的情况下,若有一个或一个以上的触点闭合,则该回路能流流通,构成回路。典型的逻辑“与”、“或”操作是一台电动机的自动控制电路,如图6-14所示。

图6-14 逻辑“与”、“或”操作示例

语句表(STL)如下:

A I0.0

AN I0.1

O I0.2

O I0.3

= Q4.0

逻辑表达式:

Q4.0=(AI0.0·ANI0.1)+OI0.2+OI0.3

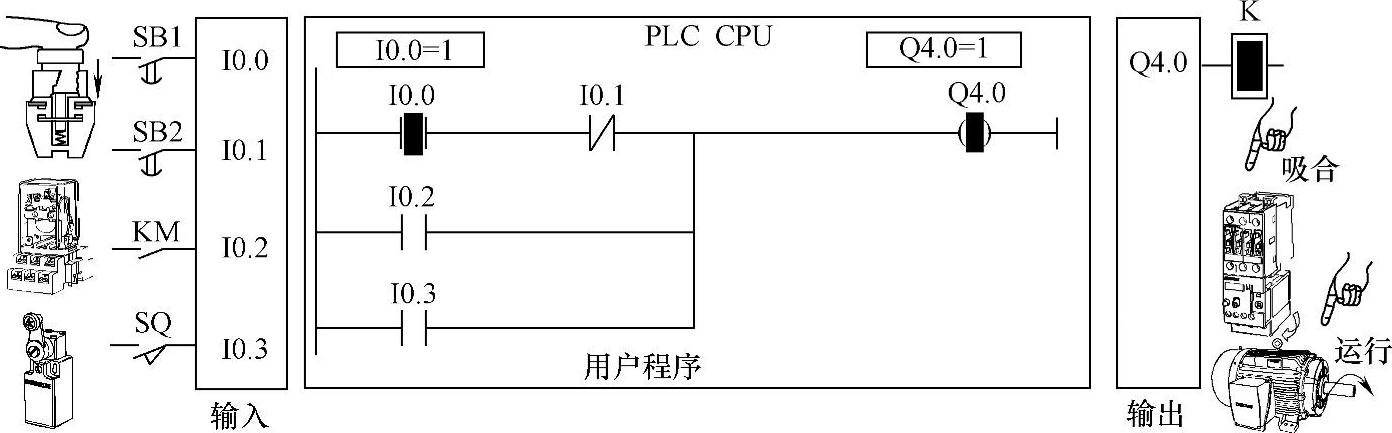

只要I0.1=1则当输入信号I0.0为“1”,输出就为“1”;或只要输入信号I0.2和I0.3中有一个为“1”,则输出为“1”;所有输入信号都为“0”,输出也为“0”。在图6-14中,现场的起动按钮SB1对应于I0.0,停止按钮SB2对应于I0.1,I0.3对应于有其他控制传递过来的继电器触点、行程开关等传感器信号。当操作SB1时,图6-14中梯形图的状态如图6-15所示。

在图6-15中,当操作启动按钮SB1(I0.0)时,第一行为逻辑“与”,助记符用“A和AN”标识,信号状态为“1”,逻辑操作结果(RLO)位的状态也为“1”,则输出信号Q4.0状态就为“1”。第二、三行为逻辑“或”,助记符用“O”标识,当操作数(I0.2或I0.3)的信号状态是“1”时,逻辑操作结果(RLO)位的状态就为“1”,则输出信号Q4.0状态也为“1”。

常开触点(常闭触点)的状态取决于相关操作数的信号状态。如果操作数的信号状态为“1”,常开触点将闭合。能流从左母线通过该常开触点流到右母线,并且该运算的输出信号状态变为“1”。如果操作数的信号状态为“0”,则常开触点不会被激活。到右母线的能流中断,并且该运算的输出的信号状态为“0”。常闭触点的操作数的信号状态为“1”时,触点“断开”并且到右母源线的能流中断,运算的输出的信号状态为“0”。如果操作数的信号状态为“0”,常闭触点将“闭合”。能流通过该常闭触点流到右母线,并且该运算的输出的信号状态设置为“1”。两个或多个常开触点(常闭触点)串联时,构成“与”逻辑,所有触点都闭合后才产生能流。常开触点(常闭触点)并联时,构成“或”逻辑,有一个触点闭合就会产生能流。由此可见,能流是使“输出线圈”指令被置位为“1”的约束条件。可以使用“输出线圈”指令运算置位指定操作数的位。线圈输入端的逻辑运算结果(RLO)为“1”时,指定操作数的信号状态将被置位为“1”。线圈输入端的信号状态为“0”时,指定操作数的位为“0”。该运算不会影响RLO。线圈输入端的RLO会立即发送到输出。

图6-15 当操作SB1时,图6-14中梯形图的状态

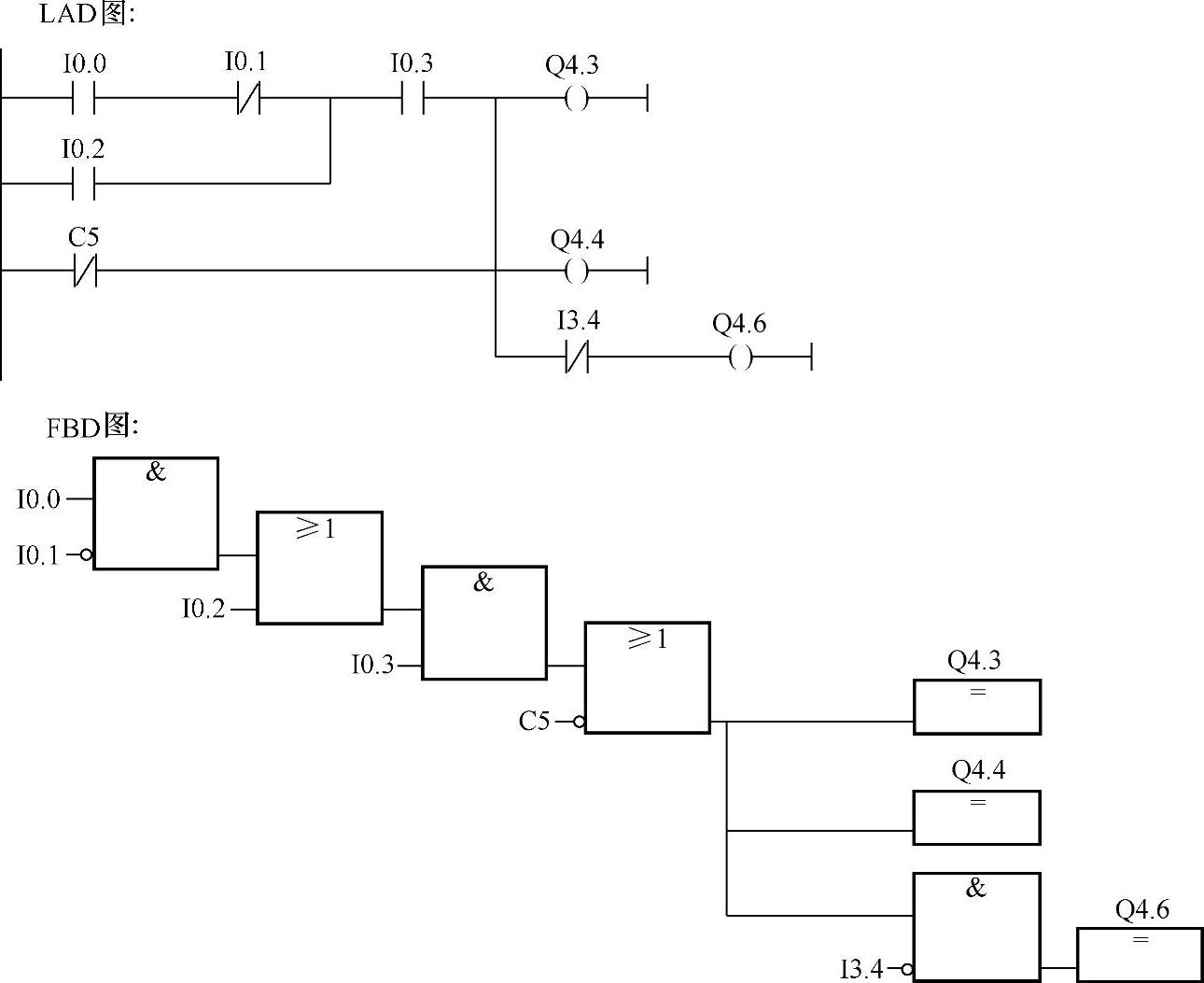

逻辑“与”、“或”嵌套示例:

A (

A I0.0

AN I0.1

O I0.2

)

A I0.3

ON C5

= L20.0

A L20.0

BLD 102

= Q4.3

A L20.0

BLD 102

= Q4.4

A L20.0

AN I3.4

= Q4.6

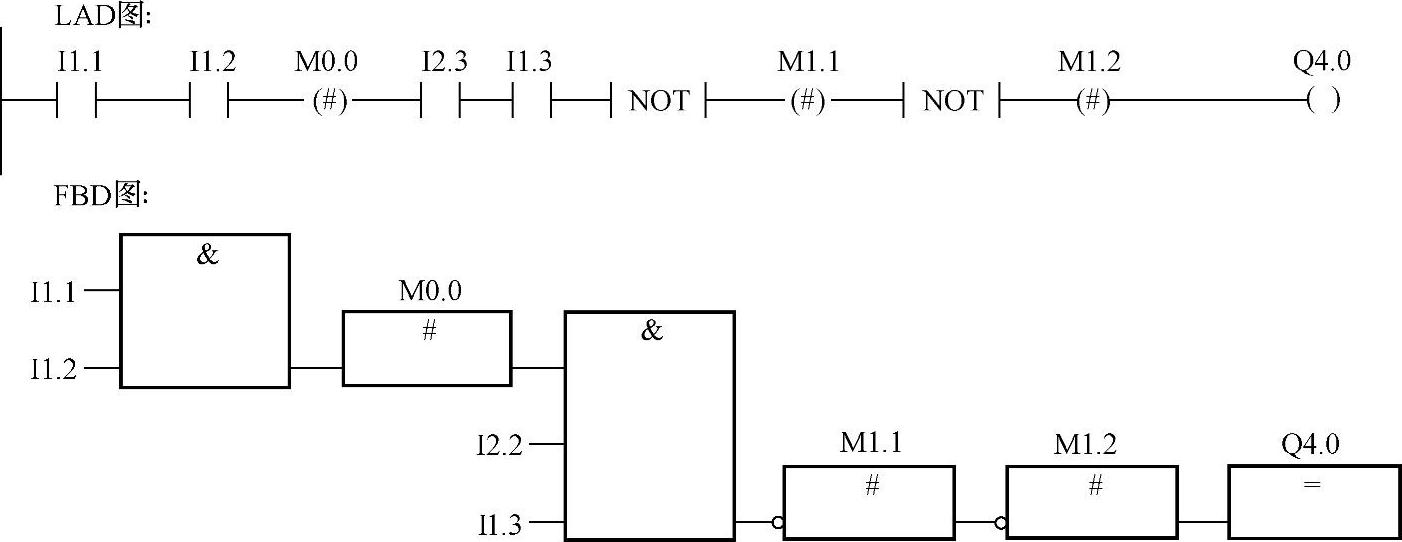

对应的LAD和FBD图如图6-16所示。

图6-16 逻辑“与”、“或”嵌套示例(https://www.xing528.com)

2.中间输出和取反操作

—(#)—,中间输出,中间输出用于存储RLO的中间值,该值是中间输出指令前的位逻辑操作结果。它将RLO位状态(能流状态)保存到指定<地址>。中间输出单元保存前面分支单元的逻辑结果。以串联方式与其他触点连接时,可以像插入触点那样插入—(#)—。不能将—(#)—单元连接到左母线或将它直接连接在分支连接的后面或分支的尾部。中间输出指令不能用于直接输出,即中间输出指令不能放在逻辑串的结尾处。存储区I、Q、M、L、D中的分配位。

使用功能图(FBD)符号:—o|;梯形图(LAD)符号:—|NOT|—;语句表(STL)符号:NOT,能流取反元素,可以取反操作—(#)—操作。逻辑取反操作是对逻辑运算结果RLO取反。如图6-17所示。

图6-17的逻辑关系是,M0.0的缓存器中存放着I1.1和I1.2相与的结果;M1.1的缓存器中存放着I1.1、I1.2、I2.2和I1.3四个输入信号相与后取反的结果;M1.2的缓存器中存放着整个逻辑运算的结果。

3.置位/复位指令

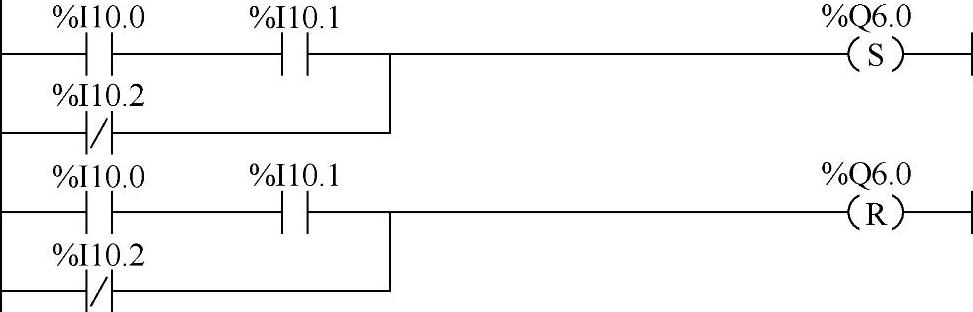

置位/复位指令根据RLO的值决定被寻址位的信号状态是否需要改变。在梯形图中,只有在能流通过线圈(RLO为“1”)时,才会执行置位线圈—(S)或执行复位线圈—(R)。置位线圈将把单元的指定<地址>置位为“1”。复位线圈将把单元的指定<地址>复位为“0”。RLO=0(没有能流通过线圈)将不起作用,单元的指定地址的当前状态将保持不变。

复位优先型SR双稳态触发器指令SR和置位优先型RS双稳态触发器指令RS(置位/复位触发器指令)仅在RLO为“1”时执行“置位”(S)或“复位”(R)指令。RLO为“0”时对这些指令没有影响,在指令中指定的地址保持不变。在输入端S的信号状态为“1”,而输入端R的信号状态为“0”时,置位复位触发器被置位。如果输入端S为“0”,而输入端R为1,则触发器被复位。如果两个输入的RLO均为“1”,则该触发器被复位。置位/复位线圈指令示例如图6-18所示。

图6-17中,当I10.0和I10.1输入都为“1”或者I10.2输入为“0”时,Q6.0被置位,即输出为“1”,否则,Q6.0的输出状态不变。当I10.0和I10.1输入都为“1”或者I10.2输入为“0”时,Q6.0被复位,即输出为“0”;不满足上述条件时,Q6.0的输出状态不变。

图6-17 中间输出和取反操作示例

图6-18 置位/复位线圈指令示例

图6-19 置位/复位双稳态触发器的指令符号

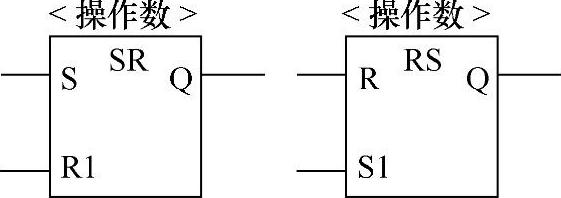

4.置位/复位双稳态触发器指令

置位/复位双稳态触发器的指令符号如图6-19所示。

图6-19中,

<操作数>,地址指定将要置位或复位的位。

SR,复位优先型SR双稳态触发器。

RS,置位优先型RS双稳态触发器。

S、S1,复位使能。

R、R1,置位使能。

Q,<地址>指定操作数的信号状态。

复位优先型RS触发器的S端在R1端之上,先在指定<地址>执行置位指令,当两个输入端S和R1都为“1”时,置位使能输入最终有效。既复位输入优先,触发器或被置位或保持置位不变。置位优先型RS触发器的R端在S1端之上,先在指定<地址>执行复位指令,当两个输入端R和S1都为“1”时,置位使能输入最终有效。既置位输入优先,触发器或被复位或保持复位不变。在梯形图中,置位/复位双稳态触发器指令方块可被看做一个特殊常开触点,其特性是,若方块的Q为“1”,则触点闭合;若Q为“0”,则触点断开。

可以使用“置位/复位触发器”或“复位置位触发器”指令操作基于输入S和R1或R和S1的信号状态置位或复位指定操作数的位。如果输入S的信号状态为“1”且输入R1的信号状态为“0”,指定的操作数将置位为“1”。如果输入S的信号状态为“0”且输入R1的信号状态为“1”,指定的操作数将复位为“0”。输入R1优先于输入S。如果两个输入S和R1的信号状态均为“1”,指定操作数的信号状态将复位为“0”。如果两个输入R1和S的信号状态为“0”,则不执行该运算。操作数的信号状态因此保持不变。如果输入R的信号状态为“1”且输入S1的信号状态为“0”,指定的操作数将复位为“0”。如果输入R的信号状态为“0”且输入S1的信号状态为“1”,指定的操作数将置位为“1”。输入S1优先于输入R。如果两个输入R和S1的信号状态均为“1”,指定操作数的信号状态将置位为“1”。如果两个输入R和S1的信号状态为“0”,则不执行该运算。操作数的信号状态因此保持不变。

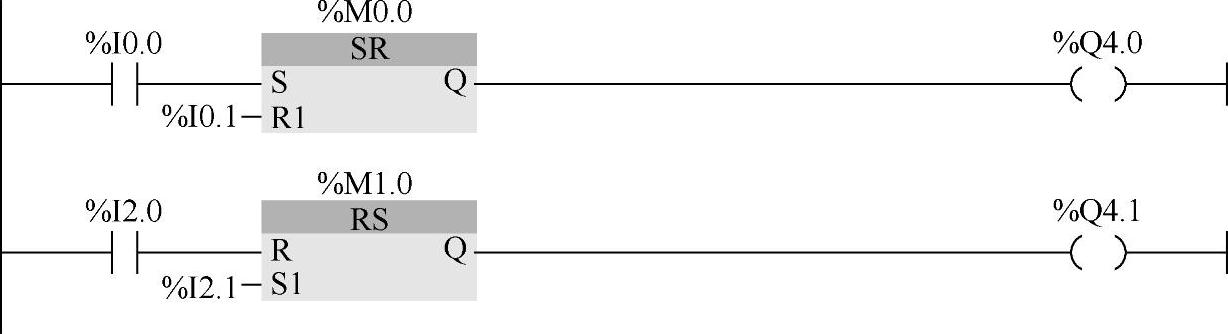

置位/复位双稳态触发器指令应用示例如图6-20所示。

图6-20 SR触发器和RS触发器指令应用示例

如果输入端I0.0的信号状态为“1”,I0.1的信号状态为“0”,则置位存储器位M0.0,输出Q4.0将是“1”。否则,如果输入端I0.0的信号状态为“0”,I0.1的信号状态为“1”,则复位存储器位M0.0,输出Q4.0将是“0”。如果两个信号状态均为“0”,则不会发生任何变化。如果两个信号状态均为“1”,将因顺序关系执行复位指令;复位M0.0,Q4.0将是“0”。

如果输入端I2.0的信号状态为“1”,I2.1的信号状态为“0”,则复位存储器位M1.0,输出Q4.1将是“0”。否则,如果输入端I2.0的信号状态为“0”,I2.1的信号状态为“1”,则复位存储器位M1.0,输出Q4.1将是“1”。如果两个信号状态均为“0”,则不会发生任何变化。如果两个信号状态均为“1”,将因顺序关系执行置位指令;置位M0.0,Q4.0将是“1”。

5.边沿识别指令

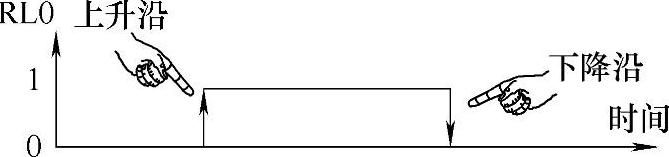

边沿状态识别包括扫描操作数、置位操作数和信号置位三类。当边沿状态信号变化时就会产生跳变沿,当从“0”变到“1”时,产生一个上升沿(正跳沿);若从“1”变到“0”,则产生一个下降沿(负跳沿)。在每个扫描周期中把信号状态和它在前一个扫描周期的状态进行比较,若不同则表明有一个跳变沿。因此,前一个周期里的信号状态必须被存储,以便能和新的信号状态相比较。如图6-21所示。

当边沿检测指令检测到输入有一个下降沿,将使输出线圈在一个扫描周期内通电。对输入扫描的RLO值存放在沿存储器位中。在OB1扫描周期中,CPU扫描并形成RLO值,若该RLO值是“0”,且上次RLO值是“1”,这说明边沿检测指令检测到一个RLO的下降沿,则边沿检测指令将RLO位置“1”。当边沿检测指令检测到输入有一个上升沿,将使输出线圈在一个扫描周期内通电。对输入扫描的RLO值存放在沿存储器位中。在OB1的扫描周期中,CPU扫描并形成RLO值,若该RLO值是1,且上次RLO值是0,这说明边沿检测指令检测到一个RLO的上升沿,则指令将RLO位置1。如果RLO在相邻的两个扫描周期中相同(全为“1”或“0”),指令将RLO位清0。需要注意的是,在编程时必须考虑到,边沿检测指令检测到的一般是在RLO中表现出的变化,而不是触点的状态变化。因为,一般情况下,RLO可能由一个逻辑串形成,并不单独与某触点状态直接相关。若需要在逻辑串中单独检测某触点的跳变沿,可使用对触点跳变沿直接检测边沿信号识别指令。

(1)扫描操作数—|P|—指令。“扫描操作数的信号上升沿”—|P|—指令有两个操作数,可用于确定指定<操作数1>的信号状态是否从“0”变为“1”。比较<操作数1>的当前信号状态与保存在<操作数2>中的上一次查询的信号状态。如果检测到逻辑运算结果从“0”变为“1”,则说明出现了上升沿。如果检测到上升沿,操作的输出的信号状态将为“1”。在任何其他情况下,操作的输出的信号状态为“0”。—|P|—指令可以放置在程序段中的任何位置。

图6-21 跳变沿检测原理

(2)扫描操作数—|N|—指令。“扫描操作数的信号下降沿”—|N|—指令有两个操作数,用于查询指定<操作数1>的信号状态是否从“1”变为了“0”。比较<操作数1>的当前信号状态与保存在<操作数2>中的上一次查询的信号状态。如果检测到逻辑运算结果从“1”变为“0”,则说明存在下降沿。如果检测到下降沿,操作的输出的信号状态将为“1”。如果没有下降沿,到右侧电源线的信号状态将复位为“0”。—|N|—指令可以放置在程序段中的任何位置。

(3)置位操作数—(P)—指令。“在信号上升沿置位操作数”—(P)—指令有两个操作数,用于操作在能流从“0”变为“1”时置位指定操作数。将当前逻辑运算结果(RLO)与保存在沿位存储器中的上次查询的运算结果进行比较。如果检测到能流从“0”变为“1”,则说明出现了上升沿。如果出现了上升沿,<操作数1>的信号状态将置位为“1”一个程序周期。在任何其他情况下,操作数的信号状态为“0”。—(P)—指令可以放置在程序段的中间或者右端。通过使用分支,多个线圈可以相互嵌套放置。

(4)置位操作数—(N)—指令。“在信号下降沿置位操作数”—(N)—指令有两个操作数,用于操作在能流从“1”变为“0”时置位指定操作数。将当前逻辑运算结果(RLO)与保存在沿位存储器中的上次查询的运算结果进行比较。如果该操作检测到能流从“1”变为“0”,则说明出现了下降沿。检测到下降沿时,<操作数1>的信号状态将置位为“1”一个程序周期。在任何其他情况下,操作数的信号状态为“0”。—(N)—指令可以放置在程序段的中间或者右端。通过使用分支,多个线圈可以相互嵌套放置。

上述指令沿存储器位的地址在程序中最多只能使用一次,否则,该存储器位会被覆盖,并且结果会变得不明确。操作不会影响RLO。线圈输入端的RLO将立即发送到线圈输出端。

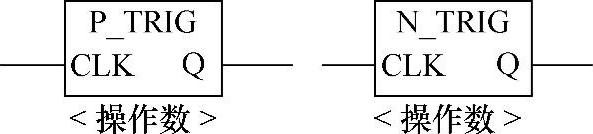

(5)信号置位输出P_TRIG指令。P—TRIG指令图形符号如图6-22所示。“在信号上升沿置位输出”P_TRIG指令用于操作查询逻辑运算结果的信号状态是否从“0”变为了“1”。比较逻辑运算结果(RLO)的当前信号状态(CLK端)与保存在沿位存储器中的上一次查询的信号状态。如果检测到RLO从“0”变为“1”,则说明出现了上升沿。如果检测到上升沿,操作的输出的信号状态将为“1”。在任何其他情况下,操作的输出的信号状态为“0”。P_TRIG指令可以放置在程序段的中间。

(6)信号置位输出N_TRIG指令。N_TRIG指令图形符号如图6-22所示。“在信号下降沿置位输出”N_TRIG指令用于操作检测逻辑运算结果(RLO)的信号状态是否从“1”变为了“0”。比较逻辑运算结果的当前信号状态(CLK端)与保存在沿存储器位中的上一次查询的信号状态。如果该操作检测到RLO从“1”变为“0”,则说明存在下降沿。如果检测到下降沿,操作的输出的信号状态将为“1”。在任何其他情况下,操作的输出的信号状态为“0”。N_TRIG指令可以放置在程序段的中间。

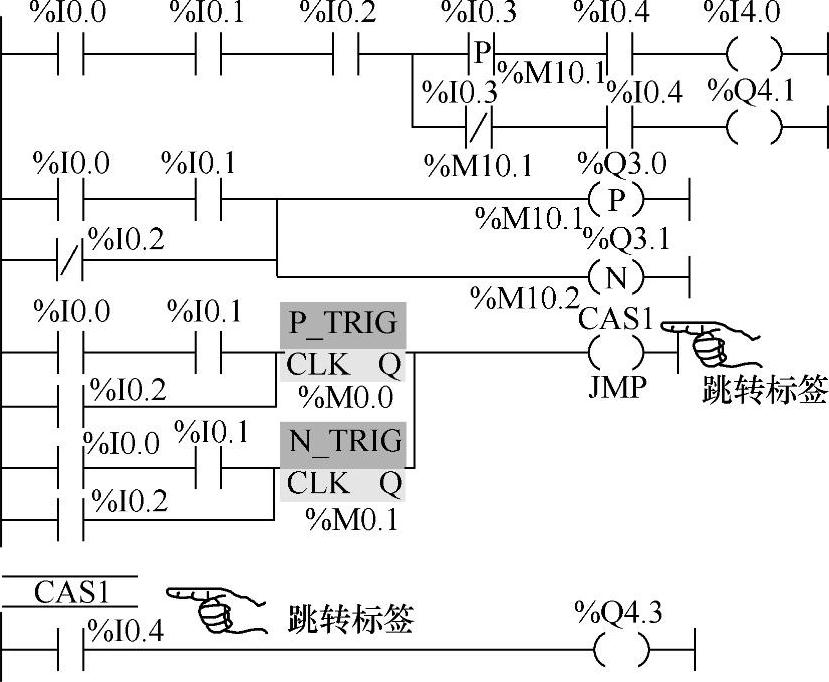

在梯形图中,边沿信号检测指令方块可被看做一个特殊常开触点,其特性是,若方块的Q为“1”,则触点闭合;若Q为“0”,则触点断开。边沿检测指令应用示例如图6-23所示。

图6-22 P_TRIG和N_TRIG指令的图形符号

在图6-23中,如果输入I0.0、I0.1和I0.2的信号状态为“1”,输入I0.3有上升沿,输入I0.4的信号状态为“1”,输出Q4.0将置位。如果输入I0.0、I0.1及I0.2的信号状态为“1”,输入I0.3有下降沿,输入I0.4的信号状态为“1”,输出Q4.1将置位。如果置位操作数—(P)—指令输入端的信号状态从“0”切换到“1”时(上升沿),输出Q3.0将置位一个程序周期。在任何其他情况下,输出Q3.0的信号状态为“0”。而当置位操作数—(N)—指令输入端的信号状态从“1”切换到“0”时(下降沿),输出Q3.1将置位一个程序周期。在任何其他情况下,输出Q3.1的信号状态为“0”。

P_TRIG指令的全部输入位逻辑运算的RLO均保存在沿位存储器M0.0中。如果RLO的信号状态从“0”变为“1”,则程序将跳转到跳转标签CAS1。N_TRIG指令全部输入位逻辑运算的RLO保存在沿存储器位M0.1中。如果检测到RLO的信号状态从“1”变为“0”,程序将跳转到跳转标签CAS1。

图6-23 边沿检测指令应用示例

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。