1.二进制译码器

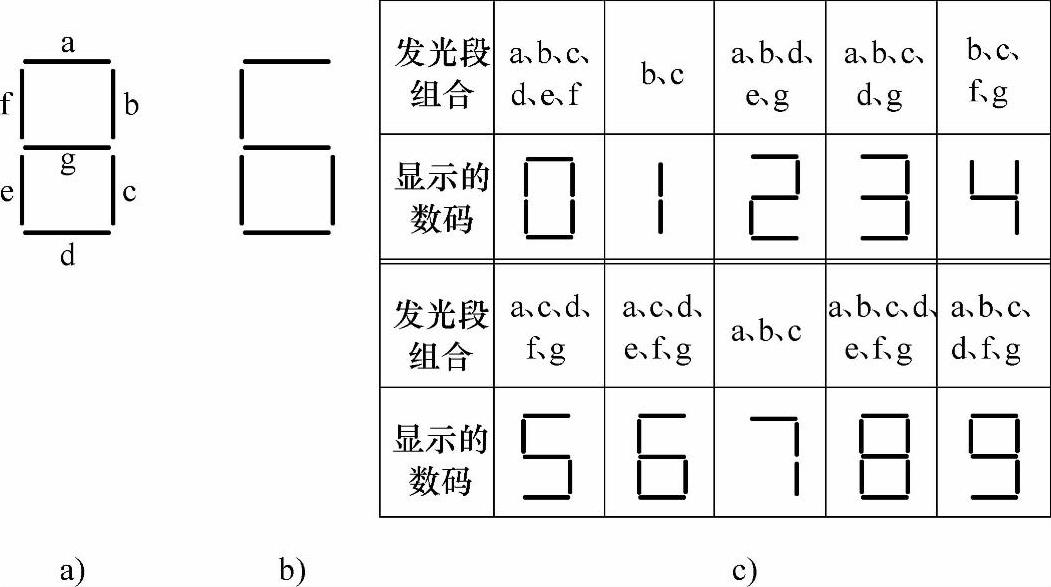

(1)七段显示数码原理 在数字电路技术中,可以利用数码管显示0~9十个数码,采用七段显示方式,如图8-16a所示。图中的a、b、c、d、e、f、g就是数码管中被制成条状的七个PN结。有选择地使其中需要的段发光,就能组成十个不同的数码。如:使b、c两段发光,则显示出数码1;再如:使a、c、d、e、f、g段均发光,则显示数码6,如图8-16b所示,其余类推。

图8-16 七段显示器

a)七段显示方式 b)数码6的显示 c)段组合及数码

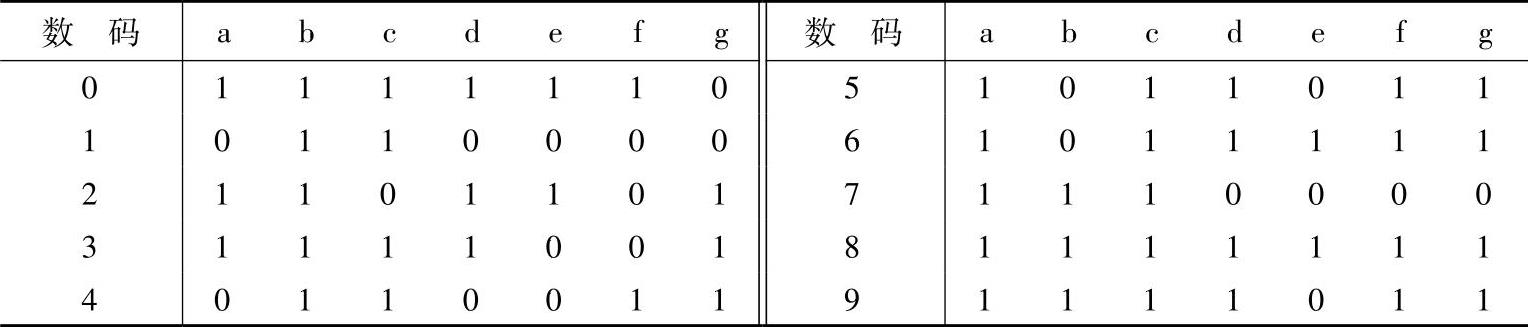

表8-7列出了通过a、b、c、d、e、f、g的组合,获得0~9十个数码的编码表。表中1表示发光段,0表示不发光段。这里是用七位二进制数码来实现编码的。

表8-7 0~9数码编码表

七段显示器显示十进制数的过程如下:首先通过与显示器联接的译码器,将计数器存储到寄存器中的数字通过译码器翻译出来,然后经过驱动器点亮对应的段,从而显示出相应的十进制数码。段组合及数码如图8-16c所示。

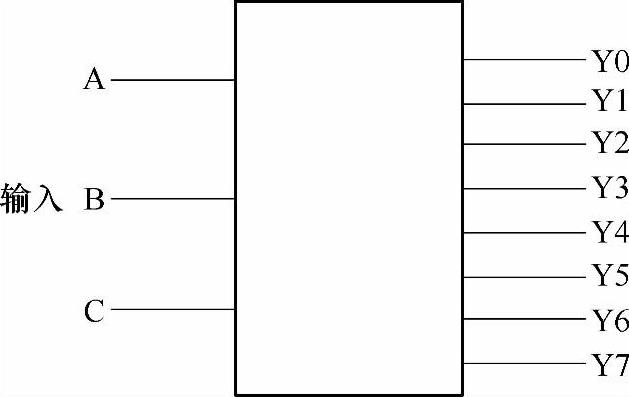

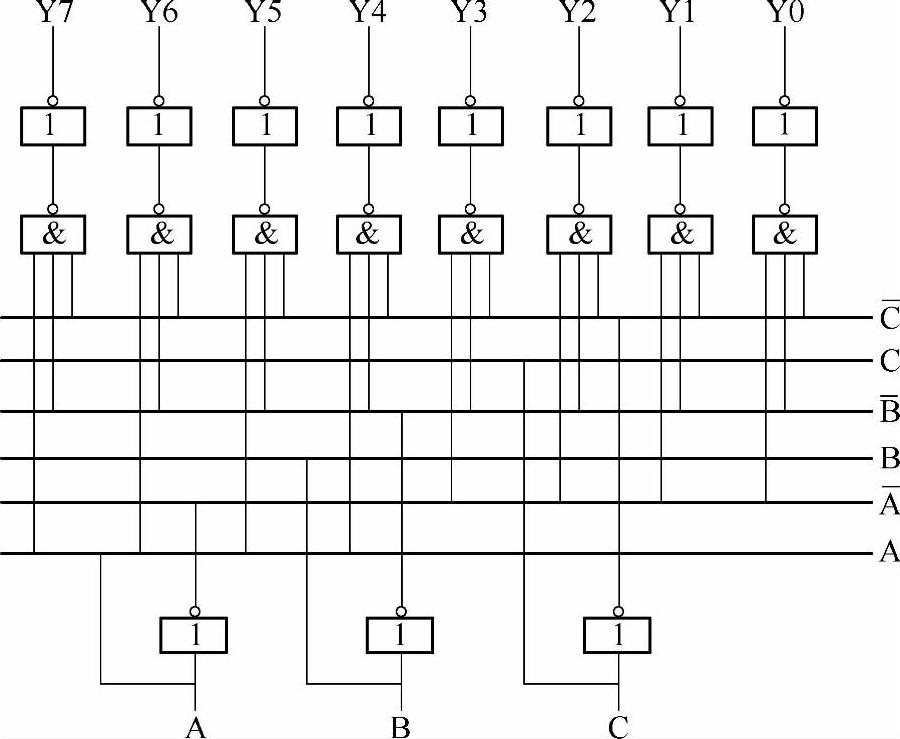

(2)二进制译码器工作原理 二进制译码器是将具有特定含意的一组二进制代码,按其原意翻译成对应输出信号的逻辑电路。二进制译码器按其输入端和输出端数目的不同,分为2线-4线译码器、3线-8级译码器和4线-16线译码器等。二进制译码器可以用二极管与门组成,也可以用集成电路与非门组成。这里只对集成电路与非门译码器进行讨论。图8-17所示为一个三位译码器框图。

图8-17 三位译码器框图

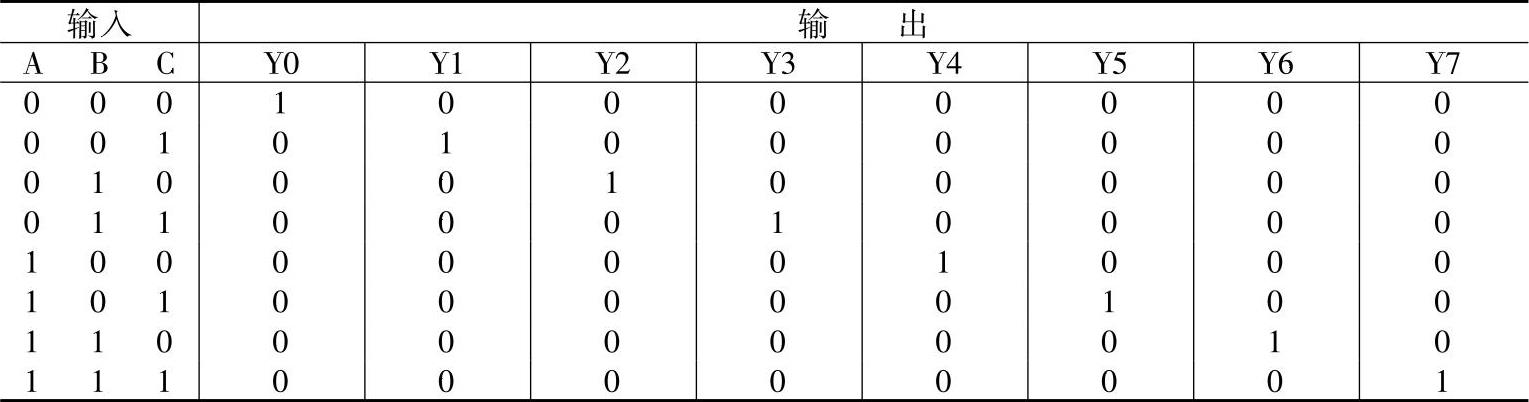

该译码器输入的是一组三位二进制代码,三位二进制数可组成八种不同的代码,这八种不同的代码又可对应八个十进制数,即0~7。设A、B、C为三个输入变量,Y0~Y7为八个输出变量,则输入和输出的状态关系可用表8-8来表示。

表8-8 三位译码器状态表

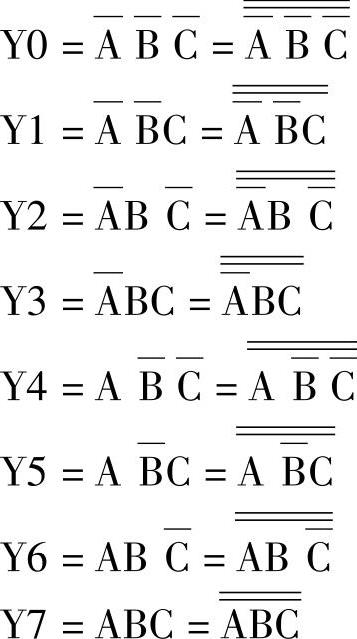

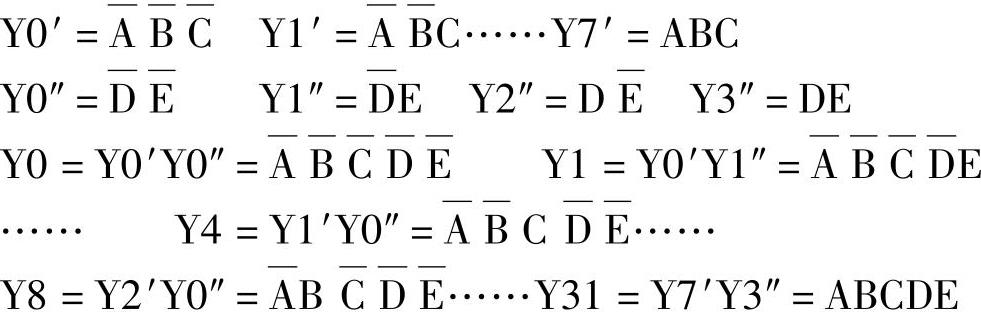

由状态表可写出如下逻辑式:

根据上述逻辑式可画出逻辑电路,如图8-18所示。

图8-18 二进制三位译码器逻辑电路

译码器的工作原理如下:当输入代表十进制数6的二进制代码ABC=110时,由逻辑式可知,只有输出端Y6=1,而其他输出端均为0。因此,仅代表6的Y6线上有输出信号。简而言之,每输入一组代码,译码器就有相应的输出端输出高电平,并以此激励驱动电路,使数码管获得较大的驱动电流而发光。

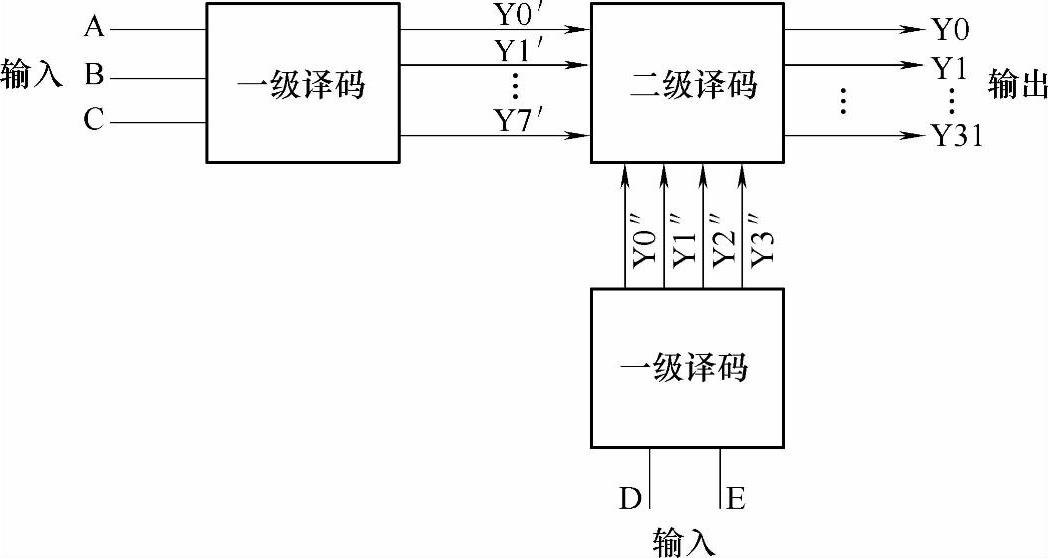

分析图8-18可知,一个n位二进制译码器就要由2n个与非门组成,每个与非门要有n个输入端。但是,与非门输入端最多只有6个,所以当二进制代码的位数多于与非门的输入端数时,门电路的数量会大大增加。在这种情况下,常采用分级译码以减少电路的数目。如对一个五位二进制代码译码时,是将这个代码分成两组,一组为三位,另一组为两位。先将这两组分别采用上面的方式译码,称为一级译码。最后把两组一级译码的输出进一步译码,称为二级译码。图8-19是对一个五位二进制代码分级译码框图。一、二级译码输入与输出的逻辑关系为

图8-19 五位二进制代码分级译码框图(https://www.xing528.com)

由此可看出,分级译码是利用增加与非门的数量来减少译码器输入端数目的。

2.二-十进制译码器

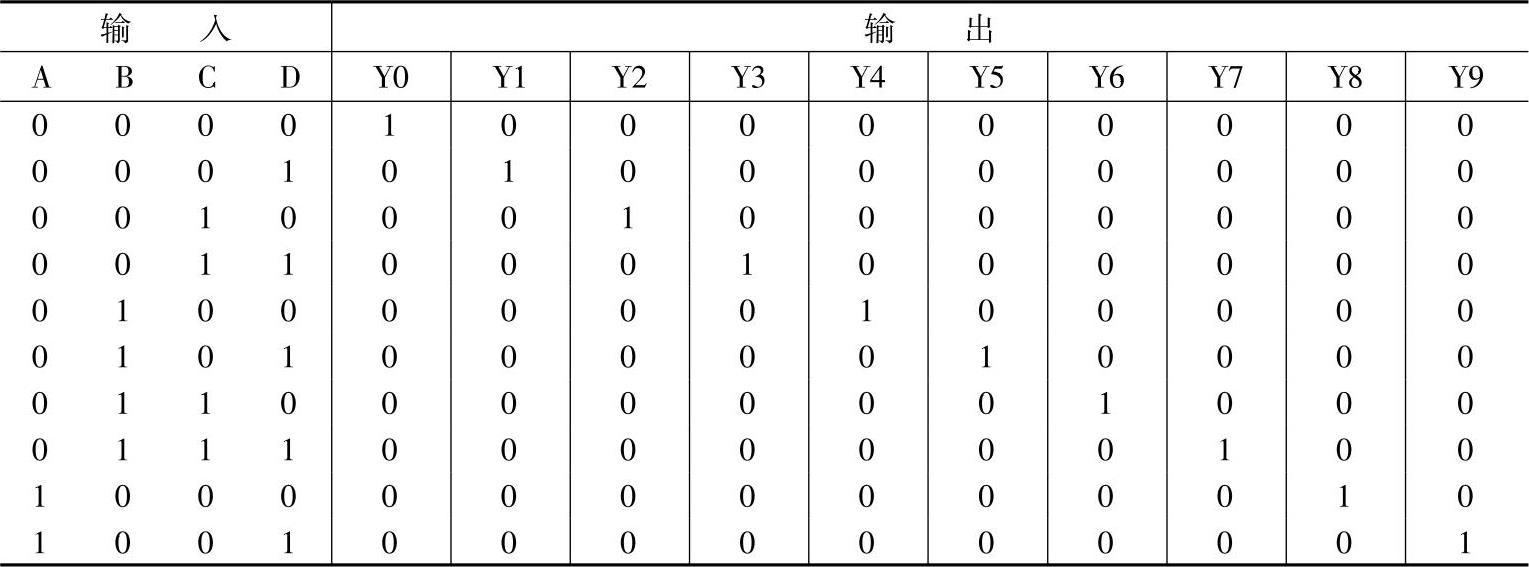

(1)8421码译码器的设计 将二-十进制代码翻译成十进制数信号的逻辑电路称为二-十进制译码器。8421码译码器是二-十进制译码器中的一种。设译码器的输入为二进制代码A、B、C、D,输出为Y0、Y1、……Y9,输入、输出的状态关系见表8-9。

表8-9 8421码译码器状态表

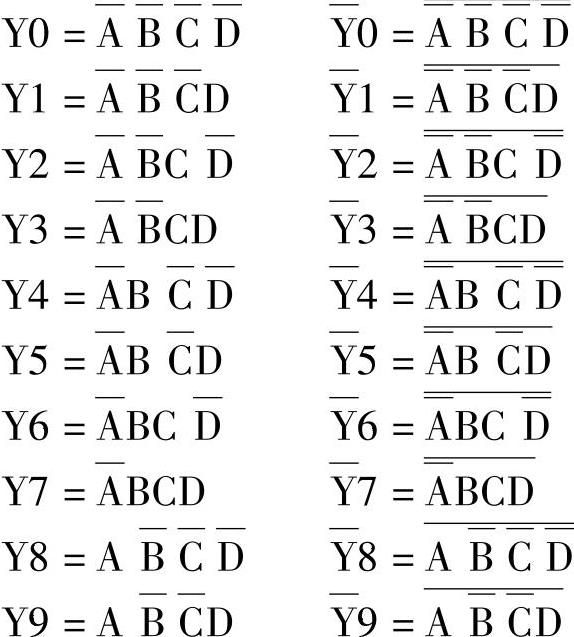

由状态表可写出0~9十个十进制数输出的逻辑式为

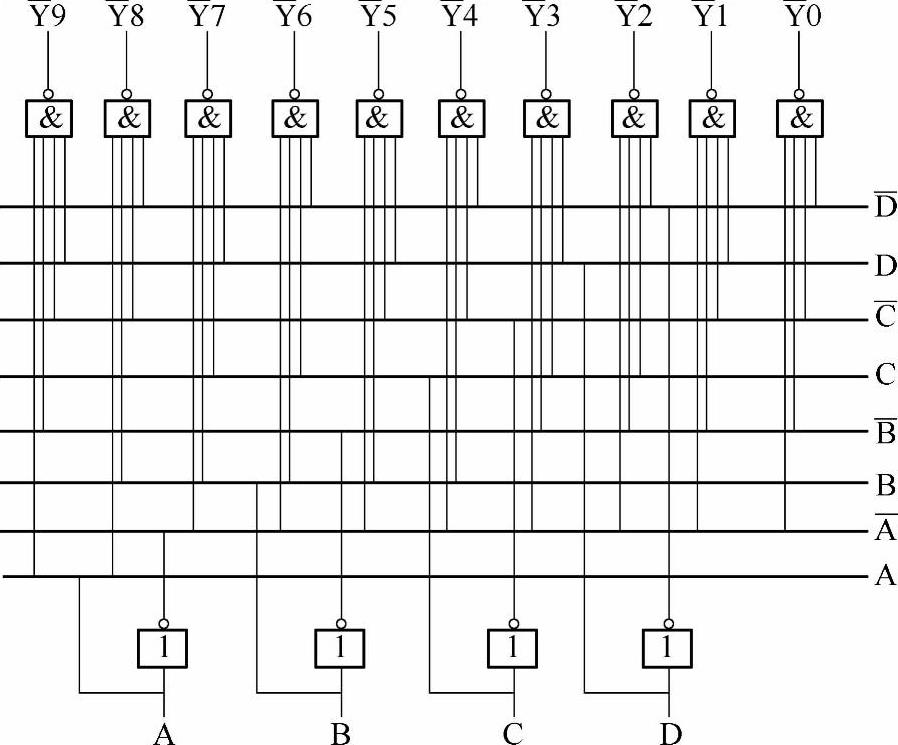

由Y0~Y9反变量逻辑表示式可画出译码器的逻辑电路图,如图8-20所示。

图8-20 8421码译码器逻辑电路

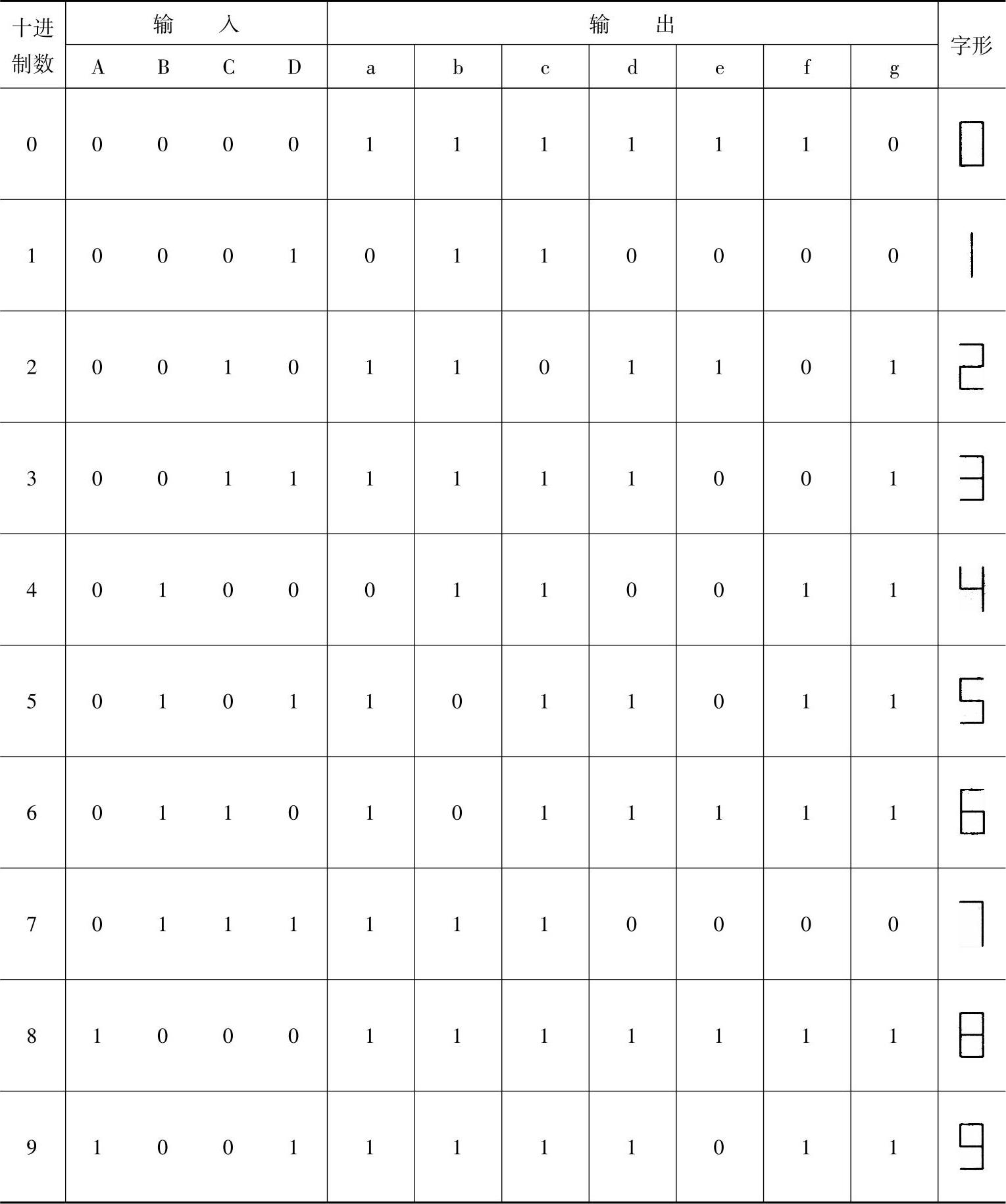

(2)8421码译码器的应用——七段字形译码器 分段式数码管要求译码器能直接将BCD码翻译成显示器所需要的七位二进制代码。由8421BCD码的编码表和图8-16a所示的七段显示方式,可列出A、B、C、D四个输入变量和a、b、c、d、e、f、g七个输出变量之间的逻辑状态表,见表8-10。

表8-10 8421码和七段显示输出状态表

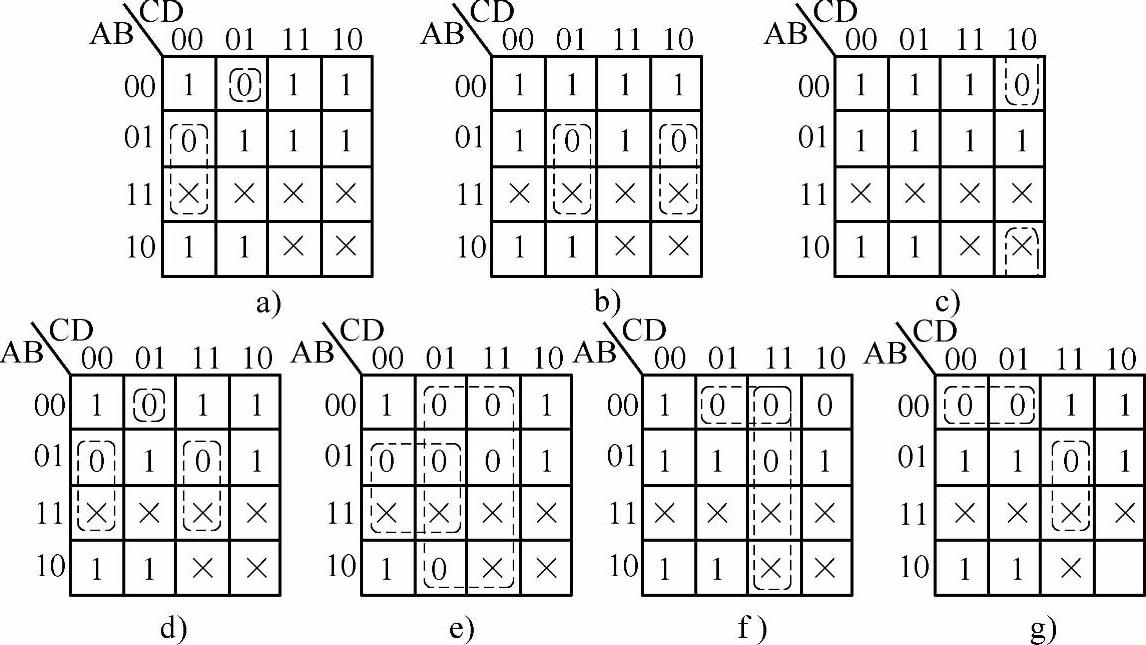

根据状态表画出每个显示段的卡诺图,如图8-21所示。

图8-21 七段显示输入-输出状态的卡诺图

卡诺图中以“1”表示亮,“0”表示暗。由于输入为8421BCD码,1010~1111六种状态未被采用,故作为约束项处理,用“×”表示。

由卡诺图可看出,0状态较少,故写出 、

、 、

、 、

、 、

、 、

、 、

、 的逻辑表达式较简便。

的逻辑表达式较简便。

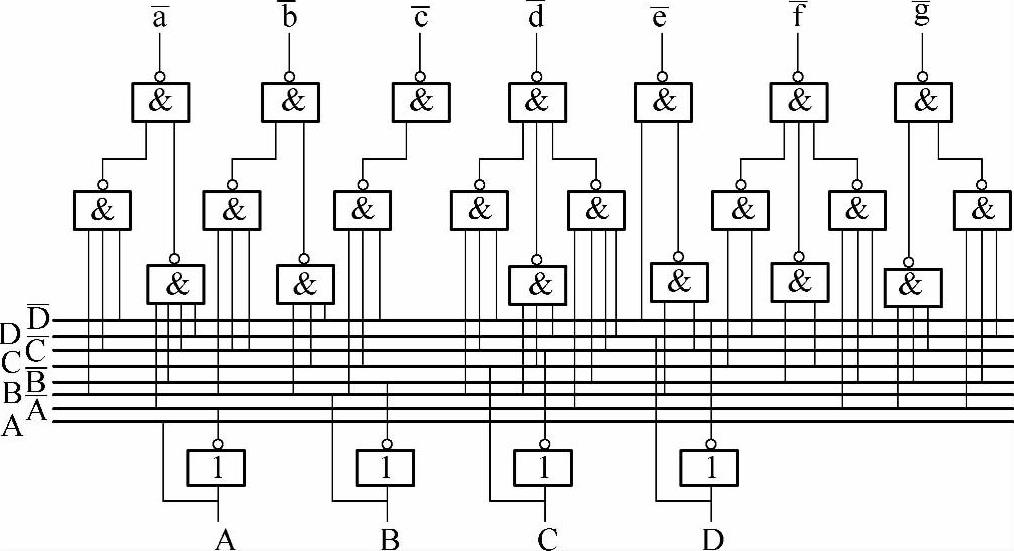

根据上述逻辑表达式画出逻辑电路如图8-22所示。

图8-22 七段译码器逻辑电路

若输入的8421码为0101,A=0、B=1、C=0、D=1,则输出端 、

、

、

、 、

、 、

、 、

、 、

、 。也就是说,a、c、d、f、g五段发光,七段数码管显示出数码“5”。

。也就是说,a、c、d、f、g五段发光,七段数码管显示出数码“5”。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。