1.二进制加法计数器

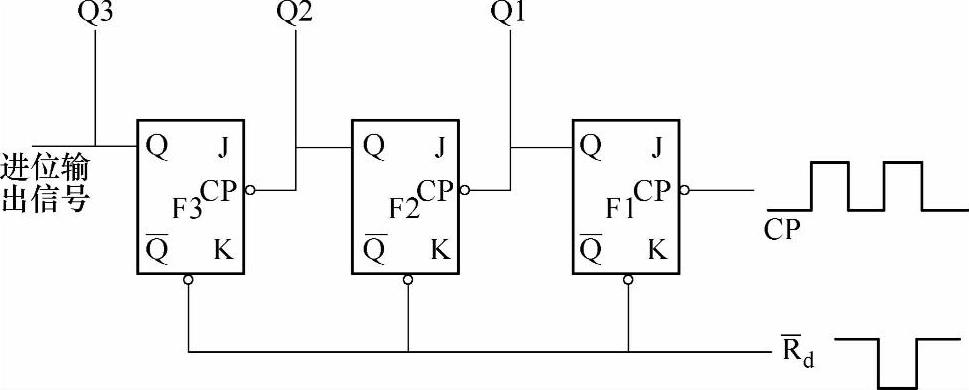

二进制数的每一位只有1和0两个数码,而一个触发器就有“1”、“0”两个状态。图8-4所示是用三个主从J-K触发器组成的一个三位二进制加法计数器的逻辑图。用n个触发器就可以表示一个n位的二进制数。

图8-4 三位二进制加法计数器

计数器的工作原理如下:

计数前,先将计数器清“0”,即在各触发器的 端加一置“0”负脉冲,使F1~F3全部处于“0”态,Q3Q2Q1为000。

端加一置“0”负脉冲,使F1~F3全部处于“0”态,Q3Q2Q1为000。

计数脉冲CP加到最低位触发器F1的CP输入端,F1的输出端接至下一高位F2的CP输入端……依此类推,可构成下降沿触发翻转的三位二进制计数逻辑电路。由主从J-K触发器的逻辑功能得知,在J=K=1的情况下,当计数脉冲CP信号产生负跳变时,F1状态就改变一次。由于Q1作为触发器F2的时钟脉冲,则每当Q1发生负跳变时,F2状态就改变一次;Q2又作为时钟脉冲驱动触发器F3。如此进行下去,图8-4所示电路就可以实现二进制加法计数。各触发器的计数状态如图8-5所示。

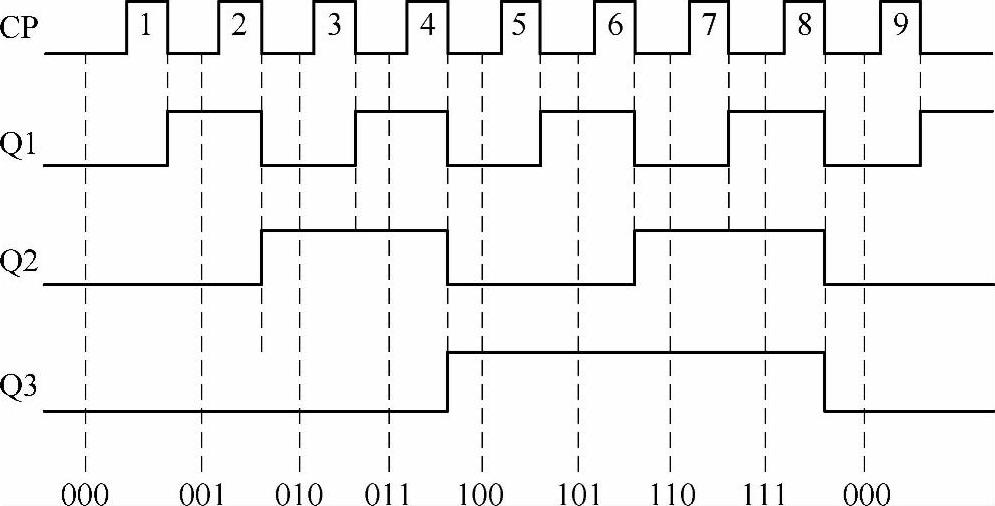

图8-5 三位二进制减法计数器时序图

分析状态时序图可知,当第一个计数脉冲作用后,三个触发器F3F2F1的状态由000变为001;第二个计数脉冲作用后,各触发器状态由001变为010;……;当第七个计数脉冲作用后,F3F2F1状态为111;当第八个计数脉冲作用后,F3F2F1状态变为000。这就是说,三个触发器组成的计数器,最多可记忆7个计数脉冲。若需记忆2n-1个计数脉冲,则需要串联n个触发器来构成2n进制计数器。计数器不仅能记忆输入脉冲的数目,还具有分频功能。因为三个触发器的输出脉冲Q1、Q2和Q3的频率,分别是计数脉冲CP频率的1/2、1/4和1/8,因此称之为二分频、四分频和八分频。

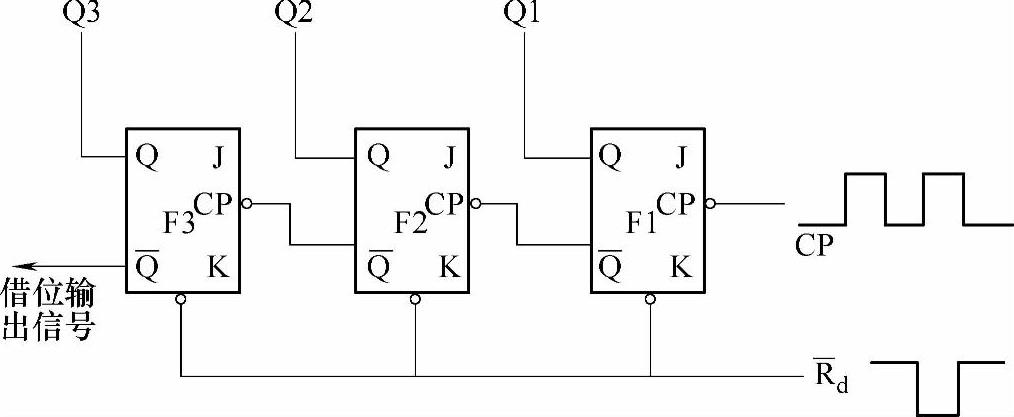

2.二进制减法计数器

图8-6所示是用主从J-K触发器组成的二进制减法计数器的逻辑图。它与图8-4不同的是低位触发器 端联接到高位触发器的CP端。

端联接到高位触发器的CP端。

减法计数过程简述如下:

计数前先清“0”,使F3F2F1状态为000。当第一个计数脉冲CP的下降沿到来时,F1由“0”变为“1”, 由“1”变“0”,这个负跳变使触发器F2由“0”变为“1”,

由“1”变“0”,这个负跳变使触发器F2由“0”变为“1”, 由“1”变为“0”,使触发器F3由“0”变为“1”,这时计数器状态为111;当第二个计数脉冲的下降沿到来时,F1由“1”变为“0”,而

由“1”变为“0”,使触发器F3由“0”变为“1”,这时计数器状态为111;当第二个计数脉冲的下降沿到来时,F1由“1”变为“0”,而 由“0”变为“1”,产生一正跳变,它对F2无影响,计数器状态为110,……。如此进行下去,每输入一个CP,计数器自动减一,计数器的计数状态见表8-4。

由“0”变为“1”,产生一正跳变,它对F2无影响,计数器状态为110,……。如此进行下去,每输入一个CP,计数器自动减一,计数器的计数状态见表8-4。

(https://www.xing528.com)

(https://www.xing528.com)

图8-6 三位二进制减法计数器

表8-4 二进制减法计数器状态表

3.十进制计数器

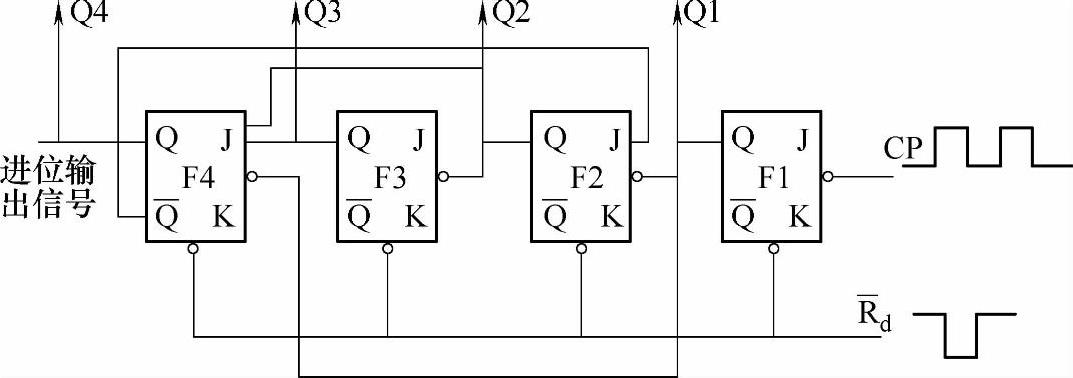

图8-7所示为用主从J-K触发器组成的8421BCD码十进制计数器的逻辑图。该电路是在四位二进制计数器基础上,令其跳过六个状态来实现十进制计数的。

图8-7 8421BCD码十进制计数器逻辑图

计数前先清0。在1~5个计数脉冲期间,计数原理与二进制计数器相同,且在此期间,Q2和Q3中总有一个为0,则F4的J端有0输入,在CP的下降沿,F4为“0”。

当第六个计数脉冲下降沿到来后,Q1由“1”变“0”,这个负跳变,使Q2由“0”变“1”,Q2的正跳变对F3无影响,这时计数器为0110状态。

第七个计数脉冲下降沿到来后,Q1由“0”变“1”,此正跳变对其他各触发器均无影响,此时计数器呈0111状态。

第八个计数脉冲下降沿到来后,F1由“1”变“0”,此负跳变使F2由“1”变“0”,Q2的负跳变又使F3由“1”变“0”,同时由于第七个计数脉冲已使F4的J端输入为1,故Q1的负跳变也使F4翻转,Q4由“0”变“1”,这时计数器变成1000状态。

第九个计数脉冲使F1翻转,Q1由“0”变“1”,Q1的正跳变对触发器无影响,计数器为1001状态。

第十个计数脉冲输入后,F1翻转,Q1由“1”变“0”,送给F2、F4的CP端一个负跳变,F2因J端有0输入,维持“0”状态不变;F4因K4=1、J4=0而翻转为“0”状态,这样计数器由1001回到0000状态,同时向高位输送一进位信号,实现了一位二-十进制的计数。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。