1.最简单的TTL与非门

(1)电路结构 如图7-20所示,它是由多发射极晶体管V1与电阻R1串联组成的与门电路和由电阻R2与晶体管V2构成的非门电路所组成。图中e1A~e1D为多发射极晶体管V1的发射极,b1为基极,每一个发射极和基极之间都有一个PN结,基极和集电极之间也有一个PN结,用等效二极管来表示其PN结电路,如图7-21所示。

(2)工作原理 当与非门的输入端全是高电平(3.6V左右)时,V1的四个发射结都处于反向偏置。因为若不是反向偏置,则b1点的电位就一定应高于3.6V,这时V1的集电结和V2的发射结必然导通,从而将b1点的电位钳制在1.4V。因此,当输入端全为高电平时,V1的四个发射结必定反向偏置,此时电流由Ec流经R1、C1到V2的基极,使V2导通。适当地选择R1和R2的阻值,即可使V2处于饱和状态,与非门输出为低电平(0.3V左右)。当输入端有一个或几个为低电平(0.3V左右)时,b1的电位被钳位在1V(0.3V+UbeD),V2截止,输出为高电平,约等于电源电压Ec。

图7-20 最简单的TTL与非门

图7-21 用等效二极管表示多发射极晶体管的PN结

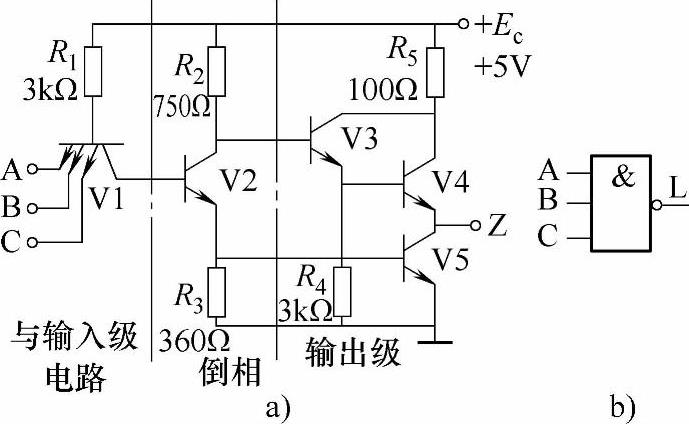

2.典型的TTL与非门

(1)电路结构 如图7-22所示,该电路由五只晶体管组成,整个电路分为与门级、分相级和输出级三部分。

1)与门级。由多发射极晶体管V1和R1组成,完成与逻辑功能,当V2由导通转为截止时,V2基区储存电荷可经V1的集电极、发射极向低电位输入端放电,使V2很快截止。

2)分相级。由V2和R2、R3组成。这一级的作用是从V2的发射极和集电极同时得到两个相位相反的信号,作为V3和V5的驱动信号。

图7-22 典型的TTL与非门(https://www.xing528.com)

a)电路 b)逻辑符号

3)输出级。由V3、V4、V5和R4、R5组成。其中V3和V4组成复合管作为V5的有源负载。V5为反相器,完成逻辑非的作用。V3、V4和V5推拉工作,在V4和V5中,总有一个导通,不论哪个导通,其输出阻抗都很低。因为V3、V4构成射极输出电路,而V5又处于深度饱和,输出阻抗也很低。因此,TTL电路无论是输出高电平还是输出低电平,都具有很低的输出电阻,所以它的带负载能力大大提高。

(2)工作原理

1)当输入端有低电平(0.3V)时,V1基极电位被钳制在0.3V+0.7V=1V左右,所以V2、V5处于截止状态。又由于V2截止,其集电极电位接近于电源电压Ec,所以V3、V4都导通,输出端Z输出为高电平3.6V。

UZ=Ec-Ib3R2-Ube3-Ube4

因为Ib3很小,可以忽略不计。当Ec=+5V时,Uz=5V-0.7V-0.7V=3.6V。由于V5截止,当接上负载后,有电流从电源经R5流向每个负载门,这种电流称为拉电流。

2)当输入端全为高电平(3.6V)时,V1基极电位被钳制在0.7V+0.7V+0.7V=2.1V,V1的三个发射结都处于反向偏置而截止。这时V1处于“倒置”状态(即原来的发射结与集电结调换使用)。V1的基极电流Ib1全部流入V2基极,使V2、V5饱和导通,所以V2的集电极电位为

Uc2=Ubes-Uce2=0.7V+0.3V=1V

此点电位即为V3的基极电位,所以V3可以导通,V3发射极电位为

Ue3=Ub3-Ube3=1V-0.7V=0.3V

此点电位即为V4的基极电位,而V4的发射极电位Ue4(即Uc5)也约为0.3V,所以V4截止。在输出端接负载后,V5的集电极电流全部由外接负载灌入,这种电流称为灌电流。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。