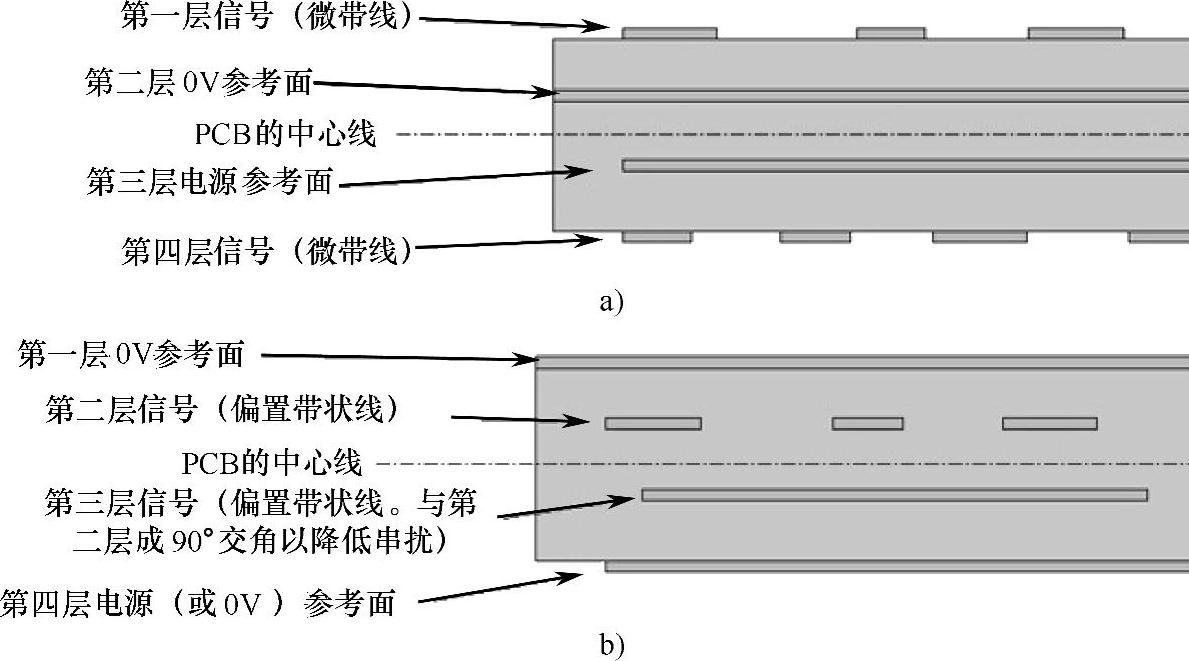

在20世纪80年代,四层PCB是相当现代化的大多数商业化产品的技术水平,并且一直延续到90年代,它都能提供和满足恰当的EMC性能要求。至今,四层PCB仍然至少能够为150μm技术出现以前的,并为遵循IC设计原则设计的数字器件产品提供合理的EMC性能(当然,这里是以精心设计的产品为前提的)。图2-6-3a显示了一个典型的等间距的80年代的四层PCB。该种结构的嵌入0V/电源参考面对的分布电容为去耦合提供了某种程度的得益。

图2-6-3 一个传统的四层PCB的横截面图及一个平面处在外面的传统四层PCB的横截面图

a)传统的四层PCB的横截面图 b)平面处在外层的传统四层PCB的横截面图

有些设计工程师推荐把两个外部层面设计为两个平面,而把两个内部层次保留用于信号线条。这一点已在图2-6-3b显示说明。这种设计构思的出发点是要对线条进行屏蔽。但即使在PCB的周边使用通孔或去耦壁(事实上,通常都会这么做),在元器件安装面上钻有许多带焊盘的元器件用插针孔,因此实际上它们无法提供高效屏蔽。

当然在使用精心设计(和仔细安排通孔或去耦壁)的情况下,是可以获得某种程度的有用屏蔽的。但这样做还必须与在使用0V和电源参考面时所存在下述事实之间取得某种折中:那就是由于它们之间分隔得如此远,以致它们不再能通过分布电容提供任何明显的去耦效果。所以,这个结果是否会优于具有嵌入平面的层叠板结构更好,还需要通过结合使用电路模拟器和场求解器(程序)进行预测来决定。

存在这个外部平面叠层的另一个问题是,在研制期间的原型板上用人工调整线条的各种参数的确是一件很困难的事。有些公司会使用一个嵌入平面对来制作所有它们的原型PCB。一旦在研制全部完成后(希望如此!),在正式产品板上再把它们移到外部平面。但这种叠层的改变不仅会对PCB的EMC性能产品产生重大影响、改变线条的特性阻抗,而且使得所做的没有更进一步改变的要求这一假定更是具有相当的风险性。

图2-6-3a和图2-6-3b所示的传统叠层采用的都是对称型,并且都使用等距的层间间距。(https://www.xing528.com)

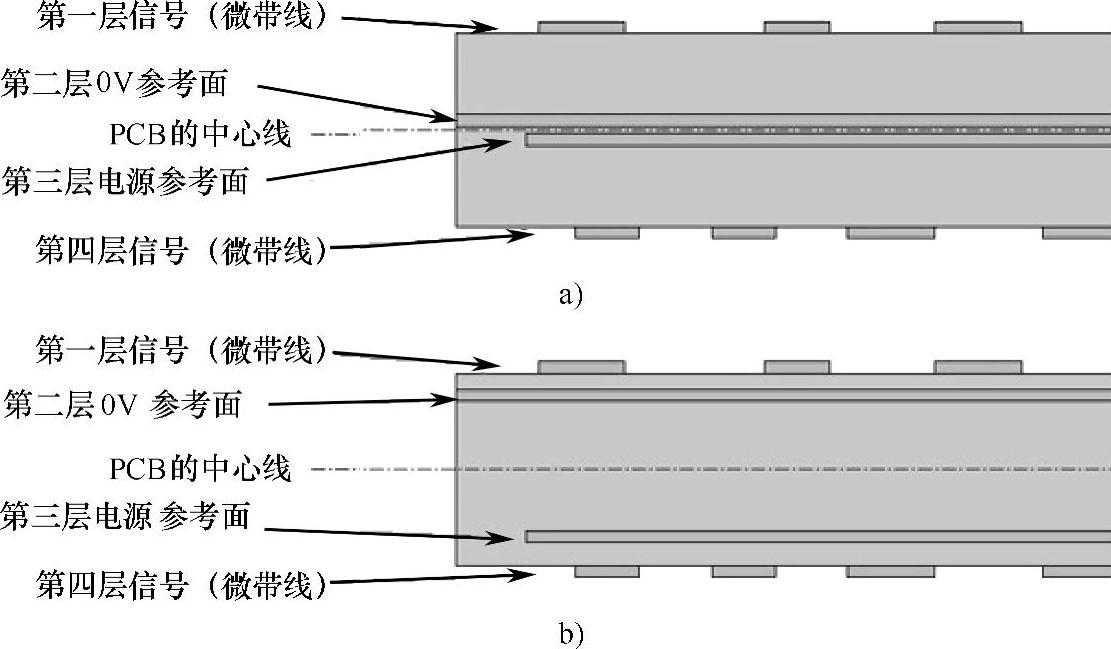

图2-6-4a中使用的是非等距层间距PCB叠层结构,以试图通过使用嵌入电容来改善去耦性能。0V/电源参考面必须沿着PCB的中心线上下对称。不然的话,很可能无法获得铜平衡和造成弯曲板。由于外部层(信号)离开它们的参考面过于远,所以它们的EMC性能也就不会那么好。

图2-6-4b所示的是Intel公司在20世纪90年代末所推荐使用的低成本主机板。它具有对称的叠层,但使用的是非等距的层间距来缩短外部层信号的线条-平面的间隔距离。因此这类板有能力处理高速数字信号,并且具有较好的信号完整性(SI)。这个叠层技术适合于安装90年代技术的数字IC和上下两个外部层面都具有高速线条的情况。但是,它们的0V和电源参考面分隔得如此之开,它们间的分布电容几乎根本没有起到什么去耦合作用。我们都已知道,良好的SI是与良好的EMC性能紧密相关的。这一点在本篇的第5章中也曾有所论及。

图2-6-4 采用嵌入电容的四层PCB横截面图及1999年Intel公司推荐采用的低成本四层PC主机板

a)四层PCB横截面图 b)低成本四层PC主机板

值得我们注意的是,在20世纪90年末使用的典型台式PC的机箱可以在30MHz频率上获得50dB的屏蔽效果。但是当频率上升到1GHz时,它的屏蔽效果已下降至仅为15~30dB之间。因此,假如没有这样一个屏蔽罩壳作为机箱,四层结构很可能无法符合FCC或EU的EMC指令要求。

还有一点值得我们注意的是,在20世纪90年代末,基于PC技术的高性能伺服器和工作站已经开始使用八层或更多叠层的PCB和屏蔽的机箱。有报道指出,在相同操作系统和应用软件的情况下,伺服器和工作站所经历的视窗故障率要比普通PC低得多。这也许就是因为四层板的信号完整性不是那么好的缘故吧。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。