在前面已经提到过,在一个差分对中线条布线对称的重要性。并且我们也知道,差分线中两根线条的布线方式不同将会改变每根线条可能存在的杂散电容和电感。不论是杂散电容还是电感的不同又都会引起差分对的失衡。况且,差分对中的每根线条与它邻近的平面(或多个平面)以及其他线条的耦合所引起的布线不对称又会改变与该差分传输线有关的DM Z0和CM Z0的比例。

有时我们也推荐采用加宽或减薄其中的一根线条来补偿线条中出现的误差。但这只能对两个Z0中的一个进行。在差分对以足够靠近的紧耦合方式布线时,尽管我们也知道是非对称布线,我们也无法采用类似于补偿的这类小技巧来同时保持DM Z0和CM Z0的恒定。

为了获得最佳的EMC性能,最好的办法就是沿着差分对的整个布线长度上,以紧耦合、完全对称的方式走线。并且,还要求以它们至少有一个端头终止于DM Z0和CM Z0(当然,两个端头则更好)。在使用LVDS技术时,倘若使用的LVDS接收器的类型可以接收宽范围的输入电平时,则有可能在PCB上采用经典的终端法(终止于两个端头)。

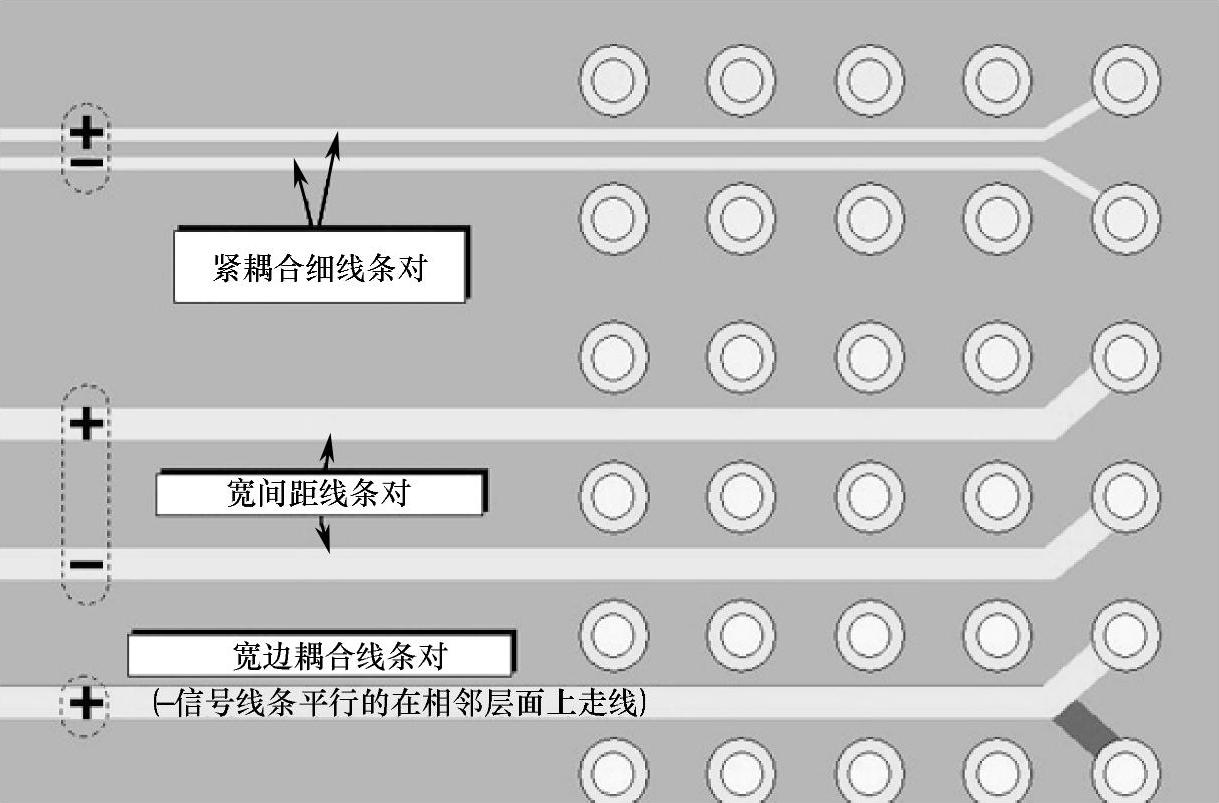

但在工程实践中,对称布线往往会遇到一些困难。特别是在一个通孔或焊盘区域的周围。比如,一个BGA器件或者在一个连接器插针下面就是这样一个多通孔或焊盘的区域。理想情况是将每个对称的差分对在布线障碍之间走线,并且在相邻层面上有足够平面宽度以对称的方式位于差分对下面来携载它们的返回电流。图2-5-31所示的理想情况可以通过在满足它们所要求条件下,使用尽可能小的线条宽度和平面间隔来获得。因为,这样做可以为它们以对称方式走线提供所需要的焊盘和通孔间隔。但是,在正常情况下,若低成本产品无法满上述对线条本身和它们的间隔所要求的条件时(在撰写此书时为18nm,或7‰in),商业上成本的增加也许无法接受。那么,就需要寻找另外其他替代办法。

图2-5-31 在高密集度通孔区域中保持线条对的对称性(https://www.xing528.com)

一个办法是简单地把有用信号波形(和不希望的噪声)的上升和下降沿减慢至由非对称所引起的非连续可以忽略不计的程度(作为例子,请参阅前面的图2-5-5)。但是,在使用高数据率或高频率的场合,试图用这个方法来达到所要求的电路功能很可能是不切实际的。

有时建议采用的另一个办法是,把差分对的间距拉开以使它们之间不会形成明显的耦合(在这个情况下,CM的Z0简单的就是DM Z0的两倍)。然后,把它们按照单根线条方式穿越通孔和焊盘区域(请参阅图2-5-31中部的一对线条)。当使用这个方法于高速或高频信号(或噪声)时,关键的是使两根线条的布线方式完全相同。并以此来确保差分线的平衡。

在线条间距足够靠近而形成耦合(即,它们的CM Z0小于它们的DM Z0的两倍)时,把两根线条在遇到一个通孔或一个焊盘时分开走线也是可能的。这在文献线对分离一文中有所描述。但是,正如前面已提到过的,要对这种做法所形成的DM Z0和CM Z0进行补偿是相当困难的。

一般地说,差分对的宽面布线并不是一个好的办法(请参阅文献在宽面设置的非对称性一文的讨论)。但还是如图2-5-31所示,这样做至少允许在通孔或焊盘区域间允许一根线条通过的同时,仍保持差分对两根线条间的原有关系。因此,就其结果来说,这种做法也许并不是可供选择的最坏办法。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。